## UNIVERSITÀ DEGLI STUDI DI PAVIA

Department of Electrical, Computer and Biomedical Engineering

Ph.D. School in Microelectronics XXXI Cycle

#### Design, Modeling and Characterization of Circuits and Devices for Emerging Memories

Ph.D. Thesis of Yilkal Andualem Belay

#### **Supervisors:**

Prof. Guido Torelli

Prof. Alessandro Cabrini

**Coordinator:**

Prof. Guido Torelli

#### Abstract

Novel data storage device concepts and high density architectures have been under exploration to meet the memory performance and storage capacity demand, which is growing exponentially and becoming challenging to be met by the mainstream memory technologies. Scaling down to advanced technology nodes is needed for increasing storage capacity and area efficiency. However, the mainstream memories namely, Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), and Flash memory are facing issues such as, reliability degradation and increasing leakage power.

As a result, emerging memory technologies such as Resistive Random Access Memory (RRAM), Phase Change Memory (PCM), and Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) are under research and development due to their promising scalability, reduced standby power, access speed, and other interesting features. They are expected not only to replace the mainstream memories but also to create new memory markets for instance, a Storage Class Memory (SCM) that combines a storage capacity comparable to that of NAND Flash memory and speed comparable to that of DRAM. The predominant emerging memories are based on resistance switching principle: the resistance of the storage device is switched between a high-resistance state (HRS) and a low-resistance state (LRS), which are used to store binary data. In addition, high density storage solutions such as multi-level cell (multiple bits in a single cell), 3D integration, and crosspoint arrays are under exploration to meet the high storage capacity demand. For instance, in crosspoint arrays, memory cells are built at the junctions of a lower and an upper plane of parallel metal lines running at right angles to each other, and hence if both the width of the metal lines and the spacing between them is equal to the minimum lithographic feature size, F, the memory cell can be allocated within the smallest footprint of  $2F \times 2F$ .

This thesis presents a model-based study of STT-MRAM cell, array and sensing circuits, an experimental electrical characterization of two (types of) RRAM device stacks, and a detail analysis of the design considerations for write and read operations and device technology requirements in crosspoint memory arrays. With respect to STT-MRAM, the thesis mainly contributes a comprehensive behavioral model of STT-MRAM cell for circuit simulations and review and analysis of sensing circuit schemes for conventional and crosspoint STT-MRAM arrays. The performance (i.e., sense margin) of various sensing circuit schemes are analyzed by taking into account the impact of cell-to-cell variations and parasitics in bitlines, BLs, and wordlines, WLs.

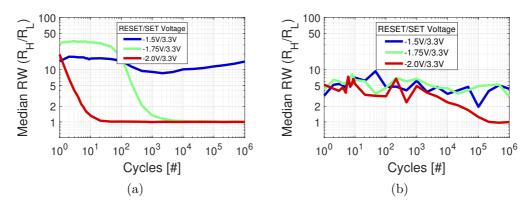

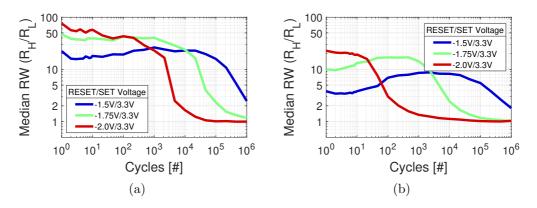

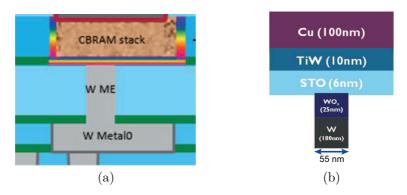

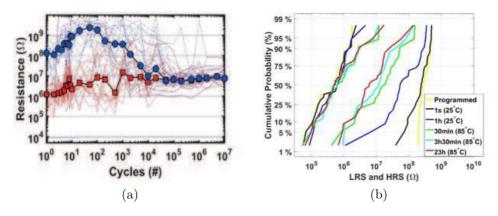

As for RRAM, a detailed array-level experimental electrical characterization of OxRAM (Oxide RAM) with TiN/Hf/GdAlO/TiN device stack and and device-level reliability study of CBRAM (Conductive Bridging RAM) with Cu/TiW/SrTiOx/WOx/W stack are presented. The characterization of the OxRAM stack focuses on analyzing operating voltages and cyclic endurance at array level, with the prospect of tuning the performance for embedded and storage class memory applications. The impacts of the thickness of the GdAlO layer and device size on operating voltages and endurance are discussed. On CBRAM, the experimental tests, which the results are presented in this thesis, were aimed at studying the Cu/TiW/SrTiOx/WOx/W stack and to optimizing the operating voltages and currents to obtain optimum memory performance and reliability.

Finally, this thesis presents a comprehensive study on design considerations for write and read operations and device technology requirements of 1S1R (one-selector one-resistor) crosspoint memory arrays. Indeed, crosspoint memory arrays has gained much attention as an architecture to obtain high-density storage. However, the successful implementation of large-size crosspoint arrays is hindered by some issues that need to be addressed. The most critical issue is that when we activate certain memory cell(s) many other cells that are not intended to be written/read will be partially activated resulting in sneak current paths, which lead to excessive leakage power consumption and write and read performance degradation. To solve this issue, the memory cell should have a strongly nonlinear current-voltage (I-V) characteristic, i.e. it should turn off at low bias voltages and turn on at adequately larger bias. One of the approaches for introducing nonlinearity is by integrating a two-terminal nonlinear selector device in series with each memory element, thus giving rise to an 1S1R configuration. By using analytical and circuit models, the thesis analyzes the dependence of 1S1R crosspoint memory array performance on the characteristics of selector device (nonlinearity and operating voltage), memory element (ratio of resistance of HRS to that of LRS, switching current and voltage) and interconnection metal line (parasitic resistance).

## Acknowledgements

First of all, I would like to express my special thanks to my supervisors Professor Guido Torelli and Professor Alessandro Cabrini for the guidance and encouragement throughout my research. Without your support and guidance, completing this work would have been unthinkable. I would also like to extend my gratitude to fellow members of my research team Dr. Riccardo Zurla and Flavio Giovanni Volpe, for their feedback, cooperation and friendship.

My next gratitude goes to Dr. Andrea Fantini, who was my mentor when I was in imec (Leuven, Belgium) for six months research internship. Thank you for your very generous supervision and experience sharing, and also for familiarizing me not only with the experimental procedures of the labs but also with everything in the work environment of imec. I also worked with Dr. Attilio Belmonte during my last two months at imec. I want to say thank you for giving me the opportunity to work with you and for making me learn a lot in this brief time. My gratitude also goes to Ludovic Goux, manager of memory device design group, and Gouri Sankar Kar, Program Director of emerging memories at imec, for giving me the opportunity to join the research team.

Last but not least, I would like to say thank you to my parents, sisters and brothers for their love support. My friends, Moses, Awet, Beza, Meseret and residents of Collegio Spallanzani, thank you for all the good moments.

## Contents

| Co | onten | nts                                                    | iv   |

|----|-------|--------------------------------------------------------|------|

| Li | st of | Figures                                                | viii |

| Li | st of | Tables                                                 | ix   |

| 1  | Intr  | oduction                                               | 1    |

|    | 1.1   | General Overview                                       | 1    |

|    | 1.2   | The Memory Sub-System                                  | 3    |

|    |       | 1.2.1 Memory Hierarchy                                 |      |

|    | 1.3   | Mainstream Solid-State Memories                        | 5    |

|    |       | 1.3.1 Static Random Access Memory (SRAM)               | 5    |

|    |       | 1.3.2 Dynamic Random Access Memory (DRAM)              | 6    |

|    |       | 1.3.3 Flash Nonvolatile Memory                         | 7    |

|    | 1.4   | Challenges of Mainstream Memories and Current Research |      |

|    |       | and Development Trends                                 | 9    |

|    | 1.5   | Objectives of the Thesis                               | 11   |

|    | 1.6   | Organization of the Thesis                             | 12   |

| 2  | Spin  | n-Transfer Torque Magnetic RAM (STT-MRAM)              | 14   |

|    | 2.1   | Overview                                               |      |

|    | 2.2   | Key Technology Advances and Challenges of STT-MRAM $$  | 15   |

|    | 2.3   | Basic Physics of STT-MRAM                              |      |

|    |       | 2.3.1 Principle of Operation                           | 17   |

|    |       | 2.3.2 Switching Current                                |      |

|    |       | 2.3.3 Probability of Switching                         | 21   |

|    |       | 2.3.4 Static Behavior of STT-MRAM Cell                 |      |

|    | 2.4   | Model of STT-MRAM                                      | 22   |

|    | 2.5   | Sensing Circuits for STT-MRAM                          |      |

|    |       | 2.5.1 Conventional Sensing Scheme                      |      |

|    |       | 2.5.2 Non-destructive Self-Reference Sensing Scheme    | 28   |

|   |      | <ul><li>2.5.4 Slope Detection Self-Reference Sensing Scheme</li><li>2.5.5 Variation-Aware Analysis of Sensing Margin in Slope</li></ul> | 29<br>30<br>32 |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 2.6  | 9                                                                                                                                       | 36             |

| 3 | Elec | trical Characterization of Resistive Memories                                                                                           | 38             |

|   | 3.1  |                                                                                                                                         | 38             |

|   | 3.2  |                                                                                                                                         | 36             |

|   | 3.3  | Electrical Characterization of GdAlO-Based OxRAM                                                                                        | 41             |

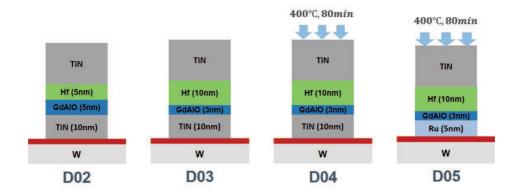

|   |      | 3.3.1 OxRAM Device Stacks and Experimental Setup                                                                                        | 41             |

|   |      | 3.3.2 Forming                                                                                                                           | 43             |

|   |      | 3.3.3 RESET Voltage                                                                                                                     | 46             |

|   |      | 3.3.4 SET Voltage                                                                                                                       | 47             |

|   |      | 3.3.5 Cyclic Endurance                                                                                                                  | 48             |

|   | 3.4  | Electrical Characterization of $SrTiO_3$ -Based CBRAM                                                                                   | 51             |

|   |      | 1                                                                                                                                       | 51             |

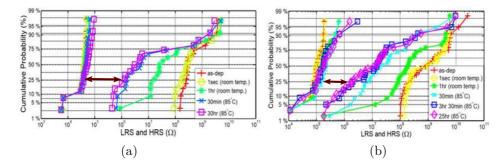

|   |      | 3.4.2 Memory Window, Endurance and Retention                                                                                            | 52             |

|   | 3.5  | Conclusion and Outlook                                                                                                                  | 54             |

| 4 | Cro  | sspoint Memory Arrays for High-Density Storage                                                                                          | 56             |

|   | 4.1  | Overview of Crosspoint Memory Arrays                                                                                                    | 56             |

|   | 4.2  | Challenges of Crosspoint Memory Arrays                                                                                                  | 58             |

|   | 4.3  | Selector Devices for Crosspoint Memory Arrays                                                                                           | 61             |

|   |      | <u>*</u>                                                                                                                                | 61             |

|   |      | ~                                                                                                                                       | 63             |

|   |      | 4.3.3 Model of Selector Device                                                                                                          | 64             |

|   | 4.4  | ŭ v                                                                                                                                     | 66             |

|   | 4.5  | e e e e e e e e e e e e e e e e e e e                                                                                                   | 68             |

|   | 4.6  | - ,                                                                                                                                     | 69             |

|   | 4.7  | Design considerations for Write Operation in Crosspoint Arrays                                                                          | 71             |

|   |      | 4.7.1 Simplified Analysis of Boundary Conditions                                                                                        | 71             |

|   |      | 4.7.2 Write Requirements in Practical-Size Arrays                                                                                       | 73             |

|   | 4.8  | Design considerations for Read Operation in Crosspoint Arrays                                                                           | 81             |

|   | 4.9  | A Variability-Aware Analysis of the Voltage Compatibility of                                                                            |                |

|   |      | v                                                                                                                                       | 83             |

|   | 4.10 | U I V V                                                                                                                                 | 90             |

|   |      | 0                                                                                                                                       | 91             |

|   |      | <u> </u>                                                                                                                                | 92             |

|   | 4.11 | Conclusion                                                                                                                              | 94             |

| 5 | Ger | eral Conclusions and Future Prospects | 96 |

|---|-----|---------------------------------------|----|

|   | 5.1 | Conclusions                           | 96 |

|   | 5.2 | Future Prospects                      | 98 |

## List of Figures

| 1.1  | Memory array organization                                                                                                            | 4  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Physical distribution and hierarchy of memory in a computer .                                                                        | 4  |

| 1.3  | Static RAM operation                                                                                                                 | 5  |

| 1.4  | 6-Transistor SRAM cell                                                                                                               | 6  |

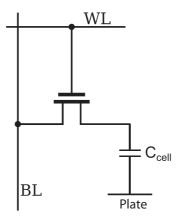

| 1.5  | 1-Transistor DRAM cell                                                                                                               | 6  |

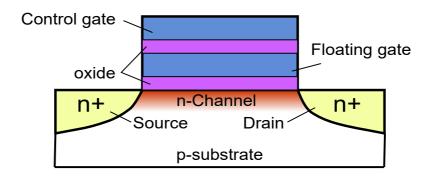

| 1.6  | Floating gate flash memory cell                                                                                                      | 7  |

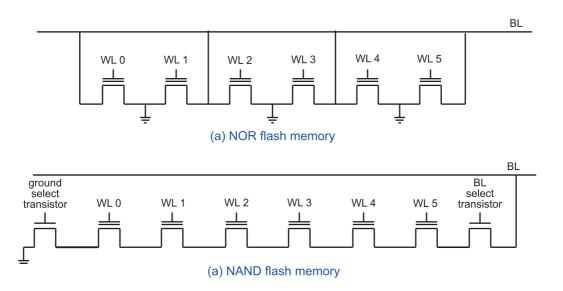

| 1.7  | Flash memory: (a) NOR (b) NAND                                                                                                       | 8  |

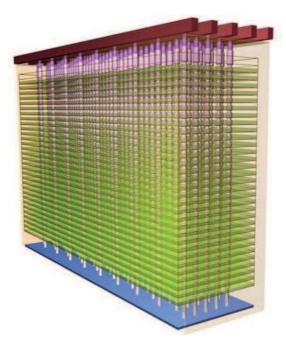

| 1.8  | 32-layer 3D NAND Flash memory                                                                                                        | 10 |

| 2.1  | STT-MRAM cell with a MOS transistor as a selector                                                                                    | 17 |

| 2.2  | STT switching (a) antiparallel to parallel switching (b) parallel                                                                    |    |

|      | to antiparallel switching                                                                                                            | 19 |

| 2.3  | Block diagram of the proposed STT-MRAM Verilog-A model .                                                                             | 23 |

| 2.4  | R-I characteristic: asymmetrical (dashed line) switching cur-                                                                        |    |

|      | rents for the AP $\rightarrow$ P and P $\rightarrow$ AP transitions; symmetrical                                                     |    |

|      | switching (solid line)                                                                                                               | 25 |

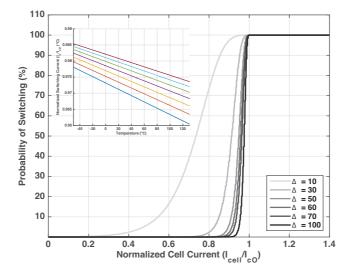

| 2.5  | Switching probability for different values of the thermal stability factor $\Delta$ . The inset shows variation of switching current |    |

|      | with temperature                                                                                                                     | 25 |

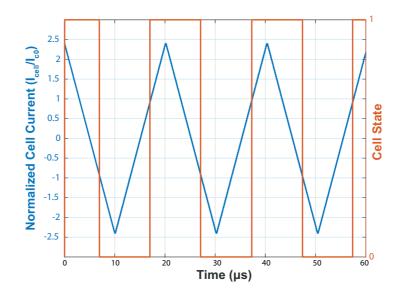

| 2.6  | Simulated switching characteristic of STT-MRAM cell: normalized write current (blue, left y-axis) and the state of the               |    |

|      | cell (right y-axis)                                                                                                                  | 26 |

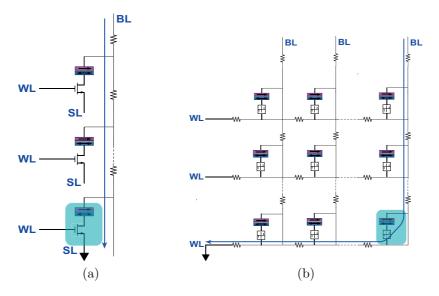

| 2.7  | Illustration of STT-MRAM arrays (a) conventional array (b)                                                                           |    |

|      | crosspoint array                                                                                                                     | 27 |

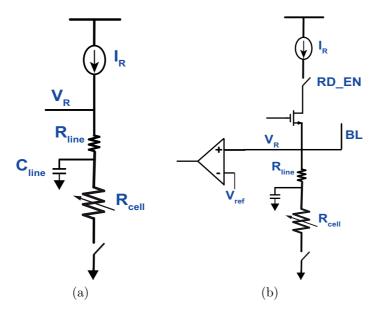

| 2.8  | Reading in STT-MRAM: (a) simplified read path model (b)                                                                              |    |

|      | conventional scheme with the simplified read path model                                                                              | 27 |

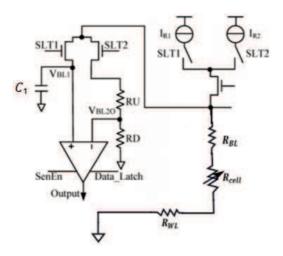

| 2.9  | Nondestructive self-reference sensing (source: [1])                                                                                  | 29 |

| 2.10 |                                                                                                                                      | 30 |

| 2.11 | Sampling in slope detection sensing                                                                                                  | 31 |

|      | Normal inverse distribution of cell resistance                                                                                       | 34 |

| 2.13 | Normal inverse distribution of sense margin for $\alpha = 0$ and                                                                     |    |

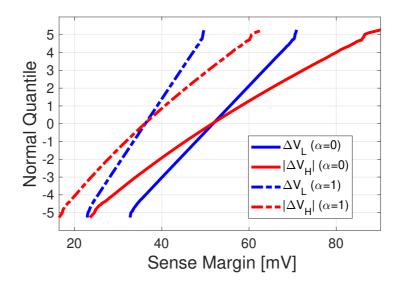

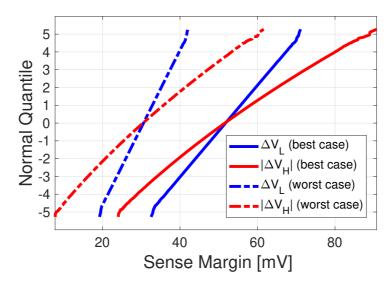

|      | $\alpha = 1 \ (R_{line} = 0) \ \dots \dots \dots \dots \dots \dots \dots$                                                            | 35 |

| 2.14 | Normal inverse distribution of sense margin for $R_{line} = 0$ and $R_{line} = 10 \text{ k}\Omega \ (\alpha = 0) \ \dots \dots \dots \dots \dots \dots \dots \dots$ . | 35 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

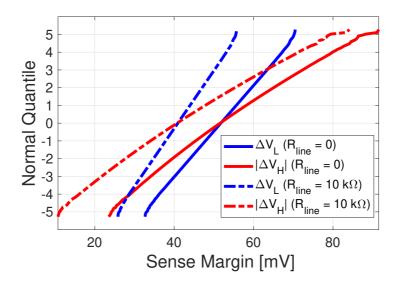

| 2.15 | Comparison of best-case and worst-case sense margins                                                                                                                  | 36 |

| 3.1  | Embedded RRAM requirements                                                                                                                                            | 39 |

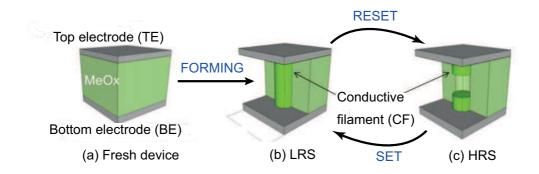

| 3.2  | RRAM device structure and filamentary switching mechanism                                                                                                             | 40 |

| 3.3  | OxRAM pillar device stack                                                                                                                                             | 41 |

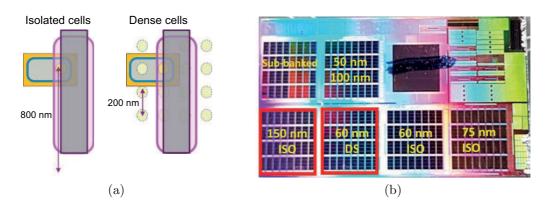

| 3.4  | (a) Isolated (ISO) and dense (DS) memory cells (b) Memory chip with different Mbit arrays                                                                             | 42 |

| 3.5  | OxRAM Memory stack implemented between Metal-3 (M3) and Metal-4 (M4)                                                                                                  | 42 |

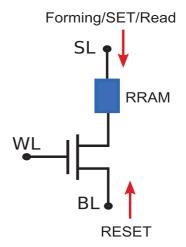

| 3.6  | Schematic view of 1T1R configuration and biasing condition                                                                                                            |    |

|      | for RESET, FORMING, SET, and read operations                                                                                                                          | 42 |

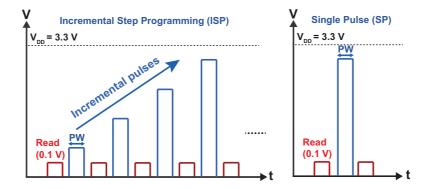

| 3.7  | Programing pulses: Incremental Single Pulse (left) and single                                                                                                         |    |

|      | Pulse programing (right)                                                                                                                                              | 43 |

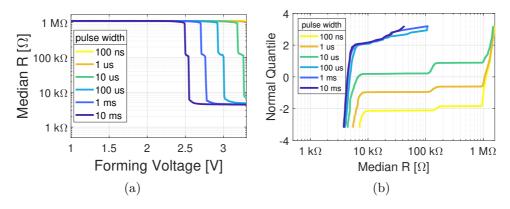

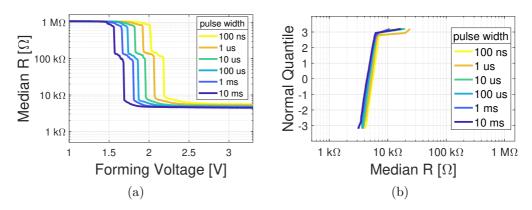

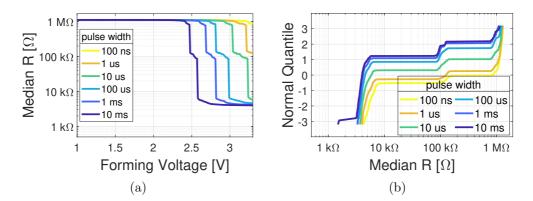

| 3.8  | Forming in D02 (5 nm GdAlO), ISO (isolated), 150 nm (cell di-                                                                                                         |    |

|      | ameter): (a) forming R-V-t plot and (b) Distribution of post-                                                                                                         |    |

|      | forming resistance                                                                                                                                                    | 44 |

| 3.9  | Forming in D02 (5 nm GdAlO), DS (dense), 60 nm (cell di-                                                                                                              |    |

| 9.0  | ameter): (a) forming R-V-t plot and (b) Distribution of post-                                                                                                         |    |

|      | forming resistance                                                                                                                                                    | 44 |

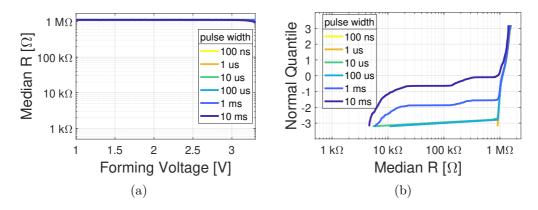

| 3.10 |                                                                                                                                                                       |    |

|      | ameter): (a) forming R-V-t plot and (b) Distribution of post-                                                                                                         |    |

|      | forming resistance                                                                                                                                                    | 45 |

| 3.11 | Forming in D03 (3 nm GdAlO), DS (dense), 60 nm (cell di-                                                                                                              |    |

| 9    | ameter): (a) forming R-V-t plot and (b) Distribution of post-                                                                                                         |    |

|      | forming resistance                                                                                                                                                    | 45 |

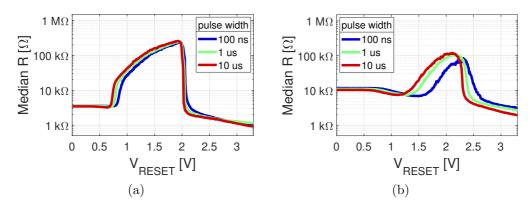

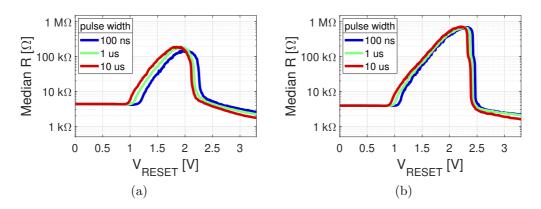

| 3.12 | RESET R-V-t in D02 (5 nm GdAlO stack): (a) Isolated, 150                                                                                                              |    |

|      | nm and (b) Dense, 60 nm                                                                                                                                               | 46 |

| 3.13 | RESET R-V-t in D03 (3 nm GdAlO): (a) Isolated 150 nm and                                                                                                              |    |

|      | (b) Dense 60 nm                                                                                                                                                       | 46 |

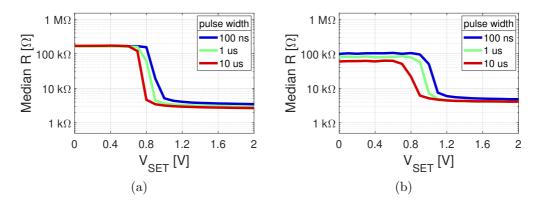

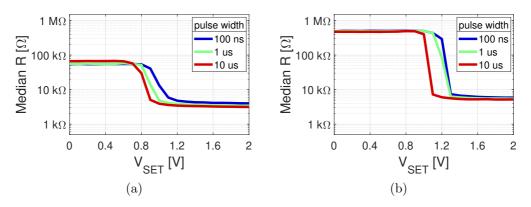

| 3.14 | SET R-V-t in D02 (5 nm GdAlO stack) plot: (a) Isolated 150                                                                                                            |    |

|      | nm cells and (b) Dense 60 nm cells                                                                                                                                    | 47 |

| 3.15 | SET R-V-t in D03 (3 nm GdAlO stack): (a) Isolated, 150 nm                                                                                                             |    |

|      | and (b) Dense, 60 nm                                                                                                                                                  | 47 |

| 3.16 | Cyclic Endurance in D02 (5 nm GdAlO) stack (150 $\mu$ A com-                                                                                                          |    |

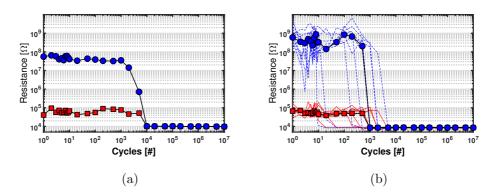

|      | pliance current): (a) Isolated 150 nm and (b) Dense 60 nm                                                                                                             | 48 |

| 3.17 | Cyclic Endurance in D03 (5 nm GdAlO) stack (150 $\mu$ A com-                                                                                                          |    |

|      | pliance current): (a) Isolated 150 nm and (b) Dense 60 nm                                                                                                             | 48 |

| 3.18 | CBRAM (a) 1T1R structure (b) STO-based CBRAM device                                                                                                                   |    |

|      | stack                                                                                                                                                                 | 51 |

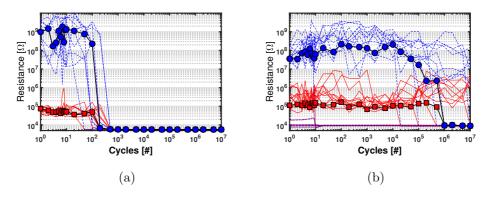

| 3.19       | Reliability of STO-based CBRAM at 10 $\mu$ A, 10 ns, $V_{SET} = 3.5 \text{ V}$ , $V_{RESET} = -3.0 \text{ V}$ : (a) cyclic endurance and (b) retention    | 52       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.20       | Comparison of endurance ( $V_{SET} = 3.5 \text{ V}$ , $V_{RESET} = -3.0 \text{ V}$ ): (a) forming and SET at 50 $\mu$ A and (b) forming at 10 $\mu$ A and |          |

| 3.21       | SET at 50 $\mu$ A                                                                                                                                         | 53       |

| 3.22       | triangular pulse (5 ns-1 ns-5 ns)                                                                                                                         | 53       |

|            | (b) triangular pulse (5ns-1ns-5ns)                                                                                                                        | 54       |

| 4.1<br>4.2 | Schematics of 3D crosspoint memory arrays                                                                                                                 | 57       |

|            | cell shown                                                                                                                                                | 59       |

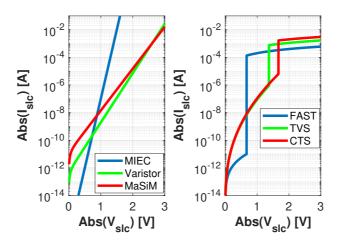

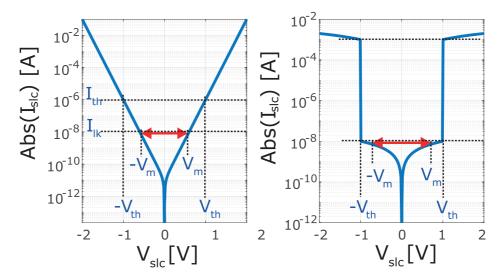

| 4.3        | Representative I-V characteristics of selector devices: expo-                                                                                             | co       |

| 4.4        | nential selectors (left) and threshold selectors (right) I-V characteristics of exponential (left)) and threshold (right)                                 | 63       |

| 1.1        | selector devices                                                                                                                                          | 64       |

| 4.5        | Typical I-V characteristics of bipolar RRAM, STTRAM, and PCM                                                                                              | 67       |

| 4.6        | Physical schematics of a $2\times2$ crosspoint array with parameters of interconnection metal lines                                                       | 68       |

| 4.7        | Simplified circuit model of a crosspoint array when programming a memory cell at the lower right corner                                                   | 70       |

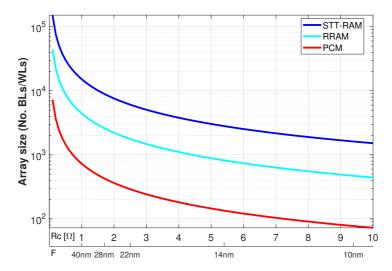

| 4.8        | Dependence of feasible crosspoint array size on low-leakage voltage margin, $V_m$ , of exponential selector device                                        | 77       |

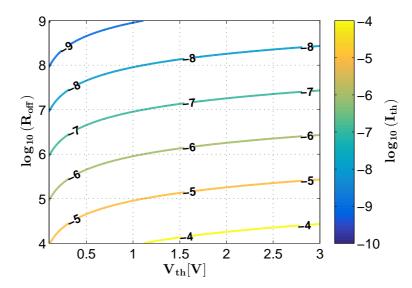

| 4.9        | Maximum feasible size of square crosspoint array built with threshold selector versus threshold voltage of selector                                       | 77       |

| 4.10       | Off-state resistance versus leakage current in threshold selector                                                                                         |          |

| 4.11       | devices                                                                                                                                                   | 78       |

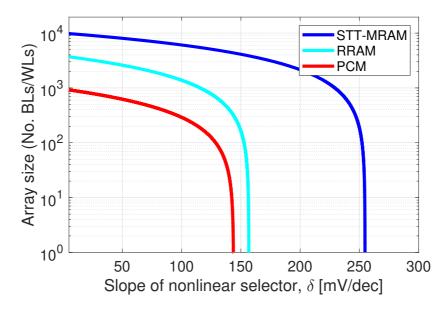

|            | selector device                                                                                                                                           | 79       |

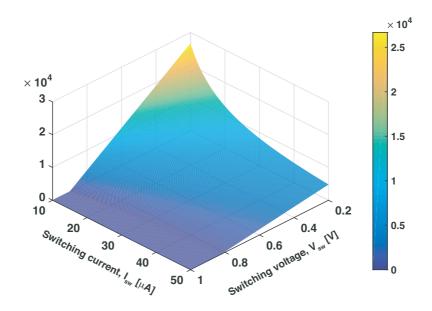

| 4.12       | Dependence of maximum array size of on $I_{sw}$ and $V_{sw}$ of mem-                                                                                      |          |

|            | ory element                                                                                                                                               | 79       |

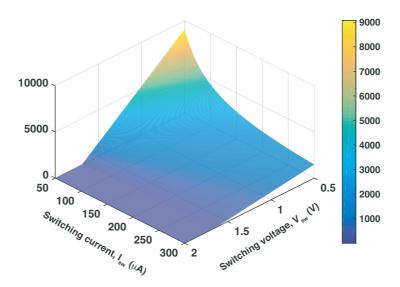

| 4.13       | Dependence of maximum array size of on $I_{sw}$ and $V_{sw}$ of the                                                                                       | 00       |

| 111        | memory element (for higher values of $I_{sw}$ and $V_{sw}$ ) Impact of interconnection metal line scaling on array size .                                 | 80<br>80 |

| 4.14       | impact of of interconnection metal line scaling on array size .                                                                                           | OU       |

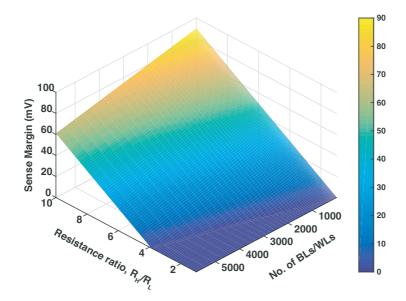

| 4.15 | Total sensing margin (using 10 $\mu$ A read current), as a function                                                                                                |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | of crosspoint array size and memory element resistance ratio,                                                                                                      |    |

|      | $rac{R_H}{R_I}$                                                                                                                                                   | 82 |

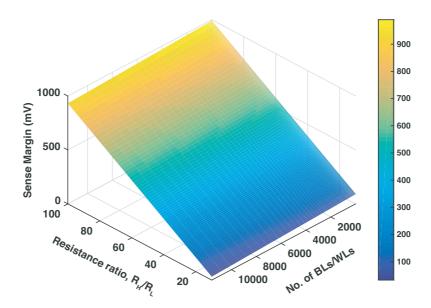

| 4.16 | Total sensing margin (using 10 $\mu$ A read current), as a function                                                                                                |    |

|      | of array size and cell state resistance ratio, $\frac{R_H}{R_I}$                                                                                                   | 83 |

| 4.17 | Circuit simulation of a crosspoint array with $256 \times 256$ memory                                                                                              |    |

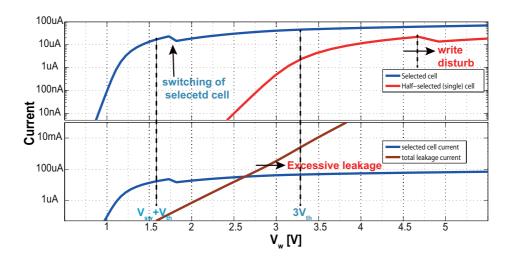

|      | $(V_{th} = 1.1 \text{ V and } V_{sw} = 0.5 \text{ V}) \dots \dots \dots \dots \dots \dots$                                                                         | 86 |

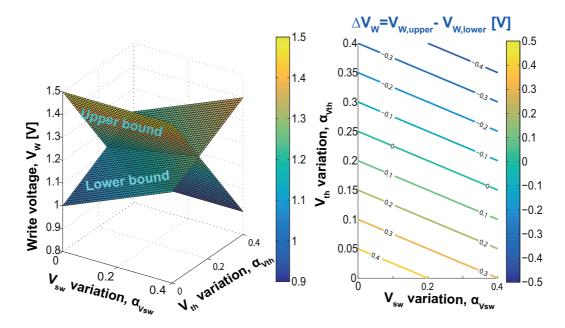

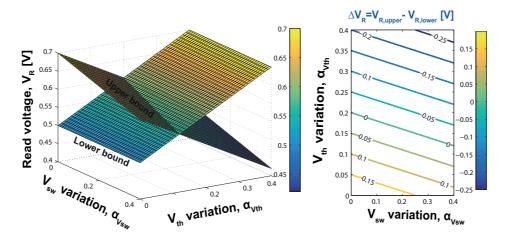

| 4.18 | Upper and lower bounds of write voltage, $V_W$ , for $V_{th} = 0.5$                                                                                                |    |

|      | V, and $V_{sw} = 0.5 \text{ V} \dots \dots \dots \dots \dots \dots$                                                                                                | 87 |

| 4.19 | Upper and lower bounds of read voltage, $V_R$ , for $V_{th} = 0.5 \text{ V}$                                                                                       |    |

|      | and $V_{sw} = 0.5 \text{ V}$ , and $\beta = 0.4 \dots \dots$ | 87 |

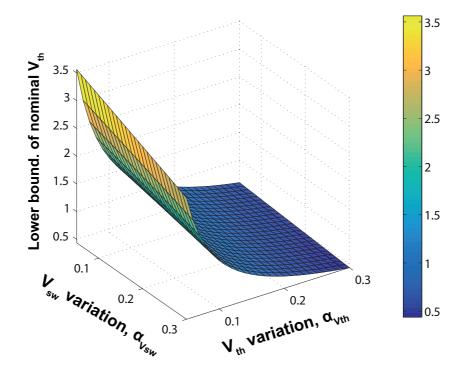

| 4.20 | Lower bound of nominal selector threshold voltage, $\overline{V}_{th}$ as a                                                                                        |    |

|      | function of different spread of parameters $\alpha_{V_{sw}}$ and $\alpha_{V_{th}}$                                                                                 | 88 |

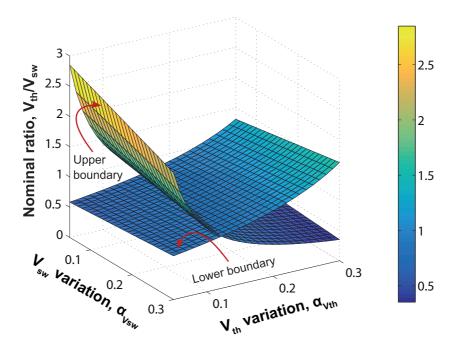

| 4.21 | Lower and upper boundaries for the ratio $V_t h/V_s w$ as a function                                                                                               |    |

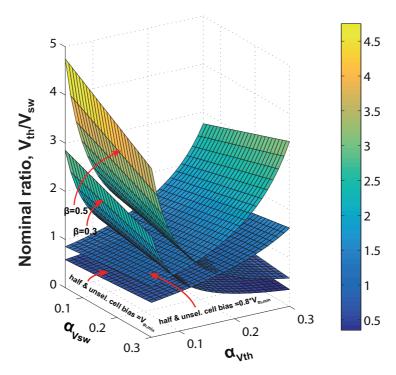

|      | of the spread parameters $\alpha_{V_{sw}}$ and $\alpha_{V_{th}}$                                                                                                   | 89 |

| 4.22 | Lower and upper boundaries for the ratio $V_t h/V_{sw}$ as a function                                                                                              |    |

|      | of the spread parameters $\alpha_{V_{sw}}$ and $\alpha_{V_{th}}$ for different cases of                                                                            |    |

|      | read and write biasing                                                                                                                                             | 90 |

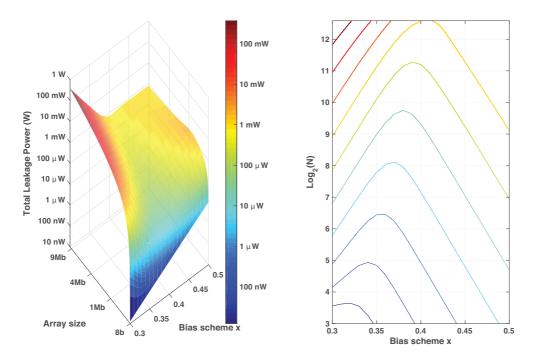

| 4.23 | Total leakage power as a function of array size and bias scheme                                                                                                    |    |

|      | (sub-threshold nonlinearity of selector = $0.2 \text{ V/decade}$ )                                                                                                 | 93 |

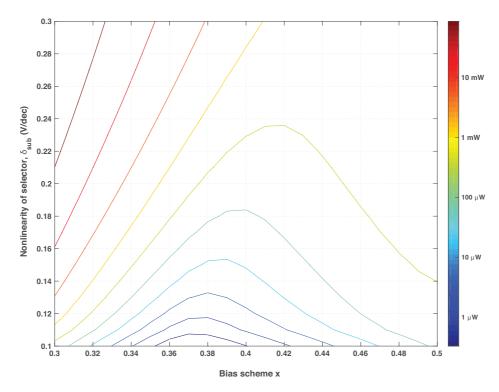

| 4.24 | Contour plot of total leakage power as a function of biasing                                                                                                       |    |

|      | scheme and nonlinearity of selector (leakage power is constant                                                                                                     |    |

|      | over each indicated contour line)                                                                                                                                  | 94 |

## List of Tables

| 2.1 | STT-MRAM Technology Parameters                                                                                             | 24 |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

|     | Summary of results: experimental electrical characterization at 150 $\mu A$ operating current (embedded memory target)     | 49 |

| 3.2 | Summary of results: experimental electrical characterization at 50 $\mu A$ operating current (storage class memory target) | 50 |

| 4.1 | Example of effective resistivity of metal lines in different technology nodes                                              | 69 |

## Chapter 1

## Introduction

#### 1.1 General Overview

Inventing better mechanisms for storing information has always been an integral part of the advancement of human civilization. The mechanisms evolved from carvings on stones and clays to markings on papyrus and parchment then to writing on modern paper, and then to the more recent electronic/digital data storage technologies. Today, memory devices that store digital data temporarily or permanently are key components of all electronic systems. Indeed, the demand for electronic storage capacity has been steadily increasing since the invention of the electronic computer and in the future, due to the expected massive number of embedded systems and Internet of Things (IoT) devices, the demand will increase at a much higher rate than ever before. It is estimated that the amount of data that needs to be processed and stored annually will reach 160 billion Terabytes by 2025, which is a 10 fold increase from the 16 billion Terabytes data generated in 2016 [2].

Moreover, since the memory subsystem inside today's electronic systems serves diversified functions, the functionality and performance of electronic systems are increasingly becoming dependent on the performance of the memory subsystems. In today's microprocessors, the memory subsystem has a strongly hierarchical organization, which mostly integrates the mainstream memory technologies namely, Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), and NAND Flash memory that serve as cache memory, main memory and secondary storage, respectively. However, with the evolution of fast microprocessors, there is an increasing performance disparity between the microprocessors and the memory subsystems.

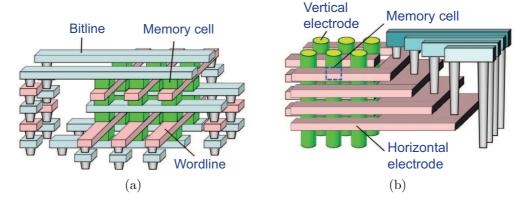

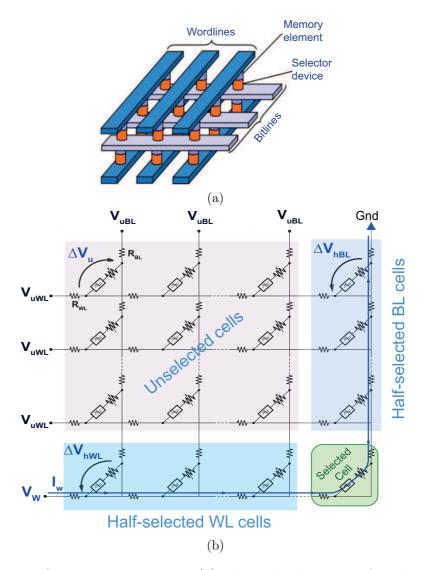

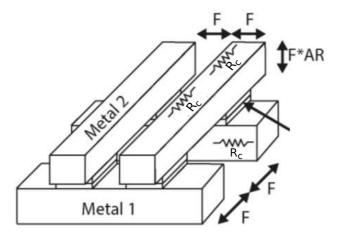

Driven by the growing demand for memory performance and storage capacity, industry is exploring solutions from continuing the conventional scaling to other high-density storage techniques such as multi-level cell (MLC) storage, three-dimensional (3D) integration and crosspoint array architecture. These solutions are required to increase storage capacity and efficiency, thus to achieve high capacity and efficiency at low cost. For instance, in crosspoint arrays, memory cells are built at the junctions of a lower and an upper plane of parallel metal lines running at right angles to each other, and hence if both the width of the metal lines and the spacing between them is equal to the minimum lithographic feature size, F, the memory cell can be allocated within the smallest footprint of  $2F \times 2F$ . The effective area per cell can be reduced even further with 3D integration. In addition, if the memory arrays are sufficiently large, much of the peripheral circuitry (including address decoders, sense amplifiers, and control circuitry) can be placed underneath the arrays, thereby increasing area efficiency (i.e., reducing the fraction of silicon area associated with the memory array) and this implies lower cost per bit.

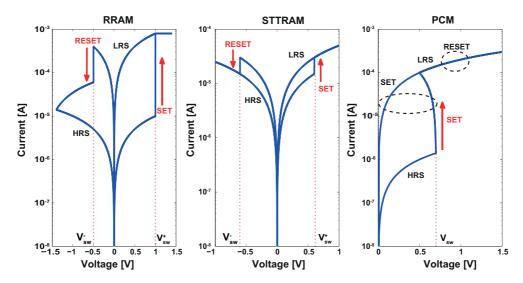

As technology scales down, increasing leakage power dissipation and significant degradation of the reliability of SRAM and DRAM are of increasing concern. In the case of NAND Flash, in addition to reliability concerns, its performance is still limited. As a result, emerging memory technologies, such as Resistive Random Access Memory (RRAM), Phase Change Memory (PCM), and Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), are actively under research and development due to not only their promising scalability but also their reduced standby power and access speed. Unlike SRAM, DRAM and NAND Flash, which are charge-based, the most attractive emerging memories, including the aforementioned ones, operate based on resistance switching principle: the basic storage device is switched between a high-resistance state (HRS) and a low-resistance state (LRS) to store bits. The transition between the two states is triggered by applying electrical voltage/current pulses. These emerging memories are expected to be used mainly as a Storage class memory (SCM), a new class of memory with a storage capacity and cost per bit similar to NAND Flash but with a speed that approaches DRAM. Due to this features, SCM helps to address the aforementioned performance disparity between microprocessors and memory.

In particular, STT-MRAM, the basic storage element of which is a Magnetic Tunnel Junction (MTJ), has demonstrated a high write speed and a practically infinite cyclic endurance, which makes it a potential candidate not only as a storage class memory but also as DRAM and SRAM replacement. However, STT-MRAM faces some challenges. One of the crucial challenges is that the sense margin (i.e., the voltage/current margin available for sensing by the sense amplifier to differentiate the LRS and the HRS states) is very small due to the intrinsically small ratio of the resistance value of the two states, which is usually worsened by process variations in the STT-MRAM cells and parasitics of interconnection metal lines. Resistive random access memory (RRAM), with a typical metal-oxide-metal device structure, has also gained great attention with the prospects of obtaining a replacement for both embedded memory and mass storage applications, which have their own requirements. For example, low operating voltage (for compatibility with the core CMOS technology) and high cyclic endurance are required embedded memory whereas acceptable power consumption and high cell density are required issue in mass storage applications.

#### 1.2 The Memory Sub-System

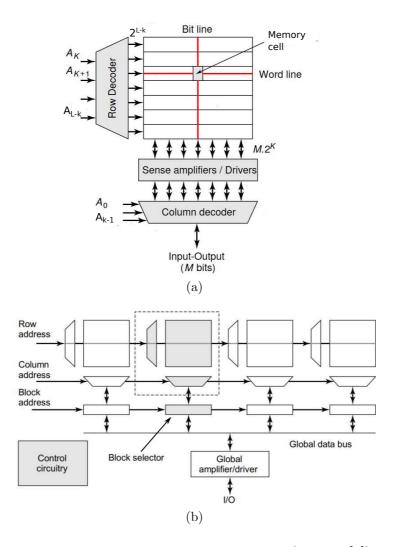

Semiconductor memory chips consist of millions to billions of memory cells organized in array structure. In particular, in Random Access Memory (RAM), individual cells can be accessed by activating the appropriate wordlines and bitlines as shown in Figure 1.1a. The binary address inputs are decoded by row and column decoders to locate the corresponding target cells, so that read and write operations can be performed [3]. Furthermore, large memory arrays are organized as sub-array blocks of as shown in Figure 1.1b.

#### 1.2.1 Memory Hierarchy

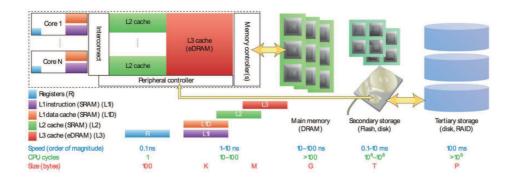

In today's microprocessors, a hierarchical memory organization, which integrates different memory technologies, is used to achieve optimal overall performance, area, and cost [5,6]. Accordingly, SRAM, which is the fastest one, is used in cache memories [7,8]. DRAM comes next in the hierarchy as a main memory due to its higher cell density [5,6,8]. Flash memory features low cost per bit and non-volatility, which have made it the technology of choice for secondary mass storage [6,8]. Figure 1.2 shows the physical distribution of memory in computer, starting from the fastest registers and L1 cache to the slowest tertiary storage. From left to right, speed decreases while storage capacity increases.

Figure 1.1: Memory array organization (source: [4])

Figure 1.2: Physical distribution and hierarchy of memory in a computer (source: [9]). The lower panel shows speed (as order of magnitude), number of processor cycles needed for accessing the memory, and storage capacity in bytes (as order of magnitude).

#### 1.3 Mainstream Solid-State Memories

#### 1.3.1 Static Random Access Memory (SRAM)

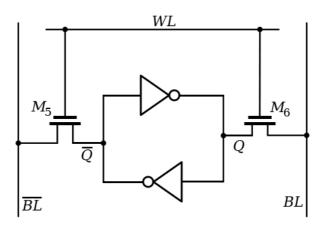

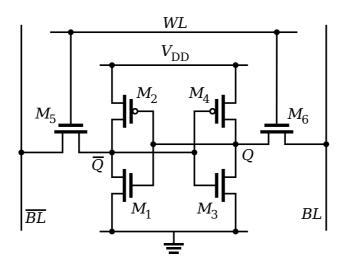

Static Random Access Memory uses a bistable latch circuit to hold the stored bit, as shown in Figure 1.4. The latch circuit is formed by the two cross-coupled inverters and the two transistors (M 5 and M 6) connected with the wordline and two bitlines, are used as access transistors to select target cells. Here, Q represents the data stored in the SRAM, which could be either bit '0' or bit '1' and  $\overline{Q}$  is the complementary data. The term 'static' is derived from the fact that the stored data can be retained with no need for refreshing as long as power is being supplied. In the most common CMOS SRAM cell, each of the two inverters are implemented with complementary NMOS and PMOS transistors, hence resulting in the 6-transistor SRAM cell structure shown in Figure 1.4 [3].

Figure 1.3: Static RAM operation

Figure 1.4: 6-Transistor SRAM cell

#### 1.3.2 Dynamic Random Access Memory (DRAM)

The basic storage element of a Dynamic Random Access Memory (DRAM) is a capacitor. The data (bits '0' and '1') is represented by whether the capacitor is fully charged or discharged. A DRAM cell with a select transistor is shown in Figure 1.5.

However, the electrical charge on the capacitor will gradually leak away, and after a period of time, the voltage on the capacitor will be too low to differentiate between '0' and '1'. As a result, all DRAM cells need to be read out and written back periodically (known as a refresh) to ensure data integrity [3].

Figure 1.5: 1-Transistor DRAM cell

Figure 1.6: Floating gate flash memory cell

#### 1.3.3 Flash Nonvolatile Memory

Flash memory is the most widely used nonvolatile memory technology today. The key device in this prevailing memory is a floating gate transistors whose cross section is shown in Figure 1.6. Unlike a MOSFET transistor, an additional floating gate (FG) is added between the control gate (CG) and channel. The data is encoded based on the presence or absence of electrons trapped in the FG and the data is retained without power. Since, it is isolated by oxide layers, the floating gate is able to trap charges and keep them for years, giving a non-volatility of Flash memory.

Figure 1.7: Flash memory: (a) NOR (b) NAND

There are two common layouts for flash memory namely, NAND flash memory with Floating gate transistors in series and NOR flash memory with floating gate transistors in parallel, as shown in Figure 1.7. The names NAND and NOR are derived from the fact that their connection fashion in series or parallel resembles a NAND gate or NOR gate. Since NAND Flash has one ground connection and two select transistors for each row, it provides with higher storage density than NOR Flash. Hence, it is widely used in external storage. Whereas, NOR Flash has lower latency and thus is widely used in embedded systems, where high performance is required.

## 1.4 Challenges of Mainstream Memories and Current Research and Development Trends

The direction of research and development on memory device technologies and architectures is shaped by some key technology trends. The first trend is the increasing difficulty of scaling down of the mainstream memory technologies [6, 7, 10, 11]. Scaling is needed for increasing storage capacity and efficiency; lack of it will make it difficult to achieve high capacity at low cost [11]. In Flash memory, scaling down the storage-cell tunneling area results in the reduction of the number of electrons that are injected to the floating gate during programming. These electrons determine the threshold voltage that is used to differentiate bit '1' and bit '0'. However, due to the reduction of the number of electrons due to scale down, a slight variation in the number of these electrons or the loss of some of the stored electrons over time may produce significant threshold voltage variations, thus lead to read errors and reliability concerns [10]. In DRAM, the unavoidable scaling of storage capacitance to scale down the overall memory cell size leads to poor data retention time and insufficient read margin [12]. SRAM also faces its own challenges when its constituent transistors are scaled down [13]. As technology scales down, it becomes more difficult to control variations when fabricating minimum-sized transistors. As a result, the quality and the reliability of SRAM's constituent transistors and, hence, SRAM cell reliability, are degraded [13]. This motivated the emergence of the aforementioned emerging memory technologies.

The second technology trend is the increasing performance disparity between processor and memory. As discussed in Section 1.2.1, the conventional approach, a strongly hierarchical memory organization, which mostly integrates SRAM, DRAM, and Flash memory, is used to achieve optimal overall performance, area, and cost [5,6]. However, with the evolution of fast microprocessors, fully exploiting their computational power with such memory hierarchy has become quite challenging. Hence, there are efforts to flatten the memory hierarchy [11,12]. On technology side, the ideal solution would be using a single "universal" memory device that satisfies all the ideal characteristics: fast read/write speed, low cost per bit, low power consumption, nonvolatility, and so on. Although, it is almost impossible to get a "universal" memory device, some of the emerging memories have been pursued toward achieving part of the aforementioned ideal characteristics [14].

The third key trend is the steadily increasing demand for large data storage capacity [12], as also mentioned earlier. In fact, the amount of data to be processed is steadily increasing over time at a rate higher than that of Moore's law [12]. To satisfy this demand, industry is exploring, other options in addition to the conventional scaling down, such as multi-level cell (MLC) storage and three-dimensional (3D) integration to improve memory density [12], and hence, to reduce the cost per bit. For example, Figure 1.8 shows a 32-layer 3D NAND Flash memory for high-density storage. Crosspoint array has also become an attractive architecture to achieve high-density memory design [15, 16]; benefiting from the recent development of the partially-mentioned emerging memory technologies that are well-suited for the architecture due to their two-terminal device structure.

Figure 1.8: 32-layer 3D NAND Flash memory (source: Micron website, accessed on December 15, 2018)

#### 1.5 Objectives of the Thesis

With the aim of contributing to the research and development on emerging memories, this PhD thesis presents a model-based study of Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), an experimental electrical characterization of two Resistive Random Access Memory (RRAM) device technologies, and a comprehensive analysis of design and technology considerations and requirements for high-density crosspoint memory array architecture.

In the first part, the thesis presents a behavioral model of STT-MRAM cell that can be used for circuit simulations, review of different sensing circuit schemes applicable for STT-MRAM and a variability-aware analysis and design guideline of slope detection self-reference scheme, which is deemed to outperform other STT-MRAM sensing schemes reported in the literature. The performance of this sensing scheme is analyzed by taking into account the impact of cell-to-cell variations and parasitic resistance in bitlines, BLs, and wordlines, WLs.

The second study focuses on the electrical characterization of RRAM memory technologies, namely Oxide Resistive RAM (OxRAM) and Conductive Bridging Resistive RAM (CBRAM). For the case of OxRAM, the purpose of this study is to establish the performance of the memory array according to oxide thickness, density and size of devices. As for the CBRAM, the study focuses on reliability (endurance and retention) performance of the memory devices under different programming pulse amplitude and width, and at the same time, optimization of the pulses for better reliability.

The last study focuses on analysis of crosspoint memory array design based on 1S1R (one selector coupled to one resistive memory). Despite promise of crosspoint memory arrays for high-density storage, their implementation is challenged by some critical issues such as, sneak-path (leakage) currents and ohmic drop due to parasitic resistance in the interconnection metal lines, which will be elaborated in Chapter 4 (Section 4.2). Hence, the thesis presents a comprehensive analysis of crosspoint arrays by taking into account selector device and memory element operating characteristics, the impact of the BL and WL parasitic elements, the size of the memory array and the biasing scheme. The analysis is aimed at contributing to the understanding of crosspoint array implementation constraints. It also gives a guideline for circuit design and for memory/selector device technology optimization.

#### 1.6 Organization of the Thesis

The thesis is structured as the following chapters. In Chapter 2, the study on STT-MRAM is discussed. After providing an overview on the application targets, key technology advances and challenges of STT-MRAM, the basic physical principle of operation of STT-MRAM is discussed with reasonable detail. Then, the developed behavioral model of STT-MRAM device is discussed and validated by circuit simulations. The next part of this chapter focuses on reading in STT-MRAM, which appears to be the fundamental challenge of this technology. In this regard, different circuit schemes are reviewed followed by analysis of self-referenced slope detection sensing architecture, which is deemed to give better read performance compared to the other sensing techniques proposed in the literature. A study of the impact of variability on the chosen self-reference slope detection sense amplifier architecture is then provided. A theoretical study, validated by simulation, proposes an original variation-aware optimization of the reading margin of this sensing technique. The chapter is concluded by providing an overall summary of the presented results.

Chapter 3 presents, consecutively, a detailed experimental electrical characterization of Oxide RAM with TiN/Hf/GdAlO/TiN device stack (or GdAlO-based OxRAM) and a reliability study of Conductive Bridging RAM with Cu/TiW/SrTiOx/WOx/W stack (or STO-based CBRAM). In the first part of the chapter, a brief discussion of the underlying operating principles of RRAM is presented followed by explanation of application targets for RRAM and the corresponding requirements for these applications. Then, the experimental setup for the electrical characterization of the GdAlO-based OxRAM is described and the obtained various results are analyzed in detail. The presented analysis focuses on the impacts of the thickness of the GdAlO layer, the size of the memory device, and memory cell density on arraylevel operating voltage/current performance and reliability. Similarly, for the CBRAM, the experimental setup used for the characterization is described and endurance and retention performance under different programming pulse amplitude and width conditions is presented. Analyzing the performances obtained on STO-based CBRAM devices, using optimized pulses completes this study. Finally, a conclusion is drawn from the experimental results and a recommendation for future work is made.

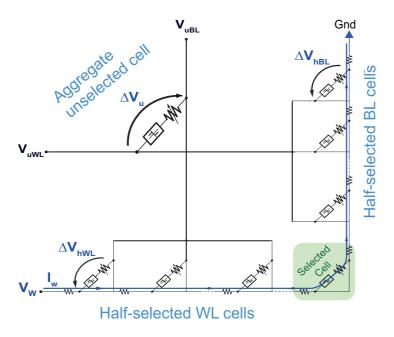

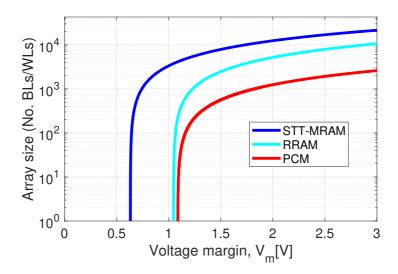

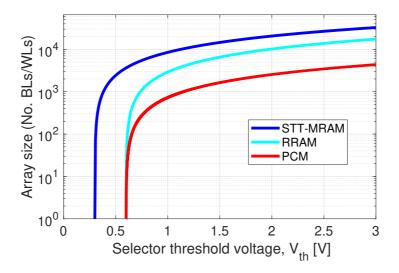

Chapter 4 is dedicated to the discussion of the study on crosspoint array design based on 1S1R (one selector coupled to one resistive memory). In the first part of this chapter, an introductory overview of crosspoint arrays and a review of research trends is provided, followed by a discussion of the challenges faced by crosspoint arrays. Then, a brief survey of selector together with their non-linearity feature is first reported, followed by the description of selector modeling. Resistive elements as well as interconnection metal line considerations are also discussed. A simplified array model for the worst-case scenario, which enables to reduce computation time to study large crosspoint arrays, is also presented. Then, a first analysis, which gives the boundary conditions of a proper write operation neglecting sneak-path as well as IR drop issues, is presented. The next part is dedicated to the evaluation of the array size considering all the design constraints (selector sensitivity, selector voltage margin, selector threshold, IR drop and voltage/current switching characteristic of the resistive element), which draws very interesting design guideline for crosspoint memory arrays. The analysis is extended for read operation evaluating the read margin versus the array size and the resistance ratio. The next part of this chapter is devoted to the analysis of the variability of the memory and of the selector element regarding voltage compatibility, which allows determining acceptable threshold voltage/switching voltage ratio for proper read and write operations considering variability. Then, a generic "x biasing" scheme is introduced in order to minimize leakage and is compared to conventional biasing schemes considering. Finally, some conclusions are drawn based on the results of the analyses presented in the chapter.

Finally, in Chapter 5, a general conclusion is drawn from the results presented in the preceding three chapters and an outlook for future work is provided.

## Chapter 2

# Spin-Transfer Torque Magnetic RAM (STT-MRAM)

#### 2.1 Overview

Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) has gained much attention due to its very desirable properties such as storage class nonvolatility, low standby power, area (and) current scalability, high write speed, and practically infinite cyclic endurance, which can be incorporated to all levels of the memory hierarchy [6, 17, 18]. In comparison with the competitor emerging memory technologies, STT-MRAM uniquely features a high write speed and a practically infinite endurance that make it a very good candidate not only as storage class memory but also as DRAM and SRAM replacement [6,7,19,20]. The speed and the endurance of STT-MRAM are comparable to that of DRAM, while STT-MRAM also provides with some additional benefits. Most notably, STT-MRAM is a nonvolatile technology and, hence, it does not require refresh unlike DRAM, which gives energy and reliability advantages [18]. Indeed, Everspin's 256 Mb STT-MRAM DDR3 (Double Data Rate) is already in mass production replacing Synchronous DRAM (SDRAM). However, as of today, the cost of production of STT-MRAM is higher than that of DRAM, which is already a mature technology with huge production volumes and, thus, the adoption of STT-MRAM as DRAM replacement is only justified in cases where the need for the performance advantages outweigh the additional cost. As for SRAM replacement, STT-MRAM has advantage of nonvolatility and higher density, while maintaining write/read speed and endurance comparable to that of SRAM [7, 18].

In fact, it has been demonstrated in the literature that STT-MRAM can give a better performance (speed) than that of SRAM in relatively large memory array sizes like in the case of L2 and L3 caches [21, 22]. In such large-size memory arrays, the overall access (read/write) time is dominated by interconnection line delay. Due to the smaller size of STT-MRAM memory cell, the same array storage capacity can be implemented with a smaller silicon area, which results in a shorter global interconnect delay and hence, better cache performance (speed). However, in small array sizes like L1 cache at the core level, SRAM gives a better read/write speed [21] than that of STT-MRAM. Yet, the research and development efforts on STT-MRAM technology are continuing. In addition, it has been proposed an alternative magnetic memory concept, namely Spin-Orbit Torque MRM (SOT-MRM), that features sub-nanosecond switching speed making it a good candidate for L1 cache memory [23, 24].

# 2.2 Key Technology Advances and Challenges of STT-MRAM

The Magnetoresistance (MR) effect, which is the change of the electrical resistance of materials by an externally-applied magnetic field, has been known since 1856 [25]. However, it was the discovery of the Giant Magnetoresistance (GMR) effect, which is observed in structures made up of two ferromagnetic layers sandwiching a non-magnetic metallic spacer layer (or in multi-layers of such sandwich structure), that opened the way to a more efficient control of electron charge transport through magnetization [20, 26]. When the magnetization, which measures the local orientation of electron spins, of the two ferromagnetic layers are aligned to the same direction (parallel orientation), a relatively low resistance,  $R_P$ , is observed. On the contrary, when the magnetizations of the two layers are oriented in antiparallel, a relatively high resistance,  $R_{AP}$ , is observed. As a crucial advancement, a much higher Tunnel Magnetoresistance (TMR) ratio, a performance index defined as the relative difference of resistance between the antiparallel and parallel states, i.e. TMR ratio =  $[(R_{AP} - R_P)/R_P] \cdot 100\%$ , was obtained by replacing the metal spacer in the GMR structure with a thin non-magnetic (insulating) tunnel layer, hence obtaining a structure referred to as a Magnetic Tunnel Junction (MTJ). In this regard, the first room temperature MTJ with TMR ratio of 11.8% was demonstrated by Moodera et al. [27]. Further improvements of TMR ratio steadily continued. For instance, a TMR ratio of 200% was reached by using a single-crystal MgO tunnel barrier [28].

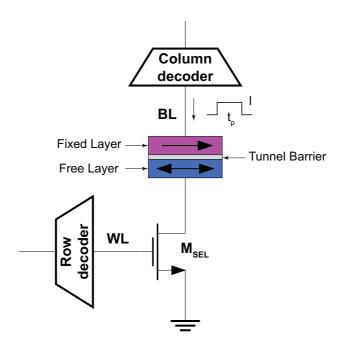

As shown in Figure 2.1, MTJ is the basic storage element in the STT-MRAM memory cell. One of the ferromagnetic layers is magnetically pinned during manufacturing while the remaining ferromagnetic layer is free to be switched into parallel or anti-parallel direction with respect to the fixed layer magnetization [29].

The other key technology advance was the discovery of spin-transfer torque effect as a way of switching the magnetization of nanomagnets. The spin-transfer torque (STT) effect was for the first time theoretically predicted by Slonczewski [30] and by Berger [31] in 1996 [29]. In the classic MRAM that preceded STT-MRAM, the memory cell lies between a wordline and a bitline arranged at right angles to one another, one below and the other above the cell and when a sufficiently high current passes through the wordline or the bitline, an induced magnetic field is produced at the intersection of the lines, which imparts torque that enables the switching of the free layer. However, since a magnetic field is difficult to localize, this technique is energy inefficient [29]. Using spin-transfer torque effect enabled a more efficient way of switching nanomagnets.

However, there are still efforts to reduce the switching current further as a high write current not only leads to energy inefficient write operations but also constrains the scalability of the driving transistors. In this respect, a perpendicular MTJ (as opposed to the in-plane MTJ shown in Figure 2.1) was introduced in 2010 [32]. Besides, more efficient write techniques such as voltage-controlled magnetic switching (VCMA), are being investigated to improve the write performance of the memory cells [33].

Insufficient sense margin is one of the critical challenges of STT-MRAM [1, 33]. This is mainly attributed to the intrinsically small TMR ratio [1]. Apart from the intrinsically small TMR ratio, process variations in the MTJ and the selector device of STT-MRAM cells within an array (cell-to-cell variations) put another key challenge on the design of the sensing circuit scheme [34]. The important sources of the cell-to-cell variations are the thickness of the tunnel oxide barrier (which is as thin as 1–2 nm) and the geometric size (surface area) of the MTJ device. Indeed, due to quantum mechanical tunneling, the resistance of an MTJ has an exponential relationship to the thickness of the oxide barrier between the two magnetic layers [34,35]. It is also worth to point out that the variation of the MTJ resistance will be aggravated by the further reduction of the oxide barrier thickness and the large MTJ geometry variation in scaled technologies [36].

Figure 2.1: STT-MRAM cell with a MOS transistor as a selector

#### 2.3 Basic Physics of STT-MRAM

#### 2.3.1 Principle of Operation

Figure 2.1 shows STT-MRAM cell with a MOS transistor selector. The binary digits are stored as a low- or a high-resistance state of the MTJ, which is controlled by switching the magnetization of the free layer to parallel or antiparallel direction, respectively, with respect to the fixed layer magnetization. The parallel configuration results in a low MTJ resistance state (assigned to bit '0'), whereas the anti-parallel configuration yields a high MTJ resistance state (assigned to bit '1'). The switching of the state of the STT-MRAM cell is achieved by using the spin-transfer torque effect, which is briefly discussed here referring to Figure 2.2.

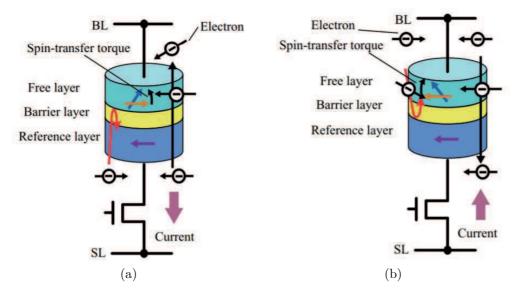

Let us assume that electrons flow from the fixed (reference) layer to the free layer (equivalently, current flows from free to fixed layer) and assume that the two layers were initially magnetized along opposite directions as in Figure 2.2a. The electrons become spin polarized when they pass through the reference layer. As a result, the electrons coming out of the reference layer mainly hold a spin direction parallel to the magnetization of the reference layer. Then, the spin-polarized electrons tunnel through the thin insulating layer (maintaining their polarization) and reach the free layer, where their average spin is quickly re-aligned to the magnetization of the free layer. In the process, the electrons lose a spin angular momentum and, due to the conservation of total angular momentum, the lost angular momentum is transferred to the magnetization of the free layer. This results in a torque tending to align the magnetization of the free layer towards the spin momentum of the incoming electrons and, hence, towards the magnetization of the fixed layer [37, 38]. The magnetization of the free layer will be switched if the amount of the spin-polarized electrons exceeds a given threshold value.

In the opposite case, i.e., parallel-to-antiparallel switching (see Figure 2.2b), current should flow from the reference layer to the free layer (i.e., electrons flow from the free to fixed layer). The electrons become spin-polarized after going through the free layer, hence the majority of them will have a spin direction parallel to the magnetization of the free layer. These electrons will pass through the reference layer since their spin direction is also parallel to the magnetization of the reference layer.

Figure 2.2: STT switching (a) antiparallel to parallel switching (b) parallel to antiparallel switching

However, those electrons with a spin direction antiparallel to the magnetization of the reference layer will be reflected at the interface between the junction and the reference layer. This results in a spin-polarized current injecting into the free layer and exerting spin-transfer torque on the magnetization of the free layer. Similar to the complementary case, the magnetization of the free layer will only switch when the amount of the spin-polarized electrons exceeds a given threshold value and an antiparallel state is obtained [37,38].

For reading the stored data, one can force a small current (namely, a current smaller than the switching threshold current) through the cell and sensing the resultant voltage across the cell, which is then compared to a reference voltage to determine whether bit '1' or bit '0' was stored.

#### 2.3.2 Switching Current

The intrinsic critical current  $(I_{c0})$ , proposed by Slonczewski [39], is used as a figure of merit in macro-spin models of current driven magnetization switching in nano-magnetic devices like STT-MTJ. It is defined as the minimum current which is able to cause a spin flip in the absence of any external magnetic field at absolute zero temperature.

For an in-plane MTJ,  $I_{c0}$  can be expressed in terms of the magnetic properties of the MTJ [40] as given by (2.1)

$$I_{c0} = \frac{2e\alpha M_S V \cdot (H_K + 2\pi M_S)}{\hbar \eta} 2x \tag{2.1}$$

where e is the absolute value of electron charge,  $\alpha$  is the damping factor,  $M_S$  is saturation magnetization, V is the volume of the free layer,  $H_K$  is the effective anisotropy field,  $\hbar$  is reduced Planck's constant, and  $\eta$  is the spin torque efficiency factor, which is a function of the current polarity, material polarization and the relative angle between the magnetization in the free and in the fixed layer [41].

Due to the inherent torque asymmetry in the MTJ cell, the critical currents required for switching from the parallel P to the anti-parallel AP state  $(P \to AP)$  and from the anti-parallel to the parallel state  $(AP \to P)$  are different; more specifically, the critical switching current for  $(P \to AP)$  switching being significantly larger. It is apparent from equation (2.1) that the switching current is directly proportional to the volume of the free layer, which means that  $I_{c0}$  decreases when scaling down the size of the MTJ cell. However, scaling down the size of the MTJ cell generally requires a trade-off between switching current and thermal stability factor,  $\Delta$ , which is given by:

$$\Delta = \frac{H_k M_s V}{2K_b T} \tag{2.2}$$

where  $K_b$  is Boltzmann constant and T is (absolute) operating temperature. One wants to minimize  $I_{c0}$  while still preserving a reasonable thermal stability factor for non-volatility. In this respect, the intrinsic switching current to thermal stability ratio,  $\frac{I_{c0}}{\Delta}$  given by (2.3) can be used as a more useful figure of merit:

$$\frac{I_{c0}}{\Delta} = \frac{4e\alpha K_b T \left(1 + \frac{2\pi M_s}{H_k}\right)}{\hbar \eta} \tag{2.3}$$

This equation was derived directly from (2.1) and (2.2).

As can be seen from equation (2.3) equation, by means of materials engineering, the critical current can be reduced without sacrificing thermal stability by using ferromagnetic materials with low magnetization  $M_s$  and/or high spin transfer efficiency  $\eta$  and/or small damping factor  $\alpha$  [40]. Another promising method to decrease the switching current is to decrease the demagnetizing field by introducing perpendicular anisotropy in the free layer [40]. In a perpendicular MTJ, the magnetization direction is perpendicular to the plane of the ferromagnetic layers, which cancels out the effect of the demagnetization field, thus reducing the value of  $I_{c0}$  [40].

In long current pulses, switching can occur even with a current pulse amplitude lower than the critical current (i.e.  $I < I_{c0}$ ) due to thermal fluctuations. In the presence of spin torque and long current pulses, when thermal activation plays a major role, the switching time (or, in other words the pulse width required for magnetization switching) can be calculated by applying [40, 42]

$$\tau_1 = \tau_0 \cdot e^{\left[\Delta \left(1 - \frac{I}{I_{c0}}\right)\right]} \tag{2.4}$$

where,  $\tau_0$  (about 1 ns for storage class memory purposes) is the minimum time required to reverse the magnetization, referred to as thermal attempt time. The critical switching current  $(I_c)$  associated with a pulse width  $t_p$  can be obtained as [43]:

$$I_c = I_{c0} \cdot \left[ 1 - \frac{1}{\Delta} ln \left( \frac{t_p}{\tau_0} \right) \right] \tag{2.5}$$

When the current pulse has an amplitude I higher than the critical one, switching is dominated by the spin-transfer torque effect and the thermal random effect becomes less important. Consequently, the current pulse required for switching can be narrower. The switching time can be estimated by using [44]

$$\tau_2 = \frac{1}{\alpha \mu_0 \gamma M_S} \cdot \frac{I_{c0}}{I - I_{c0}} \cdot ln\left(\frac{\pi}{2\theta_0}\right) \tag{2.6}$$

where  $\gamma$  is the gyromagnetic ratio,  $\mu_0$  is the permeability constant), and  $\theta_0$  is the root square average of the initial angle of the free layer magnetization (determined by thermal fluctuation).

#### 2.3.3 Probability of Switching

Spin-transfer torque (STT)-based switching is intrinsically stochastic, and the probability of switching of state is generally a function of the amplitude and the width the current pulse passing through the MTJ device, I and  $t_p$ , respectively, and technology dependent parameters  $I_{c0}$  and  $\Delta$ . For sufficiently long current pulses ( $t_p \geq 10$  ns) with amplitude  $I < I_{c0}$ , the probability of switching can be expressed as: [40, 42, 43]:

$$P_{sw} = 1 - \exp\left\{\frac{-t_p}{\tau_0} \exp\left[-\Delta \left(1 - \frac{I}{I_{c0}}\right)\right]\right\}$$

(2.7)

Since intrinsic critical current is different for  $P \rightarrow AP$  and  $AP \rightarrow P$  switching, the probability of parallel to anti-parallel switching (denoted as  $P_{sw,P\rightarrow AP}$ ) and the probability of anti-parallel to parallel switching (denoted as  $P_{sw,AP\rightarrow P}$ ) are also different even with the same current pulse amplitude and width.

#### 2.3.4 Static Behavior of STT-MRAM Cell

The static behavior of the MTJ in STT-MRAM cell can be represented by the resistance values of the anti-parallel and parallel states that are related to each other by the TMR ratio given by:

$$TMR \ ratio = \left(\frac{R_{AP} - R_P}{R_P}\right) \cdot 100\% \tag{2.8}$$

It is a measure of the distinguishability of the high- and the low- resistance states.

Besides, it has been demonstrated in the literature that the resistance values  $R_{AP}$  and  $R_P$  are dependent on the current/voltage bias of the MTJ [42, 44, 45]. In both the low- and the high- resistance state, the resistance value is maximum at zero current and starts to roll off when current flows through the MTJ. This characteristic can be modeled by using the following equations:

$$R_{AP} = R_{AP0} - S_{AP} \cdot I \tag{2.9a}$$

$$R_P = R_{P0} - S_P \cdot I \tag{2.9b}$$

where  $R_{AP0}$  and  $R_{P0}$  are the values of  $R_{AP}$  and  $R_{P}$  respectively, at zero current and  $S_{AP}$  and  $S_{P}$  are the corresponding slopes (or curve fitting parameters) for the resistance roll-off, which can be determined from experimental data. Generally,  $S_{AP}$  is larger than  $S_{P}$ .

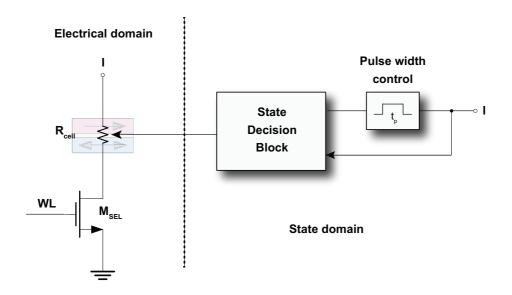

#### 2.4 Model of STT-MRAM

In this thesis work, a behavioral model of STT-MRAM cell was developed using Verilog-A language. This model is described by the block diagram shown in Figure 2.3 and was used to perform analyses using the device technology parameters given in TABLE 2.1. The storage element (MTJ) was modeled as a variable resistor whose resistance value is controlled by the state of the cell and the amplitude of the current pulse. The bias dependence of the resistance values is also considered according to (2.9a) and (2.9b).

The 'state decision' block controls the state of the cell. To take into account the intrinsically stochastic nature of STT-MTJ dynamic behavior, the block was implemented as a Bernoulli random binary number generator, in combination with the probability of switching function given by (2.7).

Figure 2.3: Block diagram of the proposed STT-MRAM Verilog-A model

If the previous state was bit '0' (parallel state), the state is retained if the write current is positive. In contrast, if the current is negative, state changes to bit '1' with a probability equal to  $P_{sw,P\to AP}$  or remains unchanged with a probability equal to  $1-P_{sw,P\to AP}$ . For the complementary case, if the previous state was bit '1', the bit '1' state is retained if the write current is negative, whereas if the current is positive, the state changes to bit '0' with a probability equal to  $P_{sw,P\to AP}$  or remains bit '1' with a probability equal to  $1-P_{sw,P\to AP}$ .

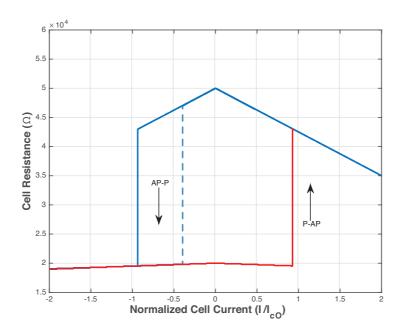

The STT-MRAM cell model is used in Cadence Virtuso platform to carry out simulations to demonstrate characteristics of the STT-MRAM cell. The simulated R-I characteristic is shown in Figure 2.4, with the resistance value of high-resistance AP state shown in blue color and the resistance value low-resistance P state shown in red color. In both states, the resistance value decreases when the amplitude of current pulse increases, with the high-resistance in the AP state dropping faster than the low-resistance in the P state, which results in decrease of TMR ratio. As expected, switching from one state to another state occurs when the programming current is sufficiently high (approximately equal to  $I_{c0}$ ), as can be seen from the transitions. The dashed line corresponds to the case of a cell with an asymmetrical R-I characteristic i.e.,  $AP \rightarrow P$  and  $P \rightarrow AP$  transitions occur at different currents. The switching currents in both transitions are normalized to  $I_{C0,P\rightarrow AP}$ . The results shown are consistent with the physical properties of the MTJ device and with results available in the literature [17, 20].

Table 2.1: STT-MRAM Technology Parameters

|                                                          | Mean value               | Variations |

|----------------------------------------------------------|--------------------------|------------|

|                                                          |                          | $(\sigma)$ |

| Resistance-area (RA) product corresponding to            | $6 \Omega \cdot \mu m^2$ | 7.5%       |

| parallel state at low field (100 mV)                     |                          |            |

| Ratio of RA (corresponding to parallel state) at         | 0.8                      |            |

| high field (400 mV) to RA at low field (100 mV)          |                          |            |

| MTJ device diameter                                      | 20 nm                    | 7.5%       |

| Parallel state resistance $(R_P)$ at zero bias           | $20~\mathrm{k}\Omega$    | 7.5%       |

| Tunnel Magnetoresistance Ratio (TMR) ratio at            | 100%                     | 4.5%       |

| low field (100 mV)                                       |                          |            |

| Parallel state resistance roll off: $R_P$ at 600 mV      | 16 kΩ                    |            |

| Anti-parallel state resistance roll off: $R_{AP}$ at 600 | $22.4~\mathrm{k}\Omega$  |            |

| mV                                                       |                          |            |

| Thermal stability factor $\Delta$                        | 60                       | 7.5%       |

| Critical current density for P to AP switching,          | 4.                       |            |

| $J_{c0,P \to AP}$                                        | $10^{6} A/cm^{2}$        |            |

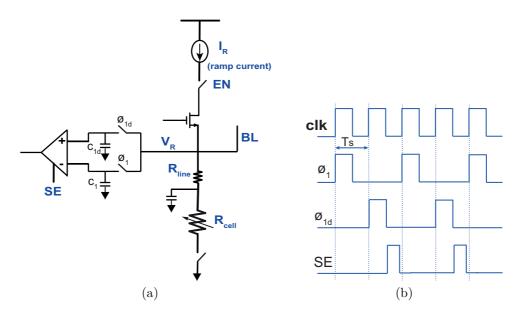

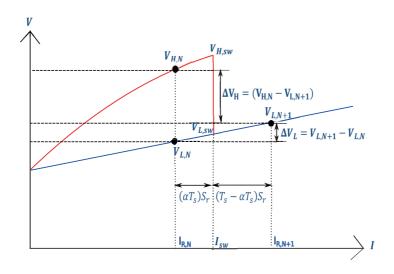

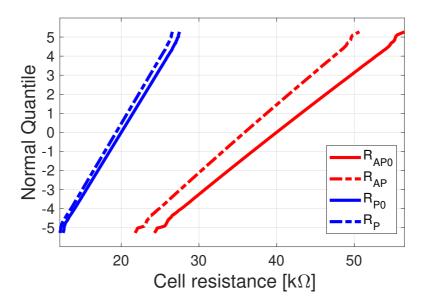

| Critical current density for AP to P switching,          | 2.                       |            |