#### UNIVERSITÀ DEGLI STUDI DI PAVIA

#### FACULTY OF ENGINEERING

Department of Electrical, Computer and Biomedical Engineering

Ph.D school in Electronics, Computer Science and Electrical Engineering XXXI Cycle

## Design and characterization of CMOS SPADs for charged particle detectors

Advisor:

Prof. Carla Vacchi Prof. Lodovico Ratti

Ph.D Coordinator: Prof. Paolo di Barba

> Ph.D thesis of Marco Musacci

Academic Year 2017/2018

## Contents

| 1 | $\mathbf{SP}^{A}$ | Ds an  | nd the APiX2 project                                 | 3  |

|---|-------------------|--------|------------------------------------------------------|----|

|   | 1.1               | Opera  | ating principle of semiconductor detectors           | 4  |

|   | 1.2               | Avala  | nche sensors                                         | 6  |

|   |                   | 1.2.1  | Single Photon Avalanche Diode (SPAD)                 | 8  |

|   |                   | 1.2.2  | Quenching circuits                                   | 10 |

|   | 1.3               | Dark   | count rate and breakdown voltage                     | 17 |

|   | 1.4               | The A  | APiX2 project                                        | 22 |

|   |                   | 1.4.1  | Detector working principle                           | 22 |

|   |                   | 1.4.2  | APiX2 sensor prototypes                              | 24 |

| 2 | $\mathbf{AP}$     | IXFAE  | 30: chip design and test setup                       | 27 |

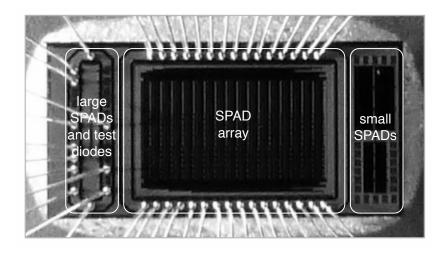

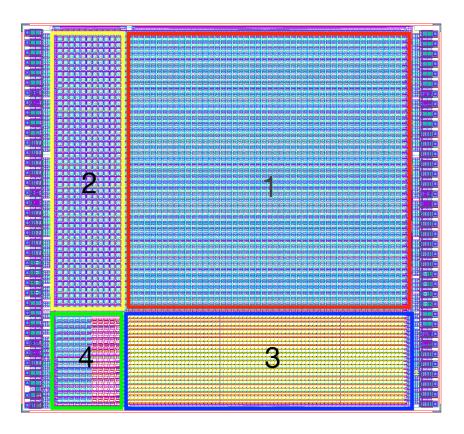

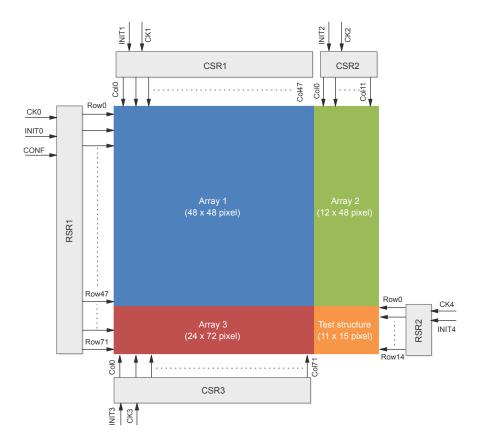

|   | 2.1               | Chip o | description                                          | 27 |

|   |                   | 2.1.1  | Test SPADs                                           | 28 |

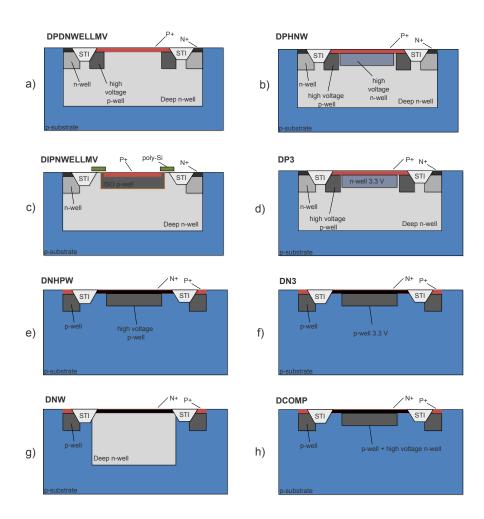

|   |                   |        | 2.1.1.1 SPAD types                                   | 29 |

|   |                   |        | 2.1.1.2 SPAD size and common layers                  | 29 |

|   |                   |        | 2.1.1.3 Layers and structure                         | 29 |

|   |                   |        | 2.1.1.4 Test diodes                                  | 34 |

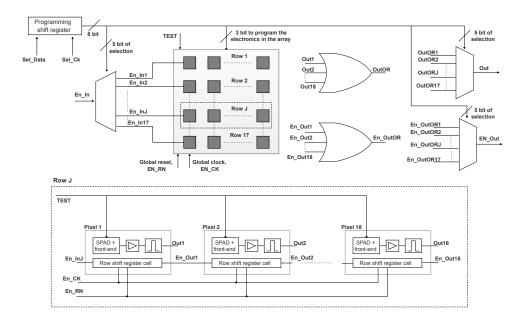

|   |                   | 2.1.2  | SPAD array                                           | 34 |

|   |                   | 2.1.3  | SPADs under test: DPD and DPH                        | 36 |

|   |                   | 2.1.4  | Front-end electronics                                | 37 |

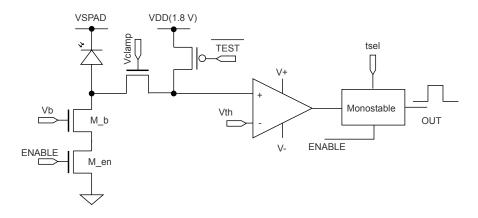

|   |                   |        | 2.1.4.1 Passive quenching readout                    | 37 |

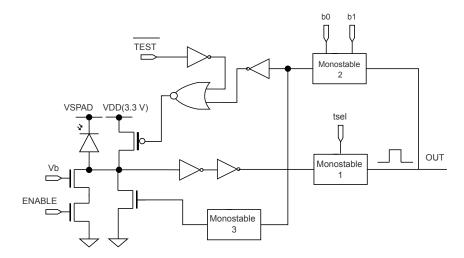

|   |                   |        | 2.1.4.2 Active quenching, inverter based readout     | 38 |

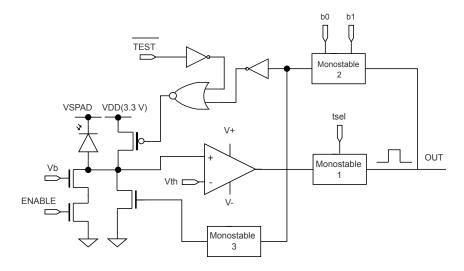

|   |                   |        | 2.1.4.3 Active quenching, comparator based readout . | 40 |

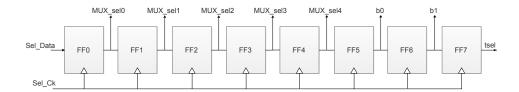

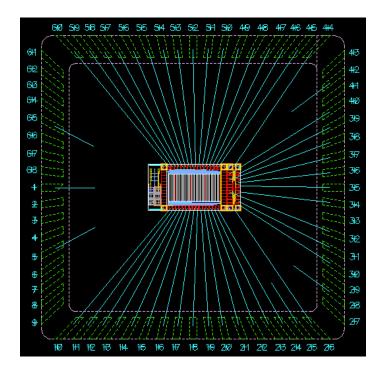

|   |                   | 2.1.5  | Bonding diagram and pin description                  | 41 |

|   | 2.2               | Measu  | irement system                                       | 43 |

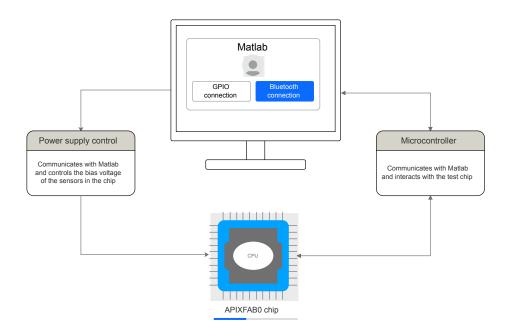

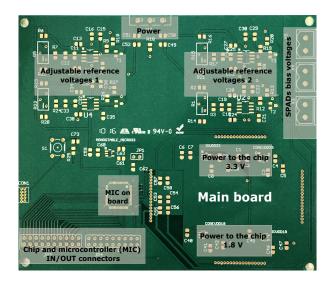

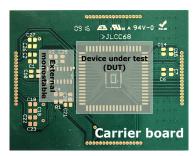

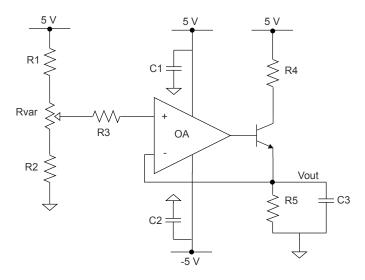

|   |                   | 2.2.1  | Main and carrier boards                              | 45 |

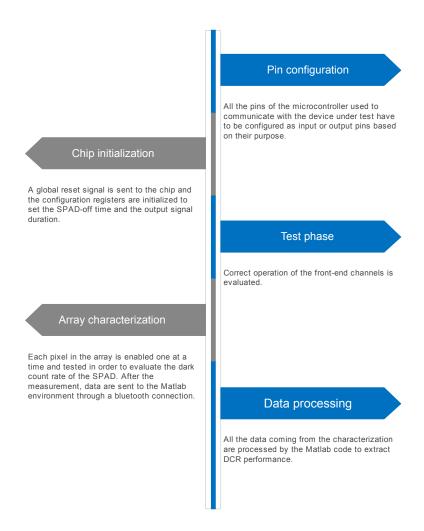

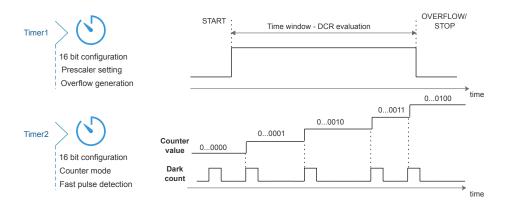

|   | 2.3               | DUT    | test program for DCR evaluation                      | 47 |

|   | 2.4               | Chapt  | ter related work                                     | 54 |

ii CONTENTS

| 3 | $\mathbf{AP}$     | IXFAB            | 0 chara    | cterization results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>55</b> |

|---|-------------------|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   | 3.1               | Pre-irr          | adiation   | tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55        |

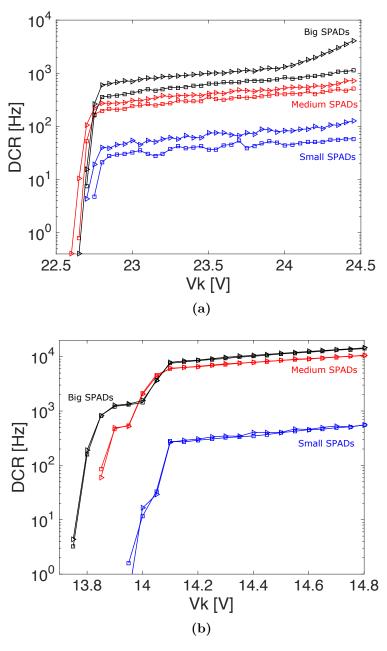

|   |                   | 3.1.1            | DCR me     | easurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55        |

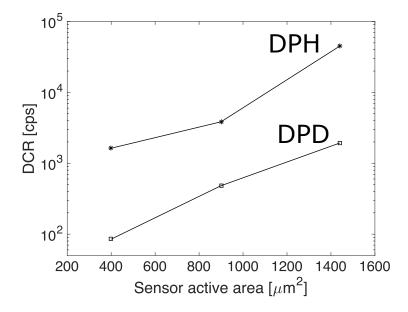

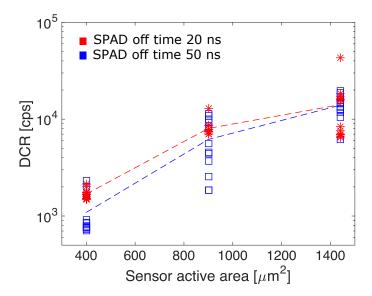

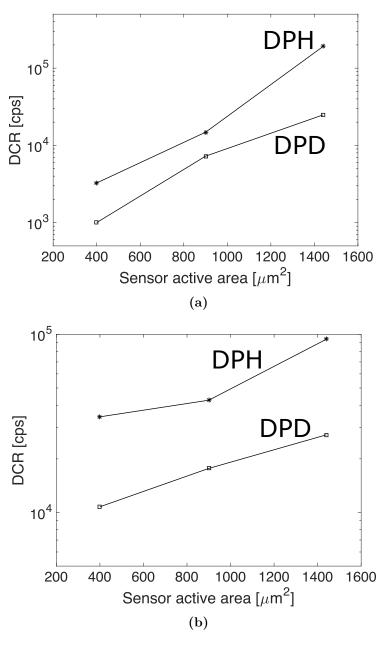

|   |                   |                  | 3.1.1.1    | DCR vs active area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56        |

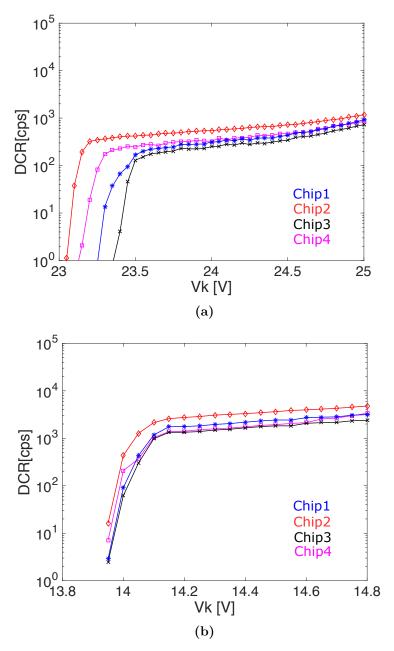

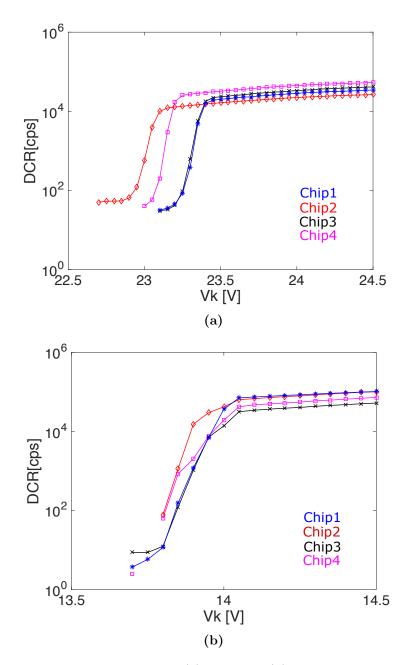

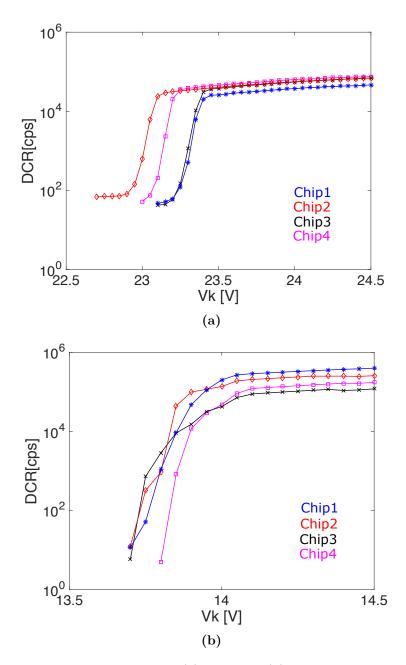

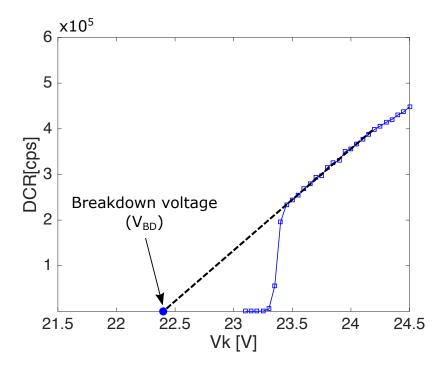

|   |                   |                  | 3.1.1.2    | DCR vs bias voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58        |

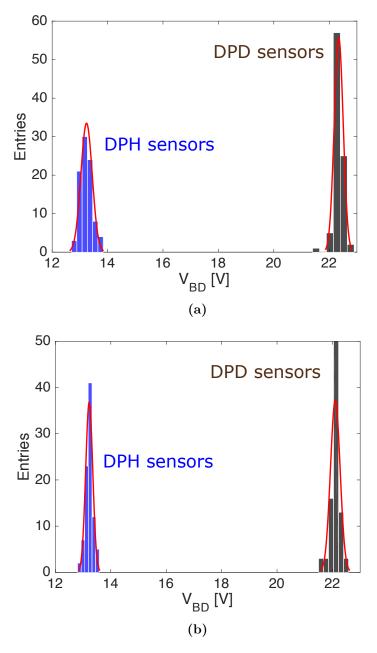

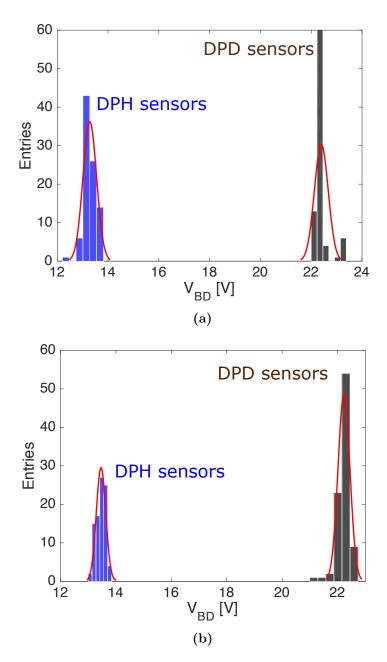

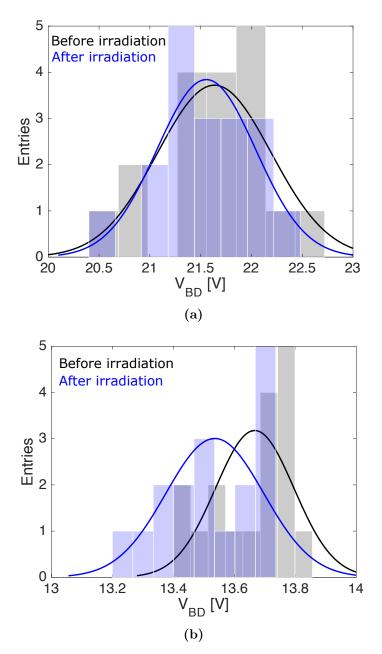

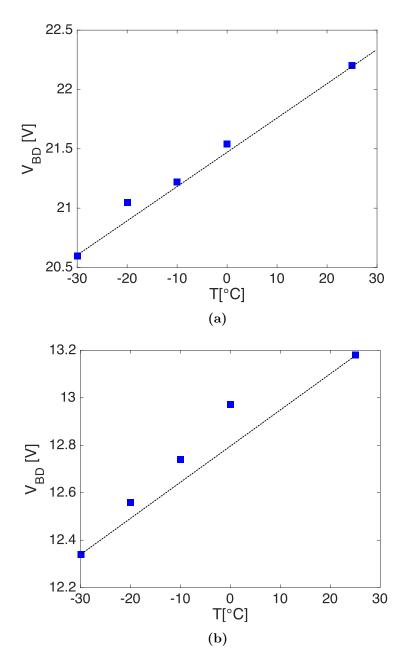

|   |                   | 3.1.2            | Breakdo    | own voltage distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60        |

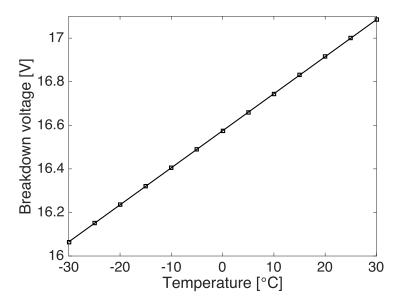

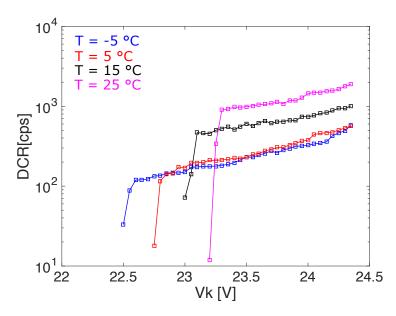

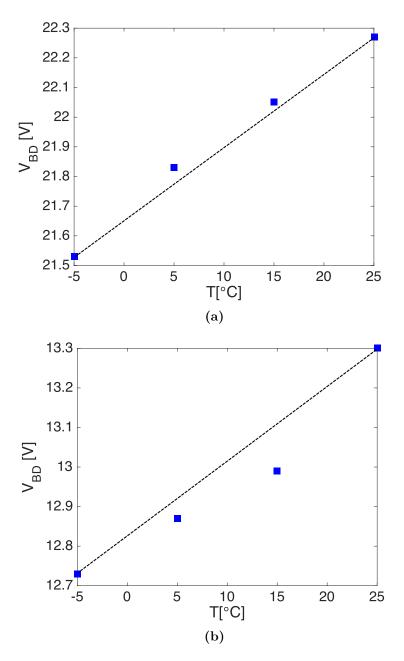

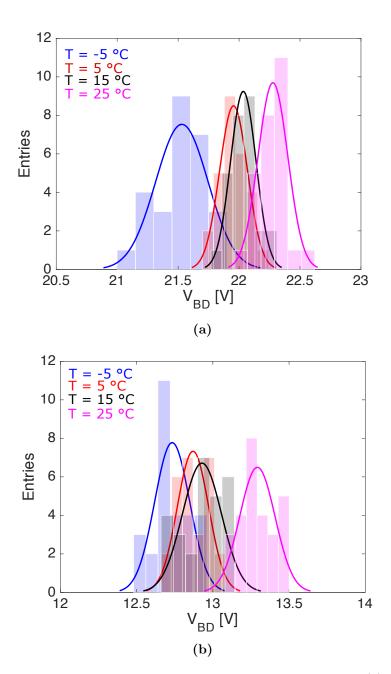

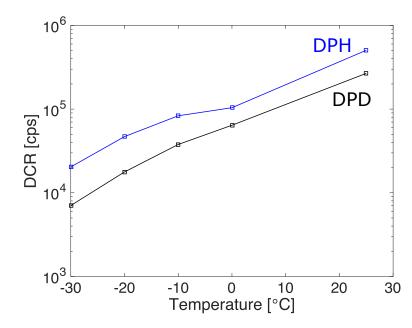

|   |                   | 3.1.3            | Tempera    | ature tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73        |

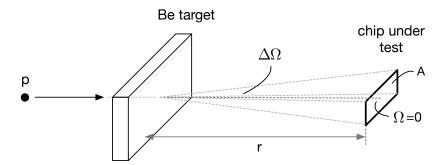

|   | 3.2               | Irradia          | _          | paigns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 77        |

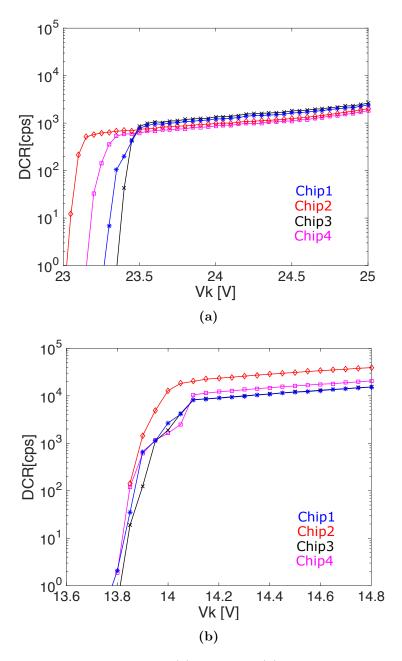

|   |                   | 3.2.1            |            | nizing dose effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78        |

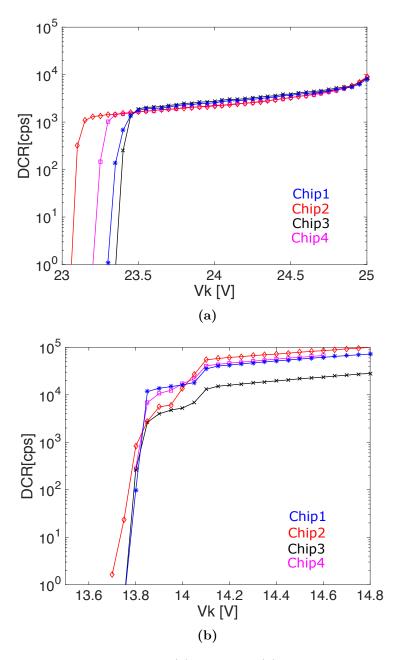

|   |                   | 3.2.2            | Neutron    | irradiation effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81        |

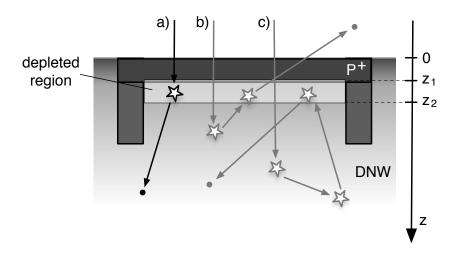

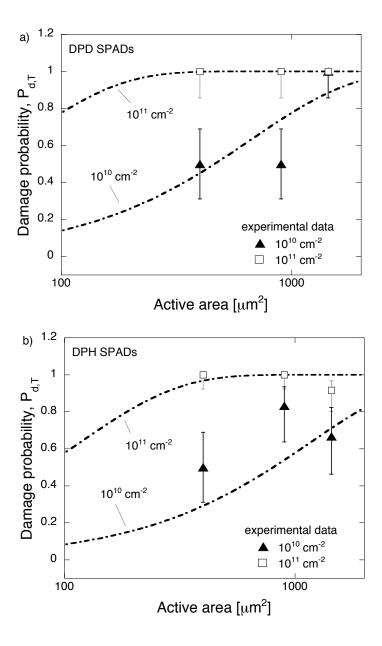

|   |                   |                  | 3.2.2.1    | Model for damage probability in neutron-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|   |                   |                  |            | irradiated SPADs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82        |

|   |                   |                  | 3.2.2.2    | Damage probability for a single incident neutron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82        |

|   |                   |                  | 3.2.2.3    | Damage probability for a given source spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|   |                   |                  | 3.2.2.4    | Model validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88        |

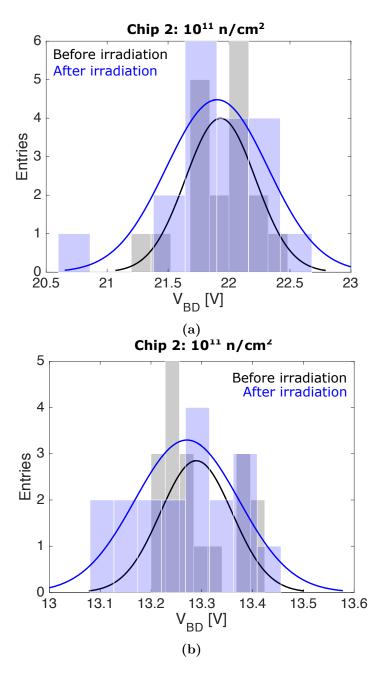

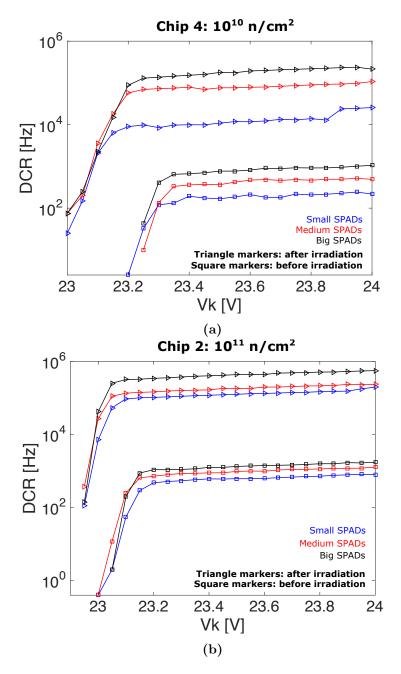

|   |                   |                  | 3.2.2.5    | Effects on breakdown voltage and DCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90        |

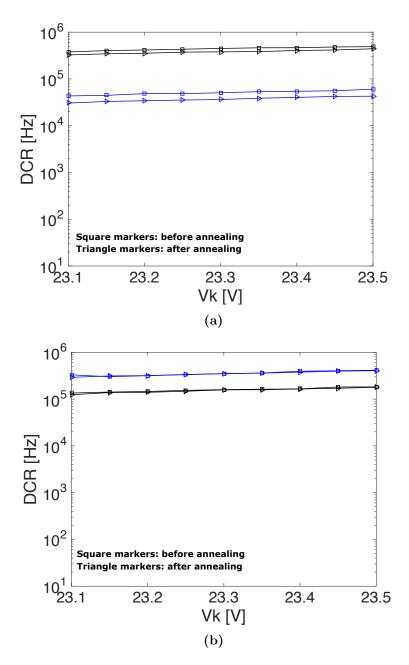

|   |                   |                  | 3.2.2.6    | Annealing procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93        |

|   |                   |                  | 3.2.2.7    | Temperature tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93        |

|   | 3.3               | Chapte           | er related | l work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97        |

| 4 | ΑP                | i <b>X2</b> : ch | ip desig   | 'n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98        |

| _ | 4.1               |                  |            | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98        |

|   | 4.2               | _                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101       |

|   | 4.3               |                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103       |

|   | 1.0               | 4.3.1            |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104       |

|   |                   | 4.3.2            |            | a contract of the contract of | 105       |

|   | 4.4               | 1.0.=            | ructures   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106       |

|   | 4.5               |                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108       |

|   | 1.0               | 4.5.1            | _          | <i>v</i> 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 109       |

|   |                   | 4.5.2            |            | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109       |

|   |                   | 4.5.3            |            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 110       |

|   | 4.6               |                  | _          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110       |

|   | $\frac{4.0}{4.7}$ |                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110       |

## Introduction

Charged particle tracking applications at future colliders call for high granularity, low material budget, low power consumption, high spatial and time resolution and radiation hardness. In order to satisfy such severe requirements, the particle physics community, on the one hand, is trying to update well established technologies, like hybrid pixel and monolithic detectors, on the other, is exploring new solutions overcoming the intrinsic limitations of the older ones. Hybrid pixels can provide good granularity and have been and will be leveraged in the LHC (large hadron collider) experiments and in their planned upgrades. The main issue in using this kind of technology consists in the relatively large amount of material they add in the sensitive region of the experiment. Thinning them down, while reducing the material budget in the detection region, also affects the signal to noise ratio by reducing the amount of collected charge. Monolithic detectors, integrating the front-end electronics in the same substrate as the sensor, can provide a good trade-off between power dissipation, granularity and material budget. Moreover, they can be thinned down to a few tens of microns still providing good signal to noise ratio.

The properties of SPADs (single photon avalanche diodes), mostly employed in the photon detection domain in applications such as optical ranging, fluorescence lifetime imaging, positron emission tomography and Raman spectroscopy, may actually be beneficially exploited for charged particle tracking. SPADs can provide huge internal gain, with no need for pre-amplification (therefore reducing power dissipation) and high spatial resolution. Moreover, the amount of detector material can be substantially reduced, as the sensitive volume of a SPAD is limited to the very thin depleted region around the p-n junction. Use of a CMOS technology for the design and fabrication of the sensor lends itself naturally to the monolithic integration of the processing electronics with the sensing element. On the other hand, noise, in the form of random generation of dark current pulses, is one basic characteristic of avalanche diodes potentially jeopardizing their use as charged particle detectors.

2 INTRODUCTION

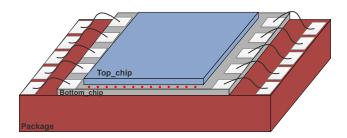

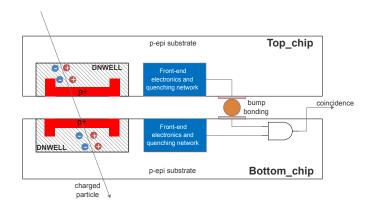

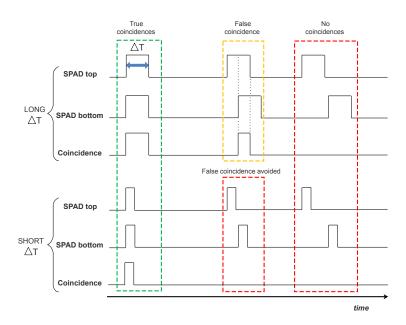

This thesis work presents the development of a new type of silicon sensor for charged particle detection, with emphasis on the device characterization and on the implementation of the measurement system. The work that will be presented in the next chapters has been carried out in the framework of the APiX2 project funded by the Italian Institute for Nuclear Physics (INFN). The aim of the APiX2 project is to develop, in a monolithic structure, an innovative position-sensitive pixelated sensor based on the vertical integration of SPADs.

The first chapter begins with a description of avalanche photodetectors (APD), discussing their working principle and their two different operating regions, focusing in particular on the Geiger-mode detector, which is another name of a SPAD. Different techniques to manage the signal provided by the sensor are presented together with a definition and discussion of the Dark Count Rate (DCR) and breakdown voltage parameters. As a final part of the chapter, more details about the APiX2 project will be provided.

The second chapter is focused on the description and characterization of a test chip designed to evaluate the features of one of the technologies investigated within the APiX2 project. First the chip, consisting of an array of SPADs with integrated front-end electronics, is described. Then, the automated measurement setup used for the chip characterization is discussed.

The third chapter is focused on the results obtained in terms of DCR curves and breakdown distribution. The data presented in the chapter will also include the outcome of an irradiation campaign performed to evaluate its radiation tolerance. The effect of temperature on the DCR has also been investigated, both before and after irradiation.

The fourth and last chapter deals with the description of a new chip designed to implement the dual tier concept proposed by the APiX2 project. The design results from the outcomes of the characterization of the first chip and of other circuits developed within the APiX2 collaboration. In particular, in this chapter, the main features of the new chip are presented together with a description of the integrated electronics, with an emphasis on the most important improvements on previous versions of SPAD arrays.

### Chapter 1

## SPADs and the APiX2 project

Continuous evolution and progress in science requires a costant refinement of sophisticated experimental techniques.

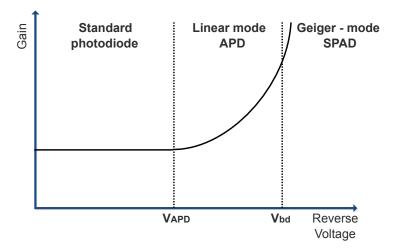

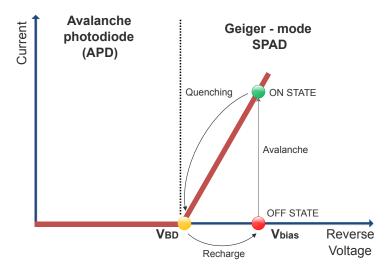

In photon counting applications, for many years, non solid-state vacuum-based devices, such as Micro Channel Plates (MCP) and Photo Multiplier Tubes (PMT), have been adopted owing to their very good performance in terms of noise and sensitivity, spatial resolution and timing characteristics. On the other hand they suffer from limitations mainly originating from their high operation voltage, large power consumption and high cost [1]. The turning point in photon detection applications happened when solid-state avalanche sensors were discovered and became available. Avalanche photodiode (APD) technologies introduce a way of counting photons at a microscopic scale and with the possibility to develop powerful techniques in light detection at the highest level of sensitivity: the single photon. Sensors with these properties, called Single Photon Avalanche Diodes (SPADs), offer an excellent timing resolution [2] and, due to this, are considered the natural candidates for the next generation of photon detectors in which high time resolution is one of the main specifications.

Charged particle tracking systems, mainly based on hybrid pixel technology, have been originally developed for physics applications in which collisions at high-energy may produce particles whose direction, identity and energy need to be measured. In these applications, hundreds of particles need to be simultaneously detected with micrometer spatial resolution and nanosecond timing precision. Use of such advanced devices is now extending to other fields, like imaging of heavy charged particles for radiography [3], biology [4] and astron-

omy [5]. The properties of SPADs can be leveraged in charged particle tracking applications, as they have the potential for providing thin, low power and highly sensitive detection systems based on commercial CMOS technology. In this chapter, after a brief presentation of the semiconductor detector operating principle, the SPAD operation is described, together with the signal processing techniques. The main characterizing parameters concerning single photon avalanche sensors are then discussed, focusing, in particular, on shot-noise and breakdown voltage. The last part of the chapter is dedicated to discussing the goal of the APiX2 project, which consists of developing a dual-layer charged particle detector based on SPAD sensors.

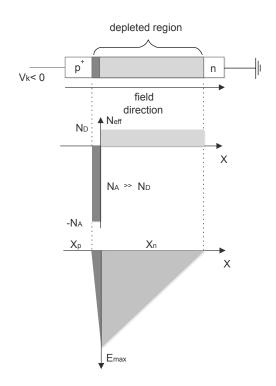

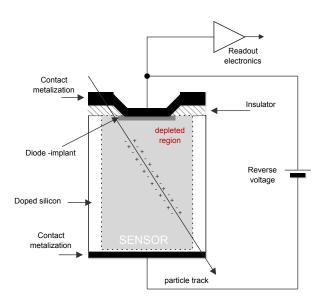

#### 1.1 Operating principle of semiconductor detectors

In a radiation detection system, the sensor is that part delivering the signal to the readout electronics as a consequence of the interaction of a particle with it. Photodiodes are the most common and versatile semiconductor-based sensors used in optoelectronic systems [6]. They consist in a reverse biased p-n junction which can also be operated at high electric fields, in that case achieving an internal gain. By solving the Poisson equation at a p-n junction, it is possible to calculate the width of the depletion region, which is the actual sensitive volume of the detector, and the electric field as a function of the applied voltage. In particular, the width of the depletion region is given by

$$W = x_n + x_p = \sqrt{\frac{2\epsilon_0 \epsilon_{Si}}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) (V_{bi} - V_k)},$$

(1.1)

where  $x_n$  and  $x_p$  represent the width of the depletion region in the n- and p-side of the junction respectively,  $N_D$  is the concentration of donors,  $N_A$  the concentration of acceptors,  $V_k$  is the applied voltage, q is the elementary charge,  $\epsilon_0$  and  $\epsilon_{Si}$  are the vacuum and silicon permittivity respectively and  $V_{bi}$  is the built-in voltage,

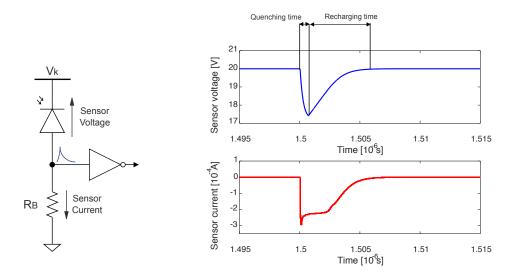

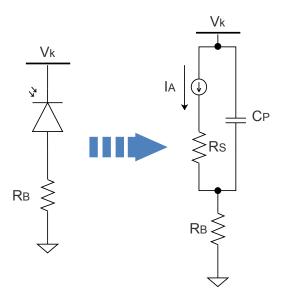

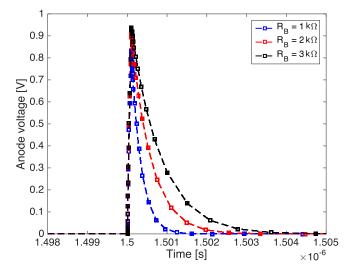

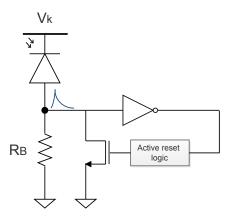

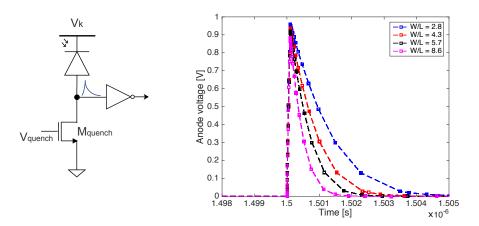

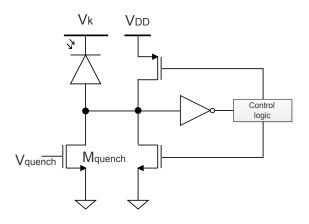

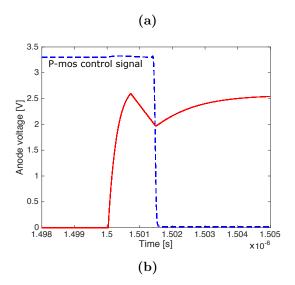

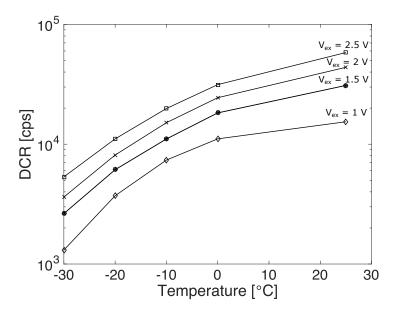

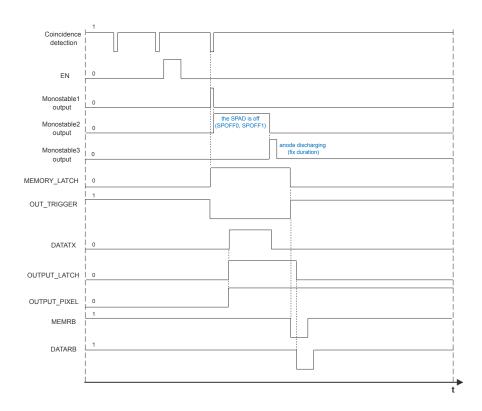

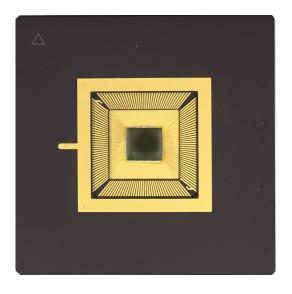

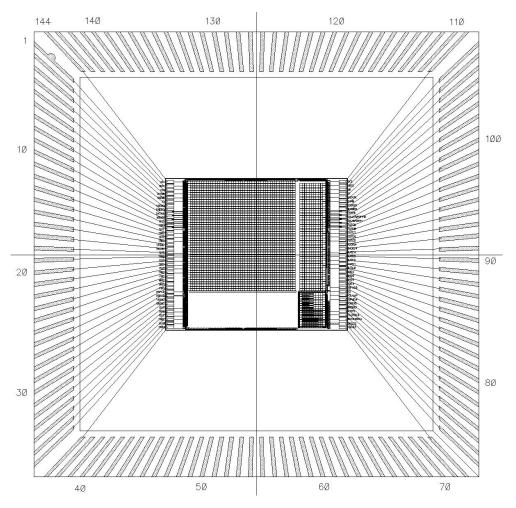

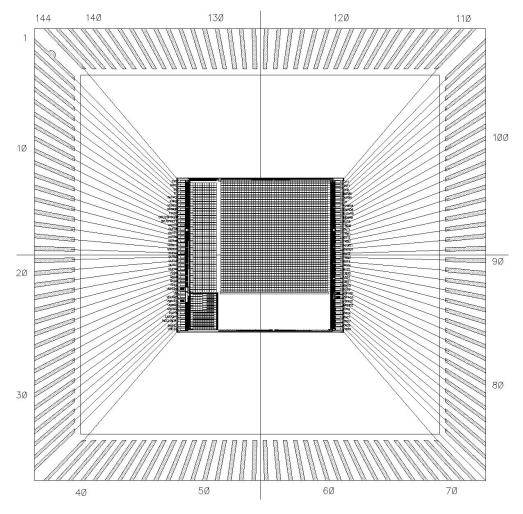

$$V_{bi} = \frac{kT}{q} ln \left( \frac{N_D N_A}{n_i^2} \right). \tag{1.2}$$