### UNIVERSITY OF PAVIA

# Department of Electrical, Computer and Biomedical Engineering

Ph.D. School in Microelectronics

# D-BAND AMPLIFIERS IN SiGe BiCMOS FOR WIRELESS BACKHAUL IN 5G and BEYOND

Ph.D. Thesis of Ibrahim PETRICLI XXXIII Cycle

Supervisor: Prof. Andrea MAZZANTI

To my family

#### ACKNOWLEDGEMENTS

Arriving to this phase of my life wouldn't have been possible without the presence of certain individuals. I would like to present my humble gratitude in this page.

I would like to thank my supervisor Prof. Andrea Mazzanti for this research opportunity and also for his motivative guidance and support starting from my M.Sc. degree, which is comprising 20% of my life.

I would like to thank Ahmet Caglayan and Cansu Telkes for their life time friendship.

I would like to thank my colleagues and friends expatriate scientists Dr. Alper Akdikmen, Dr. Farshad Piri and Mustafa Oz for their presence, coffee breaks and "molto più".

I want to thank all the colleagues in Analog Integrated Circuits laboratory.

Last but not least, I want to thank each of my family member for their endless support and their belief in me.

### TABLE OF CONTENTS

| <u>P</u>                                                              | age |

|-----------------------------------------------------------------------|-----|

| Acknowledgements                                                      | v   |

| Table of Contents                                                     |     |

| List of Figures                                                       |     |

| Abstract                                                              |     |

| 1. Introduction                                                       | 1   |

| 1.1 Motivation                                                        | 1   |

| 1.2 Thesis Organization                                               | 5   |

| 2. Design of Compact D-Band Amplifiers with Lumped Components         |     |

| 2.1 Validation of Simulation Flow and Technology                      | 8   |

| 2.2 Single-Ended Amplifier Designs                                    | 10  |

| 2.2.1 Circuit Design                                                  | 10  |

| 2.2.2 Inductors and Current Return Path                               | 12  |

| 2.2.3 Experimental Results                                            | 16  |

| 2.3 Differential Amplifier Designs                                    | 17  |

| 2.3.1 Circuit Design                                                  | 17  |

| 2.3.2 Experimental Results                                            | 20  |

| 2.4 Conclusion                                                        | 22  |

| 3. Analysis and Design of Wideband Amplifiers for D-Band Applications | 25  |

| 3.1 Introduction                                                      | 25  |

| 3.2 Review of Common-Emitter and Cascode Gain Stages                  | 26  |

| 3.3 Anaylsis of Cascode Output Matching Network                       | 29  |

| 3.3.1 Lossless Matching Network                                       | 30  |

| 3.3.2 Matching Network with Lossy Components                          |     |

| 3.3.3 Comparison with Simulations                                     | 34  |

| 3.4 Design of Amplifiers                                              | 36  |

| 3.5 Experimental results                                              | 42  |

| 3.6 Conclusion                                                        | 44  |

| 4. Design of D-Band Power Amplifiers with Enhanced PAE                | 45  |

| 4.1 Introduction                                                      | 45  |

| 4.2 Current Clamping                                                  | 46  |

| 4.3 Circuit Design                                                    | 47  |

| 4.4 Experimental Results                                              | 50  |

| 4.5 Conclusion                                                        | 53  |

| Conclusion                                                            | 55  |

| Appendix                                               | 57 |

|--------------------------------------------------------|----|

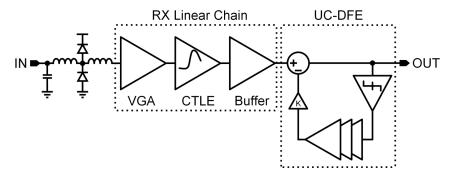

| A.1 - A 112 Gb/s PAM-4 RX Front-End with Unclocked DFE |    |

| 1.1 Introduction                                       | 57 |

| 1.2 RX Linear Chain and CTLE                           | 58 |

| 1.3 Unclocked DFE                                      | 60 |

| 1.3.1 Adder                                            | 62 |

| 1.3.2 Comparators                                      | 62 |

| 1.3.3 Delay Cell                                       | 64 |

| 1.4 Results                                            | 66 |

| 1.5 Conclusion                                         | 69 |

| References                                             | 71 |

### LIST OF FIGURES

|                                                                                                               | Page  |

|---------------------------------------------------------------------------------------------------------------|-------|

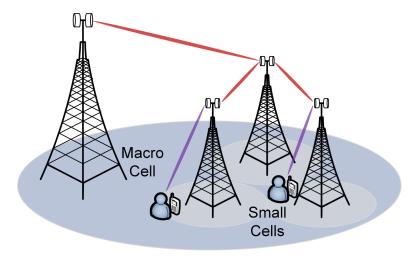

| Figure 1.1: Macro cell and small cells backhaul connections                                                   | 1     |

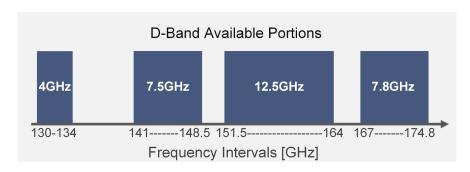

| Figure 1.2: Reserved non-contiguous spectrum blocks for fixed wireless                                        |       |

| services [8]                                                                                                  | 2     |

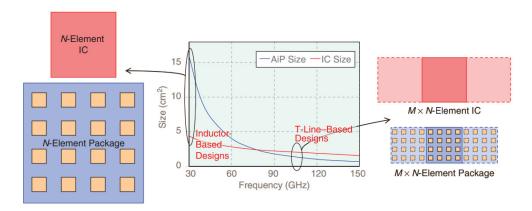

| <b>Figure 1.3</b> : The challenge of fitting the ICs in the antenna array footprint [10].                     | . 3   |

| Figure 1.4: Maximum power added efficiencies for SiGe and CMOS PAs in                                         |       |

| literature                                                                                                    | 4     |

| Figure 2.1: De-embedding structures for MOM Capacitor and CE HBT                                              | 8     |

| Figure 2.2: (a) BEOL of the technology, (b) Simulation strategy for CE HBT.                                   | 8     |

| <b>Figure 2.3</b> : Comparison of EM simulation and de-embedded measurements:                                 |       |

| (a) Capacitance of MOM capacitor (top), quality factor of MOM                                                 |       |

| capacitor (bottom), (b) maximum available gain of transistor in                                               |       |

| common emitter configuration.                                                                                 | 9     |

| <b>Figure 2.4</b> : (a) 1-stage and (b) 2-stage amplifiers schematic. $x_{gnd}$ , coupled                     |       |

| with nearby inductors, represents current return paths                                                        |       |

| <b>Figure 2.5</b> : Chip microphotograph of the (a) 1-stage and (b) 2-stage amplifiers                        | s. 12 |

| <b>Figure 2.6</b> : (a) 3D View of Stacked Capacitor (b) Simplified Model (c)  Z  vs                          |       |

| Frequency.                                                                                                    | 12    |

| Figure 2.7: Inductor layout with current density from EM simulations. (a)                                     |       |

| 3- terminal without shielding, (b) 3-terminal with a surrounding                                              | 12    |

| metal layer, (c) 4-termianl to include current return path                                                    | 13    |

| <b>Figure 2.8:</b> Equivalent circuit models reproducing EM simulations for the three situations in Fig. 2.7. | 13    |

| Figure 2.9: Equivalent inductance from EM-simulations (dotted lines) and                                      | ,. 13 |

| lumped circuit models (solid lines) for the three situations in Fig. 2.7                                      | 7 15  |

| Figure 2.10: 1-stage amplifier measurement and comparison with simulations.                                   | . 13  |

| (sim.(a): unshielded inductors and lumped ground, sim.(b):                                                    |       |

| shielded inductors and lumped ground, $sim.(c)$ : shielded inductors                                          |       |

| and current return paths included).                                                                           | 16    |

| <b>Figure 2.11:</b> 2-stage amplifier measurement and comparison with simulations.                            |       |

| (sim.(a): unshielded inductors and lumped ground, sim.(b):                                                    |       |

| shielded inductors and lumped ground, sim.(c): shielded inductors                                             |       |

| and current return paths included).                                                                           | 17    |

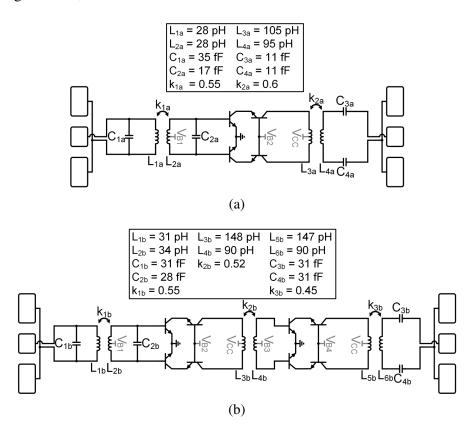

| Figure 2.12: Schematic of (a) 1-stage amplifier, (b) 2-stage amplifiers                                       | 18    |

| Figure 2.13: Layout of the input matching network of one-stage amplifier                                      | 19    |

| Figure 2.14: Layout of the transformer in 2-stage amplifier.                                                  | 20    |

| Figure 2.15: Chip microphotograph of the (a) 1-stage and (b) 2-stage                         |            |

|----------------------------------------------------------------------------------------------|------------|

| differential amplifiers.                                                                     | 21         |

| Figure 2.16: S-Parameter comparison of measurement and simulation for                        |            |

| one-stage amplifier.                                                                         | 21         |

| Figure 2.17: S-Parameter comparison of measurement and simulation for                        |            |

| two-stage amplifier                                                                          | 22         |

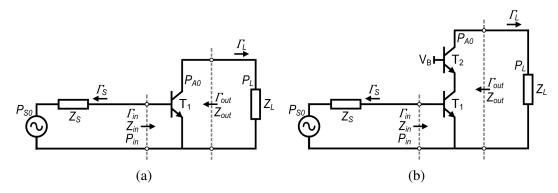

| Figure 3.1 : Common emitter (a) and cascode (b) gain stages                                  | 27         |

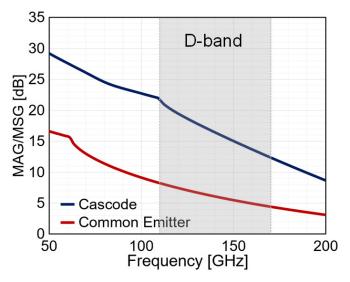

| Figure 3.2: MAG/MSG versus frequency for the common emitter and                              |            |

| cascode active stages                                                                        | 27         |

| Figure 3.3 : Optimal source and load impedances at 150 GHz for the common                    |            |

| emitter and cascode active stages                                                            | 28         |

| <b>Figure 3.4</b> : Equivalent circuit of the cascode stage driven by $Z_{S-opt}$ and with   |            |

| matching toward the equivalent impedance at the GSG pad                                      | 29         |

| <b>Figure 3.5</b> : Circuit schematic used to validate the analysis with simulations         | 35         |

| Figure 3.6 : Comparison of calculation with simulation for (a) lossless, (b)                 |            |

| lossy matching network, Normalized gain and bandwidth                                        | 35         |

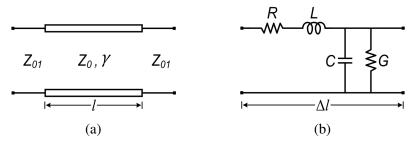

| Figure 3.7: (a) Tline 2-port network, (b) distributed-element circuit model of               |            |

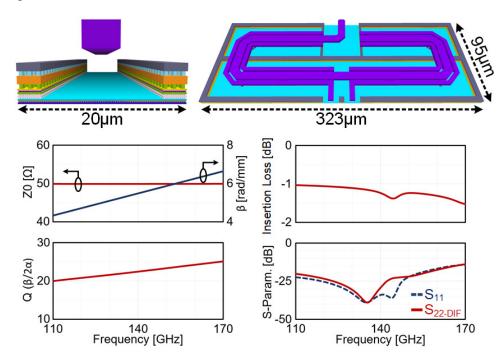

| a Tline                                                                                      | 36         |

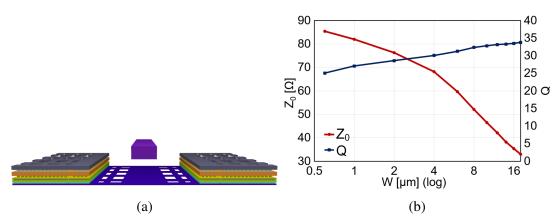

| Figure 3.8: (a) Cross section of the shielded microstrip TLINE, (b)                          |            |

| characteristic impedance and quality factor vs the width of the                              |            |

| signal trace.                                                                                | 38         |

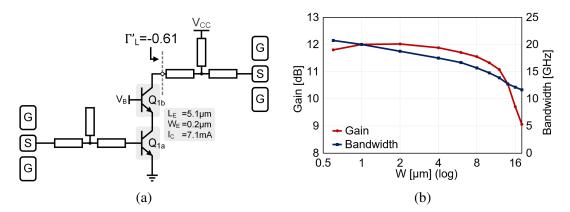

| Figure 3.9: (a) Schematic of single-stage amplifier, (b) Peak gains at 150 GHz               |            |

| and bandwidths for different W values.                                                       | 39         |

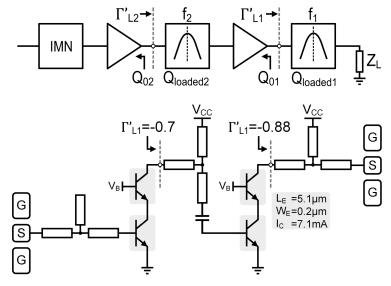

| <b>Figure 3.10:</b> Schematic of 2-stage amplifier.                                          | 39         |

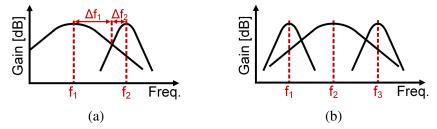

| Figure 3.11: Peaking frequencies and relative positions for (a) 2-stage, (b)                 | 40         |

| 3-stage amplifier.                                                                           | 40         |

| Figure 3.12: Schematic of 3-stage amplifier.                                                 | 41         |

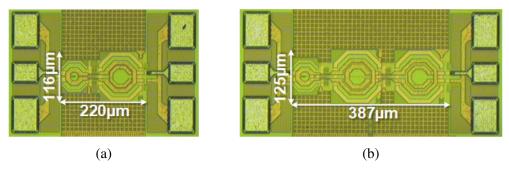

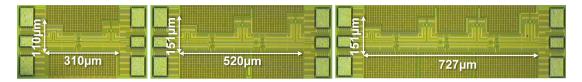

| <b>Figure 3.13:</b> Chip microphotographs of 1- (left), 2- (center) and 3-stage (right)      | 4.0        |

| amplifiers                                                                                   | 43         |

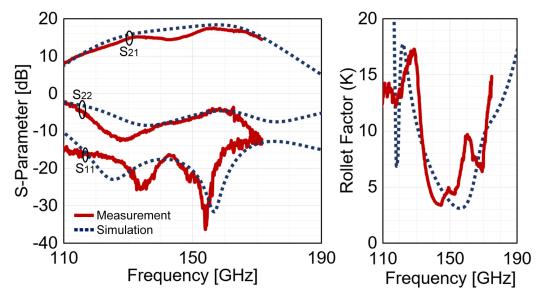

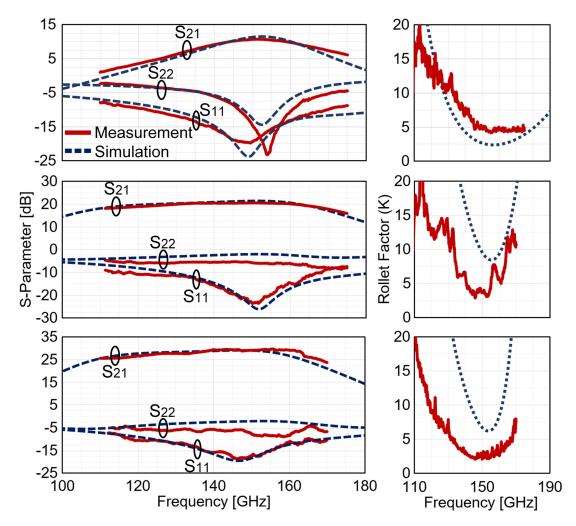

| <b>Figure 3.14:</b> S-Parameter results for 1- (top), 2- (center) and 3-stage (bottom)       | 40         |

| amplifiers                                                                                   | 43         |

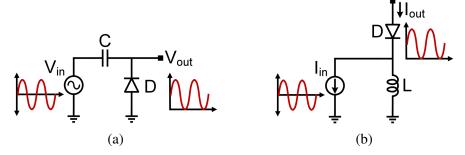

| Figure 4.1: (a) Voltage-mode, (b) current-mode diode clamping circuits                       | 46         |

| <b>Figure 4.2:</b> The implementation of current-mode clamping on CB transistor,             | 4.0        |

| and current waveforms.                                                                       | 46         |

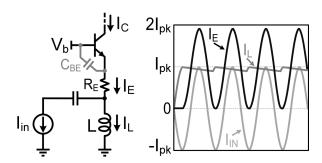

| Figure 4.3: Schematic of the single-ended PA.                                                | 47         |

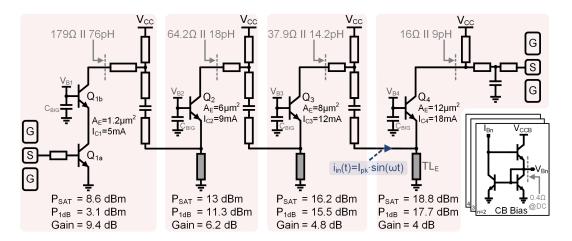

| <b>Figure 4.4</b> : (a) G <sub>P</sub> and load-pull circles, (b) dynamic load lines for the | 40         |

| transistor in the output stage.                                                              | 48         |

| Figure 4.5 : Characteristics of T-Line and balun.                                            | 49         |

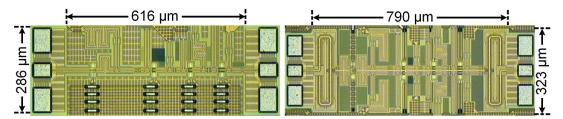

| <b>Figure 4.6</b> : Chip microphotographs of the single-ended (left) and differential        | <b>~</b> ^ |

| (right) PAs.                                                                                 | 50         |

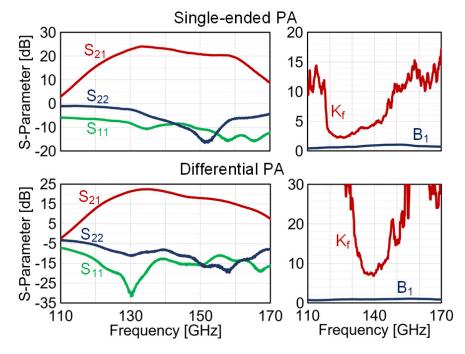

| <b>Figure 4.7:</b> Measured S-parameters and stability-factors for single-ended and          | <b>~</b> ^ |

| differential PAs.                                                                            | 50         |

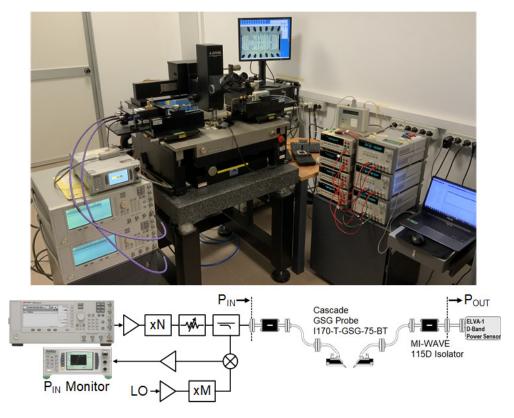

| Figure 4.8: Large-signal measurement setup                                                   |            |

| Figure 4.9: Measured large signal performance.                                               | 52         |

| Figure 4.10: | The DC current of the different stages in single-ended PA              | 53 |

|--------------|------------------------------------------------------------------------|----|

| Figure 4.11: | Reliability test for single-ended PA                                   | 53 |

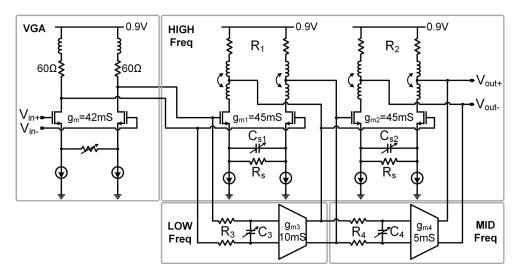

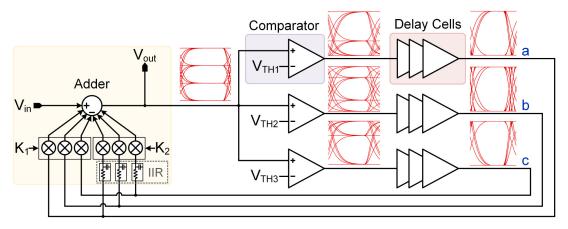

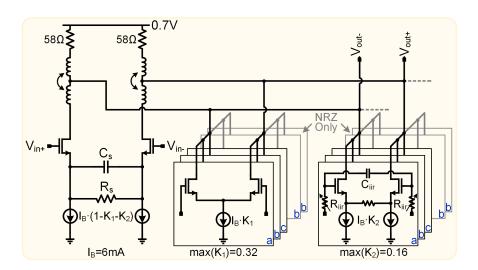

| Figure 5.1:  | Proposed Analog Front-end Architecture                                 | 58 |

| Figure 5.2:  | Schematic of VGA and Continuous Time Linear Equalizer                  | 59 |

| Figure 5.3:  | Frequency Response of CTLE from post-layout simulations                | 59 |

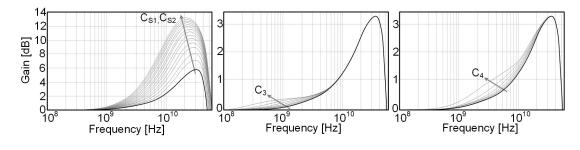

| Figure 5.4:  | Pulse responses of Channel, DT-tap and IIR-tap                         | 61 |

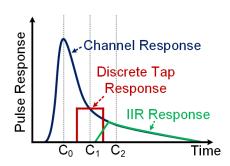

| Figure 5.5:  | UC-DFE block diagram.                                                  | 61 |

| Figure 5.6:  | Schematic of the adder                                                 | 62 |

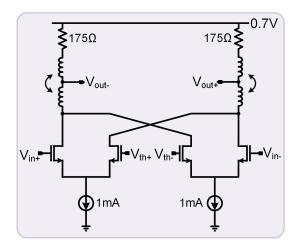

| Figure 5.7:  | Schematic of a comparator.                                             | 63 |

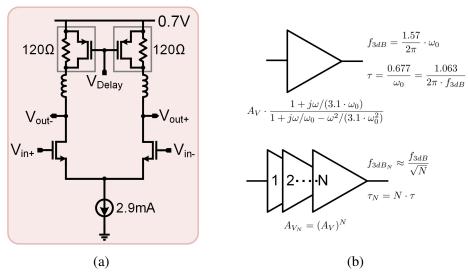

| Figure 5.8:  | (a) Schematic of the amplifier used in the delay cells. (b) Transfer   |    |

|              | function and group-delay of a single stage and multi-stage amplifiers. | 64 |

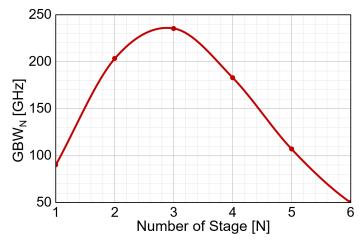

| Figure 5.9:  | Gain-Bandwidth product of cascaded amplifiers featuring 12 ps          |    |

|              | group delays.                                                          | 65 |

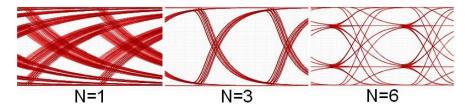

| Figure 5.10: | Eye diagrams for delay cells with a different number of stages         | 66 |

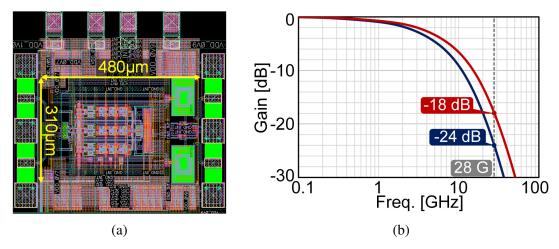

| Figure 5.11: | (a) Layout of the RX front-end with the UC-DFE. (b) The channel        |    |

|              | transfer functions.                                                    | 66 |

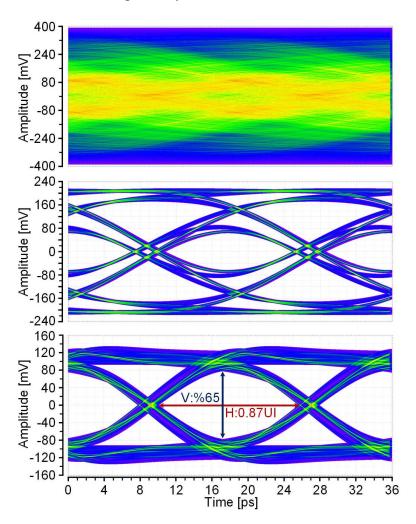

| Figure 5.12: | 56 Gb/s eye diagrams with 24 dB channel loss: input signal (top),      |    |

|              | CTLE output (middle), signal after UC-DFE correction (bottom)          | 67 |

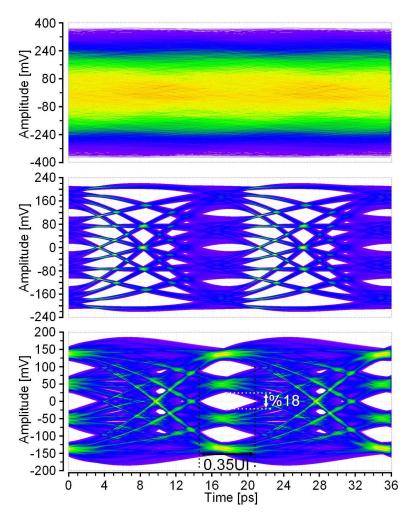

| Figure 5.13: | 112 Gb/s eye diagrams with 18 dB channel loss: input signal            |    |

|              | (top), CTLE output (middle), signal after UC-DFE correction            |    |

|              | (bottom)                                                               | 68 |

#### **ABSTRACT**

The never ending demand for wider bandwidth, coupled with the evolution of technology, drives the progress of silicon ICs beyond 100 GHz. The wide available spectrum in D-band, 60 GHz centered at 140 GHz, is being considered for enhanced resolution radars and wireless transceivers with a fiber-like transport capacity, key for network deployment in 5G and beyond [1].

Amplifiers are the key building blocks in wireless transceivers, i.e., in receivers low noise amplifiers restore adequate amplitude before frequency conversion and in transmitters power amplifiers drive the antenna with sufficient power in a most efficient way. Considering the operation of transistors close to  $f_{max}$  of the technology, in D-band, design of amplifiers with sufficient performance is particularly challenging. The Ph.D. activity has been done by following three paths to address different issues:

- (1) Strategies for compact designs, key for phased array systems where fitting the ICs in dedicated radiating antenna element footprint is challenging.

- (2) Design approach for gain-bandwidth-product enhancement, important to ensure the full D-band operation.

- (3) Techniques for efficiency enhancement for power amplifiers in D-band, essential for the most power hungry block.

To this regard, this thesis presents 9 D-band amplifiers, i.e., 7 signal amplifiers and 2 power amplifiers.

First 4 compact D-band amplifiers use lumped elements in matching networks. In the first two single ended designs, to correctly account for the effects of a non-ideal ground plane, i.e., reactances in current return paths, and coupling of inductors with nearby layout structures, a shielded 2-port, 4-terminal simulation strategy for inductors is proposed and validated by measurements. The approach allows very accurate design of compact amplifiers in D-band. The 1-stage design proves 11.8 dB gain at 152 GHz and 17.9 GHz bandwidth in 0.031 mm<sup>2</sup>. With the 2-stage amplifier, featuring 20.1 dB gain at 150 GHz with 24.5 GHz bandwidth in 0.058 mm<sup>2</sup>, from 2× to 5.7×

area reduction is demonstrated against similar SiGe amplifiers in the same frequency band. In the next two designs, the differential topology is developed for robustness against parasitic effects of the non-ideal ground, a key issue with lumped components at high frequency. The 1-stage amplifier reaches 8 dB gain at 156 GHz and 17.8 GHz bandwidth in 0.026 mm<sup>2</sup> silicon area. The 2-stage amplifier displays 17.4 dB gain at 157 GHz with 42.7 GHz bandwidth in 0.048 mm<sup>2</sup>. Compared to previously reported SiGe amplifiers in similar frequency range, more than 2× core area reduction is demonstrated at comparable gain-bandwidth product.

The last three designs uses transmission lines in matching networks. For designed amplifiers, simple, closed-form equations for gain and bandwidth as a function of the load reflection coefficient are derived. Leveraging the results of the analysis, which can be also applied to the lumped-element approach, a single-stage and multi stage stagger-tuned amplifiers are implemented in a SiGe BiCMOS technology. Two-and three-stage amplifiers demonstrate more than  $60\,\mathrm{GHz}$  bandwidth with  $20\,\mathrm{dB}$  and  $28\,\mathrm{dB}$  gain respectively, corresponding to  $700\,\mathrm{GHz}$  and  $1.7\,\mathrm{THz}$  gain-bandwidth product. Normalizing gain and bandwidth to the number of stages and technology  $f_{max}$ , the resulting Figure of Merit is remarkably higher than previously reported silicon amplifiers in the same band.

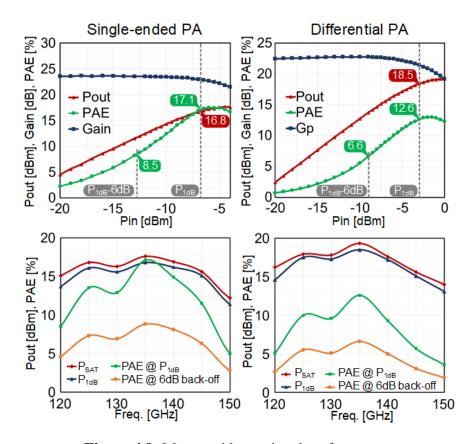

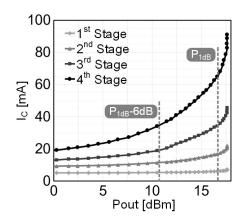

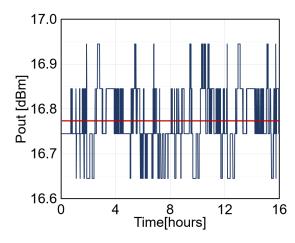

The power amplifiers (PAs) are designed in a single-ended and differential fashion. The PAs exploit the remarkable features of common-base stages to enhance power-added-efficiency in the linear PA operating region. A single-ended PA proves  $P_{1dB}$  =16.8 dBm with  $P_{SAT}$  = 17.6 dBm at 135 GHz. The PAE at  $P_{1dB}$  and at  $P_{1dB-6dB}$  are 17.1% and 8.5% respectively. With a differential PA the linear output power is increased to  $P_{1dB}$  =18.5 dBm with  $P_{SAT}$  = 19.3 dBm at 135 GHz. The PAE at  $P_{1dB}$  and at  $P_{1dB-6dB}$  are 12.6% and 6.7% respectively, an improvement of at least 3× against state of the art.

### Introduction

### 1.1 Motivation

The number of wireless devices has been increasing as a consequence of the change in our daily habits, which translates to extensive growth in data traffic. According to [2], 5G subscriptions are anticipated to surpass 849 million by 2025, which corresponds to  $\sim$ 11 gigabytes per user per month. In other words, the mobile network traffic will be tripled by 2025 compared to today's numbers.

To cope with the aforementioned expansion, wireless infrastructures keep continue to evolve with the next generation of cellular networks. Considering the anticipated data traffic demand, 5G network standards should have 20 Gbps peak data rate,  $\times 100$  network energy efficiency, and  $10 \,\mathrm{Mbps/m^2}$  area traffic capacity [3], and as a result  $10^3$  -  $10^4$  times the network capacity. To increase the spectral efficiency by means of reusing the same carrier frequency simultaneously, Massive MIMO (Multi-Input Multi-Output) and beam-forming technologies are planned to be used [3].

Figure 1.1: Macro cell and small cells backhaul connections

Having the major part of the world population in the urban areas necessities high number of base station deployments and smaller network cells to increase the

efficiency. To that purpose small-cell architecture has been proposed [4] (Fig.1.1). The macro cell and the small cells can be connected through optical-fiber lines. But the installation cost of fibers is extremely high, and in some areas simply it can't be laid out because of the obstructions. Therefore, the solution is simply to replace the optical-fiber connections with high data-rate wireless connections.

The availability of large bandwidth and high spectrum efficiency is essential, but even if multi-carrier techniques are used, a channel bandwidth as large as 2.5 GHz will be required [5]. This amount of bandwidth can only be provided in millimeter-wave (mmWave) frequency spectrum. To this end, mmWave frequencies have been investigated.

The wide available spectrum in D-band (100-170 GHz) is rapidly gaining interest enabling wireless communication with a fiber-like transport capacity, key for the infrastructure of future cellular networks, i.e., 5G and beyond [1, 6, 7]. Standardization and spectrum allocation are currently in progress. According to ECC recommendations, four non-contiguous spectrum blocks (Fig. 1.2), have been already reserved in the 130 GHz to 174.8 GHz frequency range for fixed wireless services [8].

Figure 1.2: Reserved non-contiguous spectrum blocks for fixed wireless services [8].

Wireless backhaul transceivers must be energy efficient and in a compact size to simplify deployment. Moreover, in view of the increased volumes and system complexity, the adoption of a silicon technology is key. Today, the BiCMOS process, combining CMOS devices for digital functions and bipolar transistors for high-frequency building blocks represent an optimal compromise between costs and performances. Nonetheless, in D-band the implementation of transceivers with acceptable performance is very challenging because of the high operation frequency,

Chapter 1 3

close to the technology limits. To this purpose, several private and public research programs are ongoing. The European projects DREAM [4] and TARANTO [9], where University of Pavia is a partner, are aimed at investigating D-band radio solutions to meet the requirements of wireless backhaul in 5G and beyond. In particular, my Ph.D. activity has been investigation of suitable D-band amplifiers in SiGe BiCMOS technology.

Taking into account transistors operate close to  $f_{max}$ , design of amplifiers with adequate performance is particularly challenging in D-band. This work followed three different paths to address different issues related to design of D-band amplifiers.

The first issue is related to the amplifier's footprint. A massive use of phased array, i.e., hundreds of radiating elements, each one driven by a dedicated front-end, is foreseen to compensate the high path loss and the limited available power from a single element [1]. To this purpose, as depicted in Fig. 1.3, a key challenge beyond 100 GHz is to fit the integrated circuits (ICs) in the area occupied by the antenna array [10]. In fact, the separation between radiating elements is set by the wavelength, but while the area of the antenna array shrinks with the square of the wavelength, the size of the ICs, dominated by the many required amplifiers, is hard to scale proportionally [10] which motivates investigations to shrink the size.

**Figure 1.3**: The challenge of fitting the ICs in the antenna array footprint [10].

The addressed second challenge is providing enough gain over the full bandwidth. Considering 60 GHz overall bandwidth (110-170 GHz) and gain needs of >20 dB, amplifiers must have >600 GHz gain-bandwidth-product (GBW). Distributed amplifiers in SiGe HBT technologies meet the requirement but consume excessive power.

Tuned amplifiers save power but in D-band the design is made challenging by the low available gain of transistors. To this regard, design techniques for GBW enhancement in multi-stage tuned amplifier are investigated.

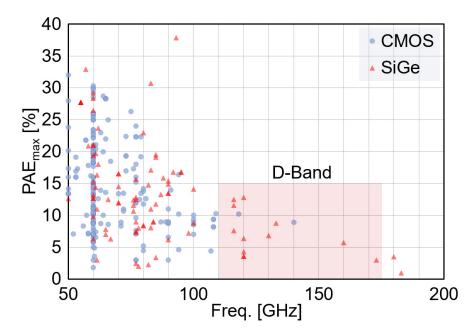

Lastly, the third issue is related to the efficiency of power amplifiers (PAs) in D-band. As depicted in Fig. 1.4, evidenced by the PA survey [11] the average of maximum power added efficiency (PAE<sub>max</sub>) in D-band is  $\sim 6.7\%$ . Moreover, this number reduces in linear operation, i.e., <5% for P<sub>out</sub>=P<sub>1dB</sub>, and <2% for P<sub>out</sub>=P<sub>1dB</sub>-6 dB. As an example, a PA delivering 15 dBm output power with 5% PAE consumes approximately 620 mW DC power. Assuming PAs are employed in 8 × 8 phased array system, the total power consumption in  $\sim 8 \times 8 \text{ mm}^2$  area would be approximately 40 W. Such a high power consumption in a very small area could cause thermal reliability issues. To overcome the problem and increase the linear operation efficiency of PAs in D-band, efficiency enhancement techniques have been proposed.

Figure 1.4: Maximum power added efficiencies for SiGe and CMOS PAs in literature.

Chapter 1 5

### 1.2 Thesis Organization

The activity documented in the rest of the thesis was part of the TARANTO funded program and addresses the issues outlined above for the design of D-band amplifiers in the STMicroelectronics BiCMOS 55 nm tecnology.

The Chapter 2 presents a design and verification strategy for compact D-band amplifiers with matching networks implemented with lumped elements. Different test chips have been realized and measurements prove state-of-the-art performances with remarkable area reduction. The results are published in [12] and [13].

The third chapter analyses wideband amplifiers for D-band communication. A design strategy is proposed leveraging the load reflection coefficient of cascode gain stage to enhance the GBW. Measurements on implemented single and multi-stage amplifiers prove a figure of merit significantly higher than state of the art. The results are submitted to a journal publication entitled "Analysis and Design of D-Band Cascode SiGe BiCMOS Amplifiers with Gain-Bandwidth Product Enhanced by Load Reflection".

The Chapter 4 study the problem of power added efficiency in D-band power amplifiers. The remarkable properties of the common-base stage are studied and applied to the implementation of D-band power amplifiers that demonstrate  $3 \times PAE$  improvement against state of the art. The results are submitted to a letter publication titled "D-band SiGe BiCMOS Power Amplifier with 16.8 dBm  $P_{1dB}$  and 17.1 % PAE Enhanced by Current-Clamping in Multiple Common-Base Stages".

As appendix of the Thesis, an activity carried out in the initial part of my PhD course is summarized. It is related to the design of a serial-link PAM-4 receiver in FinFet technology. The results of this activity are published on a journal paper titled "A 112 Gb/s PAM-4 RX Front-End with Unclocked Decision Feedback Equalizer" [14].

## Design of Compact D-Band Amplifiers with Lumped Components

In D-band, to maximize the gain amplifiers need conjugately matched multiple stages. Apart from few exceptions (e.g. [15]) amplifiers reported so far leverage transmission lines (Tlines) in matching networks [16–20]. The good confinement of the electromagnetic field in Tlines limits coupling and cross-talk issues with nearby components. The structured Tline models account both forward and return current paths, thus make the design robust against the effects of a non-ideal ground plane which is a critical issue at high frequency. However, despite the short wavelength in D-band, Tlines occupy large silicon area and represent the primary limit to scale the size of active circuits.

The amplifiers footprint can be drastically reduced with compact inductors in matching networks, as commonly used in the lower portion of the millimetre-wave band [21]. However, inductors are influenced from coupling with nearby structures in layout. Moreover, unless differential topology is adopted, the effects of current return paths [22, 23] must be carefully accounted in D-band to avoid unpredicted networks mistuning, responsible for frequency shift or loss of the gain.

This chapter starts with the validation of the simulation flow and technology. Even though the technology is well suited for mm-Wave design, we lacked reference measurement results above 100 GHz which brings questions about reliability of the simulation flow. Therefore, pre-validation was seemed to be necessary.

The chapter continues with compact D-band amplifiers with lumped-element matching networks. While having the small silicon area, to handle the aforementioned issue two different solutions are proposed, i.e., accurate modelling of current return paths in the lumped inductors and differential circuit topology. While the details on accurate modelling of inductors and current return paths are given in the single-ended amplifier

design section, differential amplifiers are presented in the section three. Finally, the results are summarized and compared with the state of the art in the conclusion section.

### 2.1 Validation of Simulation Flow and Technology

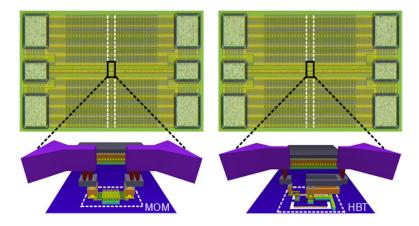

In order to verify the simulations flow against simple measurements, elementary components as well as TRL de-embedding structures (thru, reflect, and line) have been designed and fabricated in STMicroelectronics' 55 nm BiCMOS technology. As an example, Fig. 2.1 shows the microphotograph of the test structures and the 3D-layout views up to the reference planes for a MOM capacitor and a HBT in common-emitter.

**Figure 2.1**: De-embedding structures for MOM Capacitor and CE HBT.

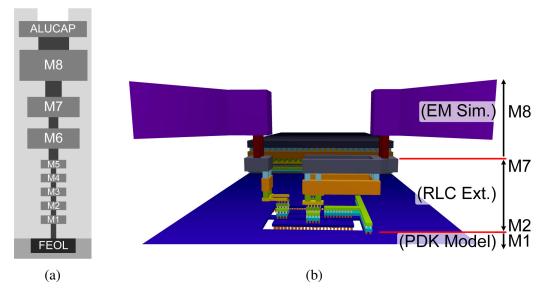

Figure 2.2: (a) BEOL of the technology, (b) Simulation strategy for CE HBT.

The back-end-of-line (BEOL) of the technology is presented in Fig. 2.2(a). For the simulation of MOM capacitor only 2.5 D EM simulators (EMX and Momentum) are

Chapter 2 9

used. On the other hand, as depicted in Fig. 2.2(b), the simulations of heterojunction bipolar transistor (HBT) make use of process design kit (PDK) device model, parasitic extraction tools for low level metals (M2-M7) and EM simululators for high level metals.

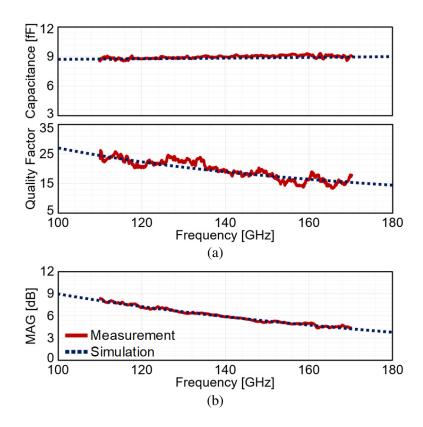

Fig. 2.3 plots the measured results, after de-embedding the access TLINE with the TRL method [24], in comparison with simulations. The plots in Fig. 2.3(a) show the equivalent capacitance ( $C = -\text{Im}[Y_{12}]/\omega$ ) and the quality factor ( $Q = \text{Im}[Y_{12}]/\text{Re}[Y_{12}]$ ) of MOM capacitor while Fig. 2.3(b) reports the Maximum Available Gain (MAG) of the HBT. After fine trimming of the many different simulation tools, the agreement between measurement and simulations is very good, thus giving high confidence level about reliability of simulations for the design of the amplifiers.

**Figure 2.3**: Comparison of EM simulation and de-embedded measurements: (a) Capacitance of MOM capacitor (top), quality factor of MOM capacitor (bottom), (b) maximum available gain of transistor in common emitter configuration.

### 2.2 Single-Ended Amplifier Designs

This section proposes an accurate, yet simple strategy for design and modelling of inductors at very high frequency without the need of performing complex electromagnetic (EM) simulations on large portions of the layout. Inductors are surrounded and co-simulated with a metal shield which ensures the component is unaffected by couplings with nearby structures. Moreover, inductors are considered as 2-port, 4-terminal devices, similar to Tlines, such that both the forward and return current paths can be accurately accounted. The approach is exploited and validated by designing 1-stage and 2-stage compact D-band amplifiers.

### 2.2.1 Circuit Design

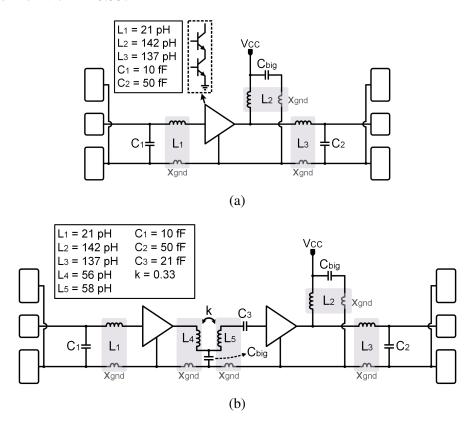

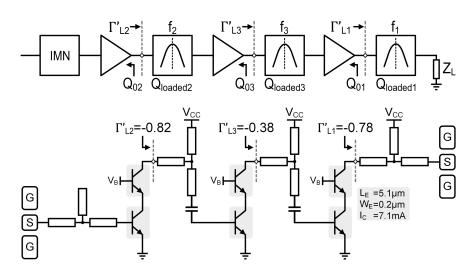

The schematics of the single-stage and 2-stage amplifiers are depicted in Fig. 2.4. The two amplifiers use the same transistor with  $5.1\,\mu\text{m}\times0.2\,\mu\text{m}$  total emitter area. After careful layout, and biased with  $7.1\,\text{mA}$  collector current, the  $f_{\text{max}}$  is simulated as 290 GHz. A single hetero-juntion bipolar transistor (HBT) in common-emitter (CE) configuration with  $V_{\text{CE}}=1\,\text{V}$  displays maximum available gain (MAG) of  $5.8\,\text{dB}$  at  $150\,\text{GHz}$  while the cascode configuration, supplied at  $1.9\,\text{V}$ , performs  $13.8\,\text{dB}$  MAG. Since the minimizing the amplifiers area is essential, and considering cascode structure shows more gain than two cascaded CE stages without the need for bulky interstage matching network, in final design cascode structure was chosen for a gain stage.

Looking at the amplifiers schematic in Fig. 2.4,  $C_1$ - $L_1$  and  $C_2$ - $L_2$ - $L_3$  form input and output matching networks respectively, identical in the one- and two-stage amplifiers. The networks are designed to provide conjugate impedance matching to  $50\,\Omega$  at  $\sim 150\,\text{GHz}$ .  $C_1$  and  $C_2$ , of relatively small value, are realized with  $M_3$ - $M_5$  metal layers as parallel plate capacitors and accurately sized with EM simulations.

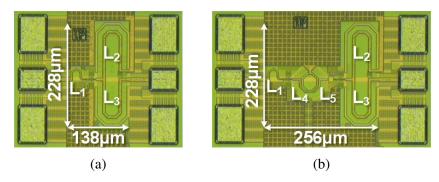

Inductors  $L_1$ ,  $L_2$  and  $L_3$  are realized in the topmost metal layer and laid out with U shape, as visible in the chip photographs in Fig. 2.5. For the largest inductors ( $L_2$ ,  $L_3$ ) the U shape yields  $\sim 30\%$  higher quality factor and  $\sim 10\%$  higher self-resonance frequency compared to a multi-turn layout. Because of the small footprint, metal

density rules are satisfied without adding tiles in close proximity with the inductors. No substrate shield is used, having negligible effect in this frequency range.

In the two-stage amplifier (bottom schematic of Fig. 2.4),  $C_3$  and the magnetically coupled inductors  $L_4$ - $L_5$  implement the inter-stage matching network, stagger tuned to flatten the amplifier frequency response.  $L_4$ - $L_5$  are wounded and form a coplanar transformer with k = 0.33.

**Figure 2.4**: (a) 1-stage and (b) 2-stage amplifiers schematic.  $x_{gnd}$ , coupled with nearby inductors, represents current return paths.

The reactances  $x_{gnd}$  in the schematics of Fig. 2.4 represent nonideal current return paths and are enclosed in a shadowed area to highlight coupling with the corresponding inductors. The approach followed for modelling inductors and  $x_{gnd}$  is deeply discussed in the next section.

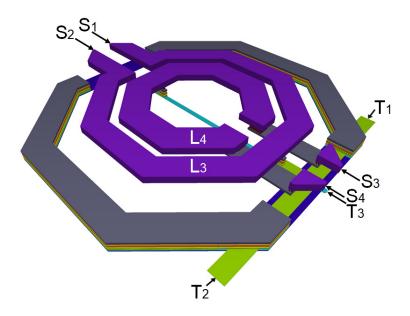

Figure 2.5: Chip microphotograph of the (a) 1-stage and (b) 2-stage amplifiers.

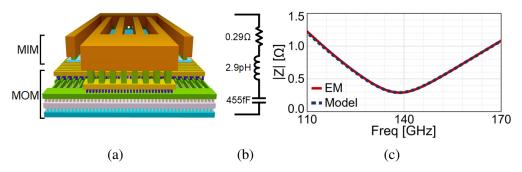

Finally, besides careful modeling of high-frequency effects in matching networks, capacitors for supply decoupling ( $C_{big}$  in Fig. 2.4) deserve attention. Being of large value, the self-resonance frequency has to be carefully accounted. The layout view of  $C_{big}$ , realized by stacking MIM and MOM capacitors, is shown in Fig. 2.6(a) while a simplified equivalent circuit, which comprises the parasitic inductance and resistance of the capacitor plates, is reported in Fig. 2.6(b).  $C_{big}$  must provide low impedance (ideally a short circuit) to the grounding point in the layout at the amplifier center frequency. The capacitor stack is therefore sized to have series resonance frequency near 150 GHz. Fig. 2.6(c) plots the impedance magnitude of  $C_{big}$ , derived from EM simulations, and from the equivalent circuit. The impedance remains below 1  $\Omega$  from 114 to 168 GHz with minimum value of 0.3  $\Omega$  at 140 GHz.

**Figure 2.6**: (a) 3D View of Stacked Capacitor (b) Simplified Model (c) |Z| vs Frequency.

### 2.2.2 Inductors and Current Return Path

The key issues of managing inductors in D-band is taking into account the effects of the surrounding layout (i.e., other components, metals and ground plane) and currents return path. At lower frequency, where the above effects have a minor impact, coupling

with nearby layout structures is typically neglected and a common ideal and shared reference (ground) is assumed in the model of the inductors [21].

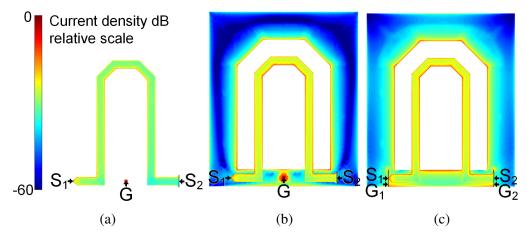

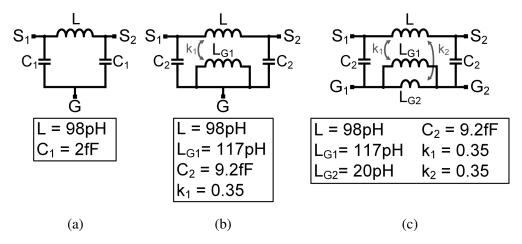

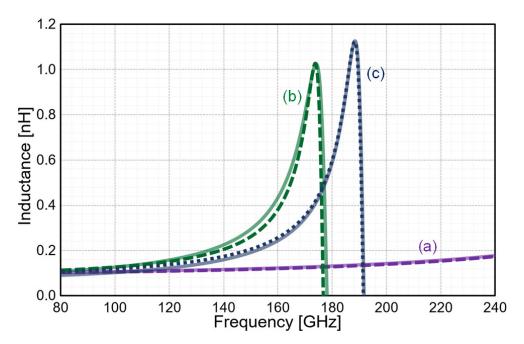

The limitations of this approach in D-band are quantitatively analyzed in this section and a robust implementation and modeling strategy is finally proposed. We keep as an example inductor L<sub>3</sub>, used in the output matching network. Fig. 2.7 shows the layout and the current distribution at 150 GHz, derived from EM simulations, in different cases. Fig. 2.8 presents the corresponding lumped-element models (loss resistors are included in series to each component but not shown for better readability) while Fig. 2.9 plots the simulated and modelled equivalent inductance over frequency.

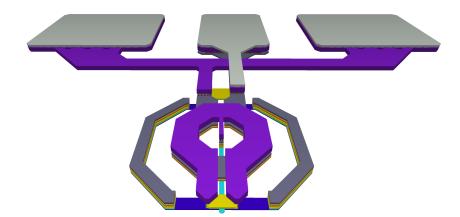

**Figure 2.7**: Inductor layout with current density from EM simulations. (a) 3- terminal without shielding, (b) 3-terminal with a surrounding metal layer, (c) 4-terminal to include current return path.

**Figure 2.8**: Equivalent circuit models reproducing EM simulations for the three situations in Fig. 2.7.

In Fig. 2.7(a) the inductor  $L_3$  (realized in the top Cu metal,  $M_8$ ) is simulated as a 3-terminal device:  $S_1$ ,  $S_2$  are EM-ports at the inductor ending points while G is a port on a substrate tap to account for coupling toward the substrate. This approach is accurate if no other structures or metals are close to the inductor and assumes ideal current return paths (i.e. a shared ground node). The inductor behavior is reproduced by the simple equivalent circuit in Fig. 2.8(a), where the two capacitors  $C_1$  account for substrate coupling. The equivalent inductance,  $L_{eq} = \text{Im}[Z]/\omega$  (with Z the impedance between terminal  $S_1$  and terminal  $S_2$  shorted to G) is plotted in Fig. 2.9 and shows a self-resonance frequency above 240 GHz. The simulated quality factor at 150 GHz (not shown) is Q = 28.

Fig. 2.7(b) shows a more realistic situation where a uniform metal is included around the inductor to mimic the effect of the ground distribution plane in final layout. The distance to the edge of the inductor is set to 3 times the width of the M<sub>8</sub> trace and the inductor is still considered as a 3 terminal device. As evident from the colors of the current density plot, an intense current is induced by the top M<sub>8</sub> trace on the edge of the surrounding metal, suggesting that coupling between the inductor and nearby structures cannot be neglected at all. On the other hand, the same plot reveals that the induced current drops very quickly moving away from the edge of the surrounding metal, suggesting the latter can be exploited to shield very well the inductor from the rest of the layout. The inductor behavior is then robust against ground plane discontinuities slightly away from the edge such as metal slots for density rules or wires for biasing and controls. In the equivalent circuit model, Fig. 2.8(b), the effect of the surrounding metal layer is captured by an additional inductor (L<sub>G1</sub>) coupled to the main inductor (L) and larger capacitances to the G node (C2). Compared to the previous case (Fig. 2.7(a) and Fig. 2.8(a)), the self-resonance frequency of the equivalent inductance, plotted in Fig. 2.9, is now reduced to around 178 GHz. The simulated quality factor at 150 GHz is 17.

By designing and simulating the inductor as in Fig. 2.7(b), the quality factor is penalized, but the component behavior will not be affected by other layout structures that may be in close proximity. However, with a single lumped reference port (G), the

parasitic reactance of the current return path ( $x_{gnd}$  in the schematics of Fig. 2.4) is not yet considered. In D-band, grounding taps located on different places in the layout cannot be assumed as perfectly short-circuited. Therefore, inductors are considered as 4-terminal devices and simulated as shown in Fig. 2.8(c). S<sub>1</sub>, S<sub>2</sub> and G<sub>1</sub>, G<sub>2</sub> (ports in EM simulations) are placed respectively on the inductor ending points and on the ground metal layer just below  $S_1$ ,  $S_2$ . By looking at the current density in Fig. 2.7(c), a significant current flows straight in the return path, from G2 to G1. The 4-terminal inductor equivalent circuit is represented in Fig. 2.8(c) where, in comparison with Fig. 2.8(b) an additional coupled inductor,  $L_{G2}$ , is included to model the return path from G<sub>2</sub> to G<sub>1</sub>. Curve (c) in Fig. 2.9 plots the equivalent inductance, derived from the impedance between  $S_1$  and  $G_1$  terminals with  $S_2$  shorted to  $G_2$ . The self-resonance frequency is around 192 GHz and in the 140-160 GHz (the target bandwidth of the amplifiers) the equivalent inductance falls in the middle between the values predicted by the simplified simulation approaches in Fig. 2.7(a) and Fig. 2.7(b). The estimated quality factor is roughly the same as for the case in Fig. 2.7(b). The importance of careful inductors modelling and the accuracy of the 4-terminal approach is confirmed by comparing measurements of the amplifiers against circuit simulations, performed by modelling the inductors with the 3 approaches of Fig. 2.7, in the following section.

**Figure 2.9**: Equivalent inductance from EM-simulations (dotted lines) and lumped circuit models (solid lines) for the three situations in Fig. 2.7.

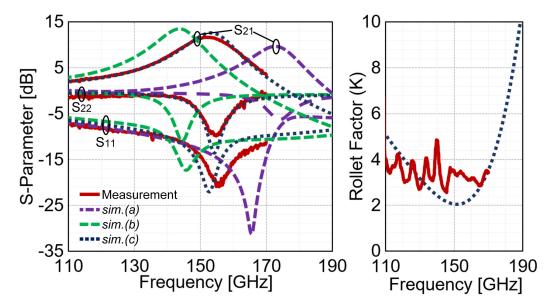

### 2.2.3 Experimental Results

Small-signal measurement was performed using VDI WR-6.5 D-Band Extenders with Agilent PNA-E8361C vector network analyzer (VNA) after thru-reflect-line (TRL) probe tip calibration. Fig. 2.10 plots the measured S-parameters and Rollet stability factor for the one-stage amplifier (red curves). The amplifier draws 7.1 mA from 1.9 V and displays a peak gain of 11.8 dB at 152 GHz with -3 dB bandwidth of 11.8 GHz and unconditional stability over D-band. The same plot compares measurements against simulations, performed by modelling the inductors as discussed in the previous section. sim.(a) neglects coupling of inductors with nearby metals and currents return path. sim.(b) considers a metal loop around inductors but still neglects currents return path while sim.(c) considers both effects. The remarkable discrepancy between measurements and sim.(a), sim.(b) and the very good agreement with sim.(c) confirms the importance of careful inductors modelling and validate the proposed approach. EM simulations for the full layout (excluding HBTs) were also performed and results are in agreement with the much faster sim.(c) approach.

**Figure 2.10**: 1-stage amplifier measurement and comparison with simulations. (*sim.(a)*: unshielded inductors and lumped ground, *sim.(b)*: shielded inductors and lumped ground, *sim.(c)*: shielded inductors and current return paths included).

S-parameter measurements for the 2-stage amplifier are plotted in Fig. 2.11 (red curves). With  $14.2 \,\mathrm{mA}$  from  $1.9 \,\mathrm{V}$  supply voltage, the amplifier reaches a peak gain of  $20.1 \,\mathrm{dB}$  at  $150 \,\mathrm{GHz}$  with  $-3 \,\mathrm{dB}$  bandwidth of  $24.5 \,\mathrm{GHz}$ . Also in this case measurements are in good agreement with sim.(c) while a remarkable discrepancy is evident with sim.(a) and sim.(b).

**Figure 2.11**: 2-stage amplifier measurement and comparison with simulations. (*sim.(a)*: unshielded inductors and lumped ground, *sim.(b)*: shielded inductors and lumped ground, *sim.(c)*: shielded inductors and current return paths included).

### 2.3 Differential Amplifier Designs

In order to circumvent the current return path issue at very high frequencies, this section proposes differential D-band amplifiers with transformers in matching networks, such that no signal current flows through the ground metal plane. The approach is exploited and validated by designing 1-stage and 2-stage compact D-band amplifiers.

### 2.3.1 Circuit Design

The schematics of differential D-band amplifiers are shown in Fig. 2.12. Transistors are employed in CBEBC structure with  $0.2 \,\mu\text{m} \times 5.1 \,\mu\text{m}$  total emitter area, and the current density is chosen to maximize  $f_t$  at  $7.1 \,\text{mA}/\mu\text{m}^2$ . After optimized layout of

metal layers contacting the HBT terminals, the device is unconditionally stable in D-Band, and the  $f_{max}$  of the transistor is simulated as 290 GHz. A single transistor in common-emitter configuration exhibits 5.8 dB Maximum Available Gain (MAG) at 150 GHz (consistent with the measurements in Section 2.1) while the stack of two transistors in cascode configuration, with 1.9 V voltage supply, reaches MAG of 13.8 dB. Therefore the cascode configuration which allows more gain than two cascaded common-emitter stages without the necessity of using a bulky interstage matching network, is selected.

**Figure 2.12**: Schematic of (a) 1-stage amplifier, (b) 2-stage amplifiers.

A differential configuration for the amplifiers is selected because, provided symmetry is maintained in layout, a well-defined virtual ground is established and ideally no signal current flows through the ground plane. This choice avoids the complex and time consuming task of accurate modelling the reactive effects of the ground metal layer in layout [22], [23]. Moreover, in view of active phased arrays with several amplifiers on the same chip, a differential configuration provides common mode noise rejection (e.g. supply and ground noise). Considering the schematic of the 1-stage amplifier

in Fig. 2.12(a),  $C_{1a}$ - $C_{2a}$  with the coupled coils  $L_{1a}$ - $L_{2a}$  and  $C_{3a}$ - $C_{4a}$  with  $L_{3a}$ - $L_{4a}$  form the input and output matching networks respectively, designed to provide conjugate impedance matching to  $50 \Omega$  at  $150 \, \text{GHz}$ . The capacitors  $(C_{1a-4a})$ , of relatively small value, are implemented with a custom layout as a parallel plate structure with M<sub>3</sub>-M<sub>5</sub> metal layers, and precisely sized with electromagnetic (EM) simulations. Being the input and output signals at the GSG pads single-ended, the coupled coils at the input  $(L_{1a}-L_{2a})$  and output  $(L_{3a}-L_{4a})$  perform single-ended to differential conversion and vice versa. The inductors are sized and simulated together with the GSG pad. As an example, Fig. 2.13 shows the 3D layout of the input transformer ( $L_{1a}$ - $L_{2a}$ ) connected to the pads.  $L_{1a}$  is realized in the two metal levels below the topmost layer (M<sub>6</sub>-M<sub>7</sub>) in a stack with a diameter of 42  $\mu$ m and a width of 11  $\mu$ m. L<sub>2a</sub> is implemented in the topmost metal layer  $(M_8)$  with the same diameter and width of  $L_{1a}$ . The center of the  $L_{2a}$  is tapped for biasing of input transistors. A side-wall around the coupled inductors, acting as a shield from the surrounding structures in the final amplifier layout, is realized by stacking M<sub>1</sub>-M<sub>7</sub> metal layers, and included in the EM simulations. The estimated equivalent inductances ( $L_{eq} = Im[Z]/\omega$ ) of  $L_{1a}$  and  $L_{2a}$  are 28 pH and the quality factors (Q = Im[Z]/Re[Z]) are 16 and 19 respectively at 150 GHz. The coupling coefficient, defined as  $k = \text{Im}[Z_{21}]/\sqrt{\text{Im}[Z_{11}] \cdot \text{Im}[Z_{22}]}$ , is 0.55. The layout of the output transformer ( $L_{3a}$ - $L_{4a}$ ) is similar to  $L_{1a}$ - $L_{2a}$  but the spirals are sized such that  $L_{3a} = 105 \text{ pH}$ ,  $L_{4a} = 95 \text{ pH}$ , and k=0.6. The supply voltage for the cascode pair is fed by a center tap on  $L_{3a}$ .

Figure 2.13: Layout of the input matching network of one-stage amplifier.

In the two-stage amplifier, the input and the output baluns are similar to the single-stage design and an additional transformer is employed as an inter-stage matching network with center taps in primary and secondary coils to provide supply and bias voltage to the first and second stage respectively. The inductors are sized to resonate with the parasitic capacitances of transistors and resonance frequencies are stagger tuned to enlarge the bandwidth. The 3D layout view of the inter-stage transformer is drawn in Fig. 2.14. Being  $L_{3b} = 148 \, \text{pH}$ , higher then  $L_{4b} = 90 \, \text{pH}$ , a planar geometry with both coils in the topmost metal layer is selected giving higher Q ( $\sim$ 20) and self-resonance frequency. A grounded side-wall stacking  $M_1$ - $M_7$  is also included to shield the component.

Figure 2.14: Layout of the transformer in 2-stage amplifier.

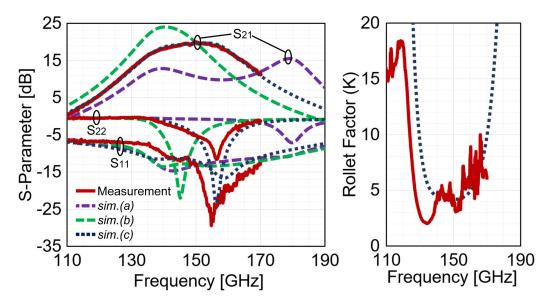

### 2.3.2 Experimental Results

The microphotographs of the fabricated amplifiers are shown in the Fig. 2.15. The core of the one-stage and two stage amplifier occupies very small area of  $116\,\mu\text{m}\times220\,\mu\text{m}$  (0.026 mm<sup>2</sup>) and  $125\,\mu\text{m}\times387\,\mu\text{m}$  (0.048 mm<sup>2</sup>) respectively.

Small-signal measurement was performed using VDI WR-6.5 D-Band Extenders with Agilent PNA-E8361C vector network analyzer (VNA) and N5260A Millimeter Head

Chapter 2 21

Controller. Input and output pads were designed for 75 µm pitch GSG probes. The TRL probe tip calibration has been applied with Cascade standard substrate (138-356).

**Figure 2.15**: Chip microphotograph of the (a) 1-stage and (b) 2-stage differential amplifiers.

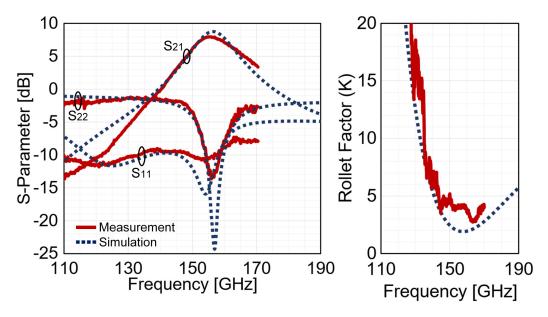

Fig. 2.16 plots the measured S-parameters and Rollet stability factor for the one-stage amplifier (red curves). The amplifier draws 14.2 mA from 1.9 V and displays a peak gain of 8 dB at 156 GHz with -3 dB bandwidth of 17.8 GHz and unconditional stability over D-band. The same plot in Fig. 2.16 compares measurements against simulations proving an excellent agreement.

**Figure 2.16**: S-Parameter comparison of measurement and simulation for one-stage amplifier.

S-parameter measurements for the two-stage amplifier are plotted in Fig. 2.17 (red curves). With 28.4 mA from 1.9 V supply voltage, the amplifier reaches a peak gain of

17.4 dB at 157 GHz with -3 dB bandwidth of 42.7 GHz. Simulations, with dotted lines in the same plots, are still in very good agreement with measurements.

The noise figure (NF) at 150 GHz, derived from simulations, is 11.4 dB and 10.5 dB for the one-stage and two-stage amplifiers, respectively while the output power at 1 dB gain compression is -1.9 dBm and 1.8 dBm.

**Figure 2.17**: S-Parameter comparison of measurement and simulation for two-stage amplifier.

### 2.4 Conclusion

In this chapter compact D-band amplifiers were presented. To solve the current return path issue 2 different solutions were proposed. In the design of single-ended amplifiers, to account current return path, accurate, yet simple modelling of inductors was presented. In the Section 2, differential amplifiers made use of differential structure and symmetric layout to solve the problem.

Measurement results are summarized in Table 2.1 and compared with other SiGe HBT amplifiers operating above 100 GHz. [15] was among the first works demonstrating silicon amplifiers in D-band (to Authors knowledge). The amplifier, with 5 CE stages and based on lumped-component matching networks, features lower gain with less bandwidth and larger area occupation than the 2-stage amplifiers presented in this work. [16–19] are two-stage amplifiers with cascode HBT configuration and

Chapter 2 23

transmission line matching networks. The two-stage amplifiers presented in this work has the same transistor configuration and number of stages. Therefore, a direct and fair comparison is possible. The presented amplifiers are highly compact, with  $2\times$  to  $5.7\times$  smaller area. Even though [16] and [18] have slightly higher  $(1.4\times$  and  $1.5\times$  for single-ended,  $1.1\times$  and  $1.2\times$  for differential) gain-bandwidth product (GBW), which partially benefit by the lower center frequency, the area occupation is significantly larger  $(5.7\times$  and  $3.7\times$  for single-ended,  $6.9\times$  and  $4.5\times$  for differential). Nevertheless, by adding one more stage to the current design the GBW can be significantly increased still maintaining advantage on area occupation.

|                                        |         | This   | Work   |        | [15]    | [16]    | [17]    | [18]    | [19]    |

|----------------------------------------|---------|--------|--------|--------|---------|---------|---------|---------|---------|

|                                        | S       | .E.    | DIFF.  |        | [13]    | [10]    | [1/]    | [10]    | [19]    |

| Technology                             | 55 nm   |        |        |        | 130 nm  |

| f <sub>t</sub> /f <sub>max</sub> [GHz] | 320/370 |        |        |        | 230/300 | 250/300 | 300/500 | 300/500 | 300/500 |

| # Stages                               | 1       | 2      | 1      | 2      | 5       | 2       | 2       | 2       | 2       |

| Gain [dB]                              | 11.8    | 20.1   | 8      | 17.4   | 17      | 25      | 20.5    | 27.5    | 16.1    |

| Center Freq.<br>[GHz]                  | 152     | 150    | 156    | 150    | 140     | 120     | 110     | 125     | 143     |

| -3 dB Bandwidth<br>[GHz]               | 17.9    | 24.5   | 17.8   | 42.7   | 16      | 20      | 20      | 16      | 11      |

| Gain-Bandwidth<br>Product [GHz]        | 69.6    | 247.8  | 44.7   | 316.5  | 113.3   | 355.7   | 211.9   | 379.4   | 70.2    |

| NF [dB]                                | 9.7**   | 10.2** | 11.4** | 10.5** | -       | 9**     | 4       | 6.5     | 7.7     |

| PDC [mW]                               | 13.5    | 27     | 27     | 54     | 112     | 54      | 17      | 12      | 36.8    |

| Core Area* [mm²]                       | 0.031   | 0.058  | 0.026  | 0.048  | 0.080   | 0.330   | 0.220   | 0.214   | 0.107   |

<sup>\*</sup>Estimated from chip photographs excluding PADs

Table 2.1: Comparison with SiGe amplifiers above 100 GHz

<sup>\*\*</sup>Simulation

# **Analysis and Design of Wideband Amplifiers for D-Band Applications**

### 3.1 Introduction

In D-band spectrum the total usable bandwidth for fixed wireless services is 31.8 GHz as mentioned in the Chapter 1. A key challenge in the design of amplifiers for such systems is providing enough gain over the full bandwidth, requiring a gain-bandwidth product (GBW) of several hundred GHz. Distributed amplifiers in SiGe HBT technology demonstrated over 500 GHz GBW in D-band, but with high power consumption [25, 26]. Tuned amplifiers save power but in D-band the design is made challenging by the low available gain of transistors, operating close to f<sub>max</sub>. To boost the transistor's gain beyond the Maximum Available Gain (MAG), different strategies for device unilateralization have been investigated, but over limited bandwidth [27– 29]. In general, tuned amplifiers have to be realized with several cascaded stages, conjugately matched for maximum power transfer. However, matching networks are inherently narrow-band, exacerbating the GBW issue. Several D-band multi-stage tuned amplifiers have been demonstrated in CMOS [30–33] and SiGe HBT technology [34–45], with the latter showing a significant GBW advantage. The choice of the transistor configuration also plays a key role on the amplifier performance. In fact, the achievable bandwidth of an impedance-matched gain stage is bounded by the nodal quality factor (Q<sub>n</sub>) of the impedances to be matched, i.e., the input and output impedance presented by the active stage [46]. The most widely adopted transistor configurations for D-band amplifiers are the common-emitter and cascode. While Qn of the impedance at the base and collector of an HBT in common emitter is relatively low, facilitating wideband matching, transistors in the cascode configuration rise substantially Qn of the output impedance, making broadband matching difficult

[36, 38–40, 42, 45]. On the other hand, the cascode stage is typically preferred because of the remarkably higher available gain.

In this work, the common-emitter and cascode gain stages are first compared, focusing on the impedance matching issues for designing high GBW amplifiers in D-band. The non-linear relation between gain and bandwidth in resonant matching networks is then formally analyzed proving that when the gain stage displays high nodal quality factor at the output port, like the cascode, if power gain is slightly penalized by rising the load reflection coefficient the bandwidth is significantly increased, finally giving a remarkable improvement on the amplifier GBW. The analysis is further extended to derive the optimal load reflection coefficient to maximize the power gain or the GBW in the practical case of matching networks realized with lossy reactive components. D-band amplifiers with 1-, 2- and 3-stage are designed in 55 nm SiGe BiCMOS technology from STMicroelectronics to validate the analysis and to demonstrate the high achievable GBW. The 2-stage and 3-stage amplifiers prove 20.6 dB gain with 65.8 GHz bandwidth and 28.6 dB gain with 64.3 GHz bandwidth respectively. The GBW of 705 GHz and 1731 GHz are comparable or higher then distributed amplifiers with a remarkably lower power consumption. The paper is organized as follow. Section-3.2 compares in detail the differences in gain, bandwidth, input and output impedances of common emitter and cascode stages. Section-3.3 analyzes the gain-bandwidth trade-off with respect to the load reflection coefficient in resonant matching networks, and show how to apply the concept for GBW extension with a cascode amplifier. Section-3.4 describes the design of amplifiers while measurements are presented in Section-3.5. Finally, Section-3.6 compares experimental results with state of the art and concludes the paper.

### 3.2 Review of Common-Emitter and Cascode Gain Stages

The active gain stages in D-band amplifiers are commonly implemented with transistors in common emitter (CE) or with the cascode configuration, shown in Fig. 3.1. The two alternatives are analyzed and compared in this section, focusing on the available gain and the issues related to broad-band impedance matching. The

Chapter 3 27

same transistor is used, with an emitter area of  $0.2 \,\mu\text{m} \times 5.1 \,\mu\text{m}$ , with a collector to base voltage  $V_{CB} = 0$  and a current of 7 mA which provides  $f_{max} = 290 \,\text{GHz}$ .

Figure 3.1: Common emitter (a) and cascode (b) gain stages.

The simulated MAG versus frequency for the two alternatives in Fig. 3.1 is shown in Fig. 3.2. Looking at Fig. 3.2, at 150 GHz the MAG of the CE stage is 5.5 dB only, while the cascode yields a remarkable improvement [43, 47]. The stacked common-base transistor (T2 in Fig. 3.1(b)) rises significantly the output impedance with a minimal penalty on the short-circuit transconductance of the stage [48]. As a result, the MAG increases to 15 dB, roughly equivalent to the cascade of three conjugately matched CE amplifiers.

**Figure 3.2**: MAG/MSG versus frequency for the common emitter and cascode active stages.

The MAG is the upper bound on transducer power gain, reached with an optimal source impedance,  $Z_{S-opt}$ , which maximizes the available power gain,  $G_A = P_{A0}/P_{S0}$

(being  $P_{A0}$  and  $P_{S0}$  the available power from the amplifier stage and from the source) and the optimal load impedance,  $Z_{L-opt}$ , which maximizes the operating power gain,  $G_P = P_L/P_{in}$  (with  $P_L$  the power delivered to the load and  $P_{in}$  the power delivered by the source, i.e. the input power to the transistor). In this condition the active stage is also conjugately matched at the input and output, i.e.  $Z_{S-opt} = Z_{in}^*$ ,  $Z_{L-opt} = Z_{out}^*$ .

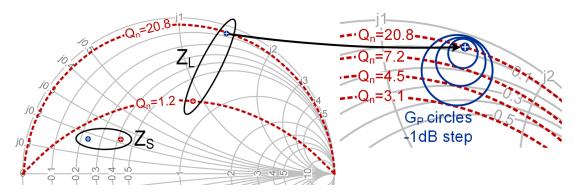

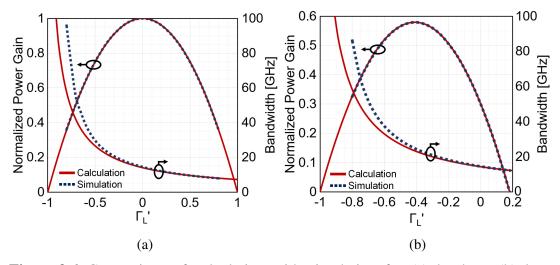

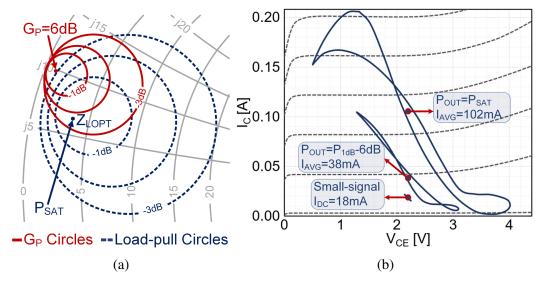

The required source and load impedances influence the achievable bandwidth. Assuming a simple resonant network is used to match a  $50\,\Omega$  resistance to  $Z_S$ ,  $Z_L$ , the bandwidth can be approximated as  $BW=2f_0/Q_n$  where  $f_0$  is the center frequency and  $Q_n=Im[Z_n]/Re[Z_n]$  (n=S,L) [46]. The optimal source and load impedances at 150 GHz are shown on the Schmitt chart in Fig. 3.3 together with curves of constant  $Q_n$ .  $Z_{S-opt}$  and  $Z_{L-opt}$  for the CE transistor fall within the Q=1.2 curve, thus not introducing any limitation to the amplifier bandwidth. With the cascode configuration, Q of  $Z_{S-opt}$  remains low, but because of the high resistance at the collector of T2,  $Z_{L-opt}$  is remarkably higher than for the CE transistor alone and Q of  $Z_{L-opt}$  is raised to 20.8, posing a serious bandwidth issue (BW $\approx$ 14 GHz) with impedance matching.

**Figure 3.3**: Optimal source and load impedances at 150 GHz for the common emitter and cascode active stages.

In summary, the CE transistor is penalized by a low upper bound on power gain but it allows simple wideband matching. On the opposite, the cascode features a remarkably higher MAG but rises challenges in matching networks design. It is worth noticing that cascode gain can be further increased by adding inductors at the emitter and/or base terminals of the common-base transistor (T2 in Fig. 3.1(b)) [42, 44, 45, 48, 49], still with the challenge of wideband output matching. Furthermore, although the analysis has been quantitatively performed on a specified transistor size, the conclusion remains

Chapter 3 29

valid in general, being MAG and  $Q_n$  of the optimal source and load impedances nearly independent from the emitter area at fixed current density.

Considering the very low MAG in D-band of the CE transistor, the cascode remains preferable, allowing a wider design space to trade gain for bandwidth. To this purpose, a simple solution is to select a load impedance with lower Q. In the right of Fig. 3.3 constant GP circles around  $Z_{L-opt}$  are drawn, with steps of -1dB from the MAG value. Q decreases very quickly as  $Z_L$  shifts toward the center of the chart. As an example, with 3 dB of gain penalty Q is reduced from 20.8 to 3.1, yielding more than six times wider bandwidth and hence an overall improvement in the gain-bandwidth product. This trade-off is quantitatively analyzed in the next section considering first the realistic situation of matching the cascode output impedance to a general impedance (with resistive and reactive components) and, in a second step, including the impact of the losses in the matching network components.

**Figure 3.4**: Equivalent circuit of the cascode stage driven by  $Z_{S-opt}$  and with matching toward the equivalent impedance at the GSG pad.

### 3.3 Anaylsis of Cascode Output Matching Network

The trade-off and optimal design of a resonant matching network at the output of the cascode stage is studied in this section considering the practical situation depicted in Fig. 3.4. We assume the cascode is terminated at the input with the source impedance  $Z_S$ . In this way the cascode output impedance, the available power gain,  $G_A$ , and the available power  $P_{A0} = G_A \cdot P_{S0}$  are fixed. A matching network is placed between the output port and the load (represented by  $R_L \parallel C_L$ ). In the neighborhood of the center frequency,  $f_0$ , the output port of the cascode can be modelled with an equivalent output resistance  $r_0$ , capacitance  $r_0$  and the current source  $r_0 = 2\pi f_0 r_0 c_0$ , is relatively high (from the example

in Sec. 3.2,  $Q_0 = 20.8$  if  $Z_S = Z_{S-opt}$ ). On the opposite, the nodal quality factor of the load impedance,  $Q_L = 2\pi f_0 R_L C_L$ , is assumed low because  $R_L \parallel C_L$  represents the input impedance of a cascaded stage ( $Q_L \approx 0.6$  from Sec. 3.2) or the equivalent impedance at the ground-signal-ground (GSG) pad, where the impedance of the pad parasitic capacitance is reasonably higher than the terminating resistance. Having represented equivalent circuits with parallel elements it is convenient to analyze the network with the admittance parameters. The matching network transforms the load admittance,  $Y_L = R_L^{-1} + j\omega C_L$ , to the admittance  $Y_L'$  seen by the cascode. Let's assume the network is designed such that the susceptance of  $Y_L'(f_0)$  is the conjugate of the susceptance of  $Y_0(f_0)$  ( $Im[Y_L'(f_0)] = -Im[Y_0(f_0)]$ ). In this case the reflection coefficient at the output of the active stage  $\Gamma_L'$  is set by the real part of  $Y_L'$  and  $Y_0$ . By defining  $R_L' = (Re[Y_L'(f_0)])^{-1}$  and being  $r_0 = (Re[Y_0(f_0)])^{-1}$ :

$$\Gamma_L' = \frac{R_L' - r_0}{R_L' + r_0} = \frac{1 - \frac{r_0}{R_L'}}{1 + \frac{r_0}{R_L'}}$$

(3.1)

Maintaining generality on the matching network topology we want to estimate the achievable bandwidth and how gain and bandwidth are influenced by the reflection coefficient given by (3.1). The analysis follows the law of conservation of complex power as in [50]. First, a lossless case is considered, i.e., a matching network realized with ideal reactive components. The impact of lossy components is evaluated in a second step.

### 3.3.1 Lossless Matching Network

Having assumed that  $Im[Y_0(f_0)] = -Im[Y'_L(f_0)]$ , the capacitors  $c_0$  and  $C_L$  resonate with the reactive components in the matching network, while only resistors  $r_0$  and  $R_L$  dissipate active power. Denoting with  $W_t$  the total reactive energy stored, and with P the total dissipated active power, the loaded network quality factor is:

$$Q_{loaded} = \frac{2\pi f_0 W_t}{P} \tag{3.2}$$

and the bandwidth can be approximated with [46]:

$$BW = \frac{f_0}{O_{loaded}} \tag{3.3}$$

Although eq. (3.2) with Q given by (3.1) is rigorously valid only for simple LC tanks, it yields a reasonably accurate estimation of the bandwidth also for a general resonator, particularly if Q is high [51].

If the matching network in Fig. 3.4 is realized only with components storing magnetic energy (i.e., inductors) the reactive energy at resonance is equal to the electrical energy stored in  $c_0$  and  $C_L$ , denoted by  $W_{C_0}$  and  $W_{C_L}$  respectively. The nodal quality factors of  $Y_0$  and  $Y_L$  allow to express  $W_{C_0}$  and  $W_{C_L}$  as a function of  $P_{r_0}$  and  $P_L$ , the active power dissipated on  $r_0$  and  $R_L$ :

$$W_t = W_{c_0} + W_{C_L} = \frac{Q_0 P_{r_0} + Q_L P_L}{2\pi f_0}$$

(3.4)

By using (3.4), the loaded quality factor given by (3.2) can be rewritten as:

$$Q_{loaded} = \frac{Q_0 P_{r_0} + Q_L P_L}{P_{r_0} + P_L} = \frac{Q_0 \frac{P_{r_0}}{P_L} + Q_L}{\frac{P_{r_0}}{P_L} + 1}$$

(3.5)

Eq. (3.4) and (3.5), suggest that a matching network comprising only inductors is preferable for maximum bandwidth. In fact, any other capacitor (in addition to  $c_0$  and  $C_L$ ) would rise the reactive energy and the loaded quality factor, finally penalizing the bandwidth.

Eq. (3.5) shows that for a given active stage and load (i.e.,  $Q_0, Q_L$ ) the loaded Q is determined by the ratio between the power dissipated in the transistor output resistance and the active power delivered to  $R_L$ . Being  $Q_0 >> Q_L$ , from (3.5) the Q can be reduced (increasing the bandwidth) by reducing the  $P_{r_0}/P_L$  ratio.

From Fig. 3.4,  $r_0^{-1} = \text{Re}[Y_0]$  and  $R'_L = \text{Re}[Y'_L]$  form a current divider for  $i_0$ . Considering the available power from the active stage and with the lossless matching network assumption (i.e.  $P_L = P_{\text{out}}$ ), the powers  $P_{r_0}$  and  $P_L$  normalized to  $P_{A0}$  are:

$$\frac{P_{r_0}}{P_{A0}} = \left(\frac{2}{1 + \frac{r_0}{R_L'}}\right)^2 = (1 + \Gamma_L')^2 \tag{3.6}$$

$$\frac{P_{out}}{P_{A0}} = \frac{P_L}{P_{A0}} = \left(\frac{2}{1 + \frac{r_0}{R_L'}}\right)^2 \frac{r_0}{R_L'} = 1 - \Gamma_L'^2$$

(3.7)

Eq. (3.7) represents the transducer power gain,  $G_{T-MN}$ , of the matching network. Combining (3.6), (3.7) with (3.5), the loaded quality factor can be rewritten as:

$$Q_{loaded} = \frac{Q_0 + Q_L \frac{r_0}{R'_L}}{1 + \frac{r_0}{R'_L}} = \frac{1}{2} (Q_0 (1 + \Gamma'_L) + Q_L (1 - \Gamma'_L))$$

(3.8)

If  $\Gamma_L'=0$  the amplifier is conjugately matched. From (3.7)  $P_L=P_{A0}$  and from (3.8) the  $Q_{loaded}$  is the arithmetic mean of  $Q_0$  and  $Q_L$  ( $Q_{loaded}=(Q_0+Q_L)/2$ ). A positive  $\Gamma_L'$  ( $R_L'>r_0$ ) penalizes both power gain and bandwidth, because with  $0<\Gamma_L'<1$ ,  $P_L$  is reduced and the loaded quality factor tends to be  $Q_0$  (which is assumed  $\gg Q_L$ ). On the other hand, if  $\Gamma_L'$  is negative ( $R_L'< r_0$ ) the power gain is still reduced but the bandwidth increases. In fact,  $-1<\Gamma_L'<0$  limits  $P_L$  but moves the loaded quality factor towards to  $Q_L$  ( $\ll Q_0$ ). For a relatively small negative  $\Gamma_L'$  the bandwidth grows much faster than the gain penalty, improving the amplifier GBW.

It is worth noticing that  $\Gamma_L' < 0$  is effective for GBW extension only if the nodal quality factor of the active stage is much higher than the nodal quality factor of the load to be matched, which is indeed the typical case with a cascode active stage. If  $Q_0 \ll Q_L$  GBW is enhanced by  $\Gamma_L' > 0$ . But if  $Q_0 \simeq Q_L$ , from (7) and (8)  $\Gamma_L' \neq 0$  penalizes gain without changing  $Q_{loaded}$  and hence the bandwidth.

### 3.3.2 Matching Network with Lossy Components

We now consider the practical case of lossy components in the matching network, i.e., reactances featuring a finite quality factor,  $Q_r$ . In this situation the matching network dissipates a fraction of the stored reactive energy:

$$P_{diss} = 2\pi f_0 W_t / O_r \tag{3.9}$$

The above equation reveals that the power lost is minimized, for a given  $Q_r$ , if the matching network comprises only magnetic components resonating with  $c_0$  and  $C_L$ , because  $W_t = W_{C_0} + W_{C_L}$  is minimized. Any capacitor included in the matching network would rise the reactive energy above this minimum and consequently the power lost in the network.

From Fig. 3.4, the active power delivered by the cascode stage is:

$$P_{out} = P_{diss} + P_L \tag{3.10}$$

From (3.10), it may happen that with a lossy matching network  $P_{diss} = P_{out}$ , hence  $P_L = 0$ . This condition sets an upper bound on the achievable reflection coefficient,  $\Gamma'_{L-max}$ .  $P_L = 0$  leads to  $W_{C_L} = 0$  and the total reactive energy in (3.9) corresponds only to the electrical energy stored by the output capacitance  $c_0$  in Fig. 3.4,  $W_t = W_{c_0} = P_{r_0}Q_0/(2\pi f_0)$ . Using (3.6), (3.7) to express  $P_{r_0}$  and  $P_{diss} = P_{out}$  as a function of  $\Gamma'_{L-max}$ , (3.9) can be written as:

$$1 - \Gamma_{L-max}^{\prime}^{2} = (1 + \Gamma_{L-max}^{\prime})^{2} \frac{Q_{0}}{Q_{r}}$$

(3.11)

whose solution is:

$$\Gamma'_{L-max} = \frac{1 - \frac{Q_0}{Q_r}}{1 + \frac{Q_0}{Q_r}}$$

(3.12)

For  $\Gamma_L' < \Gamma_{L-max}'$ ,  $P_L$  and  $W_{C_L} > 0$ . Replacing  $P_{diss}$  given by (3.9) in (3.10), with  $W_t$  given by (3.4), and making use of (3.6), (3.7) to express  $P_{r_0}$  and  $P_{out}$  as a function of  $\Gamma_L'$ , leads to:

$$(1 - \Gamma_L'^2) P_{A0} = \frac{(1 + \Gamma_L')^2 P_{A0} Q_0 + P_L Q_0}{Q_r} + P_L$$

(3.13)

which can be solved to find the transducer gain with the lossy components in the matching network:

$$G_{T-MN} = \frac{P_L}{P_{A0}} = \frac{1}{1 + \frac{Q_L}{Q_r}} \left( (1 - {\Gamma_L'}^2) - \frac{Q_0}{Q_r} (1 + {\Gamma_L'})^2 \right)$$

(3.14)

The above equation highlights that an optimal reflection coefficient exists,  $\Gamma'_{L-opt}$  to maximize the power gain:

$$\Gamma_{L-opt}' = -\frac{Q_0}{Q_0 + Q_r} \tag{3.15}$$

and with  $\Gamma_L' = \Gamma_{L-opt}'$  the maximum matching network transducer gain is:

$$G_{T-max} = \frac{1}{\left(1 + \frac{Q_L}{Q_r}\right)\left(1 + \frac{Q_0}{Q_r}\right)}$$

(3.16)

Turning now to the bandwidth, it can still be estimated with (3.3) but with  $Q_{loaded}$  given by:

$$Q_{loaded} = \frac{2\pi f_0 W_t}{P_{r_0} + P_{diss} + P_L} \tag{3.17}$$

As intuitively expected, the lossy matching network reduces  $Q_{loaded}$  (thus increasing the bandwidth) because of the inclusion of  $P_{diss}$  in the denominator of (3.17). Replacing  $W_t$  from (3.4) and expressing the active powers in (3.17) by means of  $\Gamma'_L$ ,  $Q_{loaded}$  can be rewritten as follows:

$$Q_{loaded} = \frac{1}{2\left(1 + \frac{Q_L}{Q_r}\right)} (Q_0(1 + \Gamma_L') + Q_L(1 - \Gamma_L'))$$

(3.18)

The dependence of  $Q_{loaded}$  on  $\Gamma'_L$  remains the same as for the lossless network (with  $Q_{loaded}$  given by (3.8)). In particular, with  $-1 < \Gamma'_L < 0$   $Q_{loaded}$  tends to  $Q_L \ (\ll Q_0)$  thus raising the amplifier bandwidth. The impact of the finite quality factor of the network reactances,  $Q_r$ , on  $Q_{loaded}$  is captured by the term  $(1 + Q_L/Q_r)$  in the denominator of (3.18). It is interesting to note that the effect is limited in practice because  $Q_L \ll Q_r$ . However, the lossy network mandates selection of  $\Gamma'_L < 0$  also to maximize the power gain (with  $\Gamma'_{L-opt}$  given by (3.15)) and this choice also increases the bandwidth by shifting  $Q_{loaded}$  towards to  $Q_L$ .

### 3.3.3 Comparison with Simulations

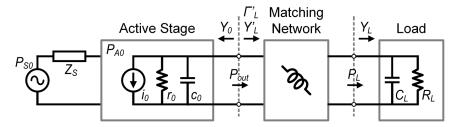

The most relevant equations from the above analyses are plotted in this section and validated against circuit simulations. The circuit schematic considered is shown in Fig. 3.5, with realistic component values. The active stage is modelled with  $r_0$ =1.45 k $\Omega$ ,  $c_0$ =15.2 fF, which correspond to the output impedance at  $f_0$ =150 GHz, of the cascode active stage considered in Sec. 3.2 terminated at the input with  $Z_{S-opt}$ . The load comprises  $R_L$ =29  $\Omega$ ,  $C_L$ =22 fF which represent the impedance at the GSG pad (terminated on 50  $\Omega$  employed for the design of the amplifiers described in the next section. With the above component values  $Q_0$  = 20.8,  $Q_L$  = 0.6. The matching network is realized with the 3 inductors  $L_1$ - $L_3$ , sized to have  $Im[Y'_L] = -Im[Y_0]$  and different values of  $R'_L$  = 1/Re[Y'\_L] thus different values of  $\Gamma'_L$ .

Chapter 3 35

**Figure 3.5**: Circuit schematic used to validate the analysis with simulations.

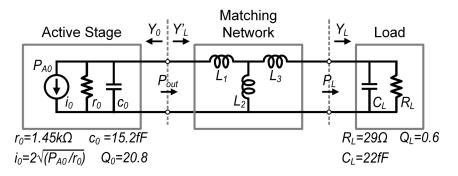

First, inductors are assumed lossless. Fig. 3.6(a) compares the calculated transducer power gain, given by (3.7), and bandwidth given by (3.2) with  $Q_{loaded}$  in (3.8), against simulations. As previously discussed,  $\Gamma_L' > 0$  penalizes gain and bandwidth while  $\Gamma_L' < 0$  reduces the gain but increases the bandwidth, thus initially improving the GBW until a maximum is achieved. The calculated gain matches perfectly with simulations, because no simplifying assumptions have been made in calculations. The agreement between (3.2), (3.3) and the simulated bandwidth, measured as the frequency points at -3 dB from the maximum gain, is very good at high  $Q_{loaded}$ , (toward positive values of  $\Gamma_L'$ ). At low  $Q_{loaded}$  a discrepancy between simulations and calculations is observed, because (3.2) and (3.3) are rigorously valid only for simple series or parallel resonators. Nevertheless, the analysis allows to explain and still predict reasonably well the dependence of bandwidth on  $\Gamma_L'$ .

**Figure 3.6**: Comparison of calculation with simulation for (a) lossless, (b) lossy matching network, Normalized gain and bandwidth.

Simulations and calculations with lossy inductors are then reported in Fig. 3.6(b). In this case, a resistance in series with  $L_1$ - $L_3$  is included in simulations to have  $Q_r = 30$  at  $f_0$ =150 GHz. Fig. 3.6(b) compares the transducer power gain, calculated with (3.14), and bandwidth, given by (3.2) with  $Q_{loaded}$  in (3.18), against simulations. From (3.12), the finite  $Q_r$  limits the maximum achievable reflection coefficient to  $\Gamma'_{L-max} = 0.18$ , confirmed by the simulations. As expected from (3.15), the maximum gain ( $G_{T-MN-max} = 0.58$ ) is now achieved with a negative reflection coefficient,  $\Gamma'_{L-opt} = -0.41$ . With  $\Gamma'_L > \Gamma'_{L-opt}$  both the gain and bandwidth are penalized while for  $\Gamma'_L < \Gamma'_{L-opt}$  the gain is reduced but the bandwidth increases, enhancing the GBW.

### 3.4 Design of Amplifiers