### UNIVERSITÀ DEGLI STUDI DI PAVIA

#### FACULTY OF ENGINEERING

Department of Electrical, Computer and Biomedical Engineering

PhD thesis in Microelectronics

# Highly Linear Filtering TIA for 5G wireless standard and beyond

Advisors: Prof. Rinaldo Castello Prof. Danilo Manstretta

PhD thesis of Nimesh Nadishka Miral

Academic Year 2021/2022

### **Declaration of Authorship**

I, , declare that this thesis titled, and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

#### UNIVERSITÀ DEGLI STUDI DI PAVIA

### Abstract

Facoltà di Ingegneria

Dipartimento di Ingegneria Industriale e dell'Informazione

#### Design of

by Nimesh Nadishka Miral

The demand for high data rates in emerging wireless standards is a result of the growing number of wireless device subscribers. This demand is met by increasing the channel bandwidth in accordance with historical trends. As MIMO technology advances, more bands and antennas are expected to be used. The most recent 5G standard makes use of mm-wave bands above 24GHz to expand the channel bandwidth. Channel bandwidth can exceed 2GHz when carrier aggregation is used. From the receiver's point of view, this makes the baseband filter's design, which is often a TIA, more difficult. This is due to the fact that as the bandwidth approaches the GHz range, the TIA's UGBW should be more than 5GHz and it should have a high loop gain up to high frequencies. A closed-loop TIA with configurable bandwidth up to 1.5GHz is described in this scenario. Operational Transconductance Amplifier (OTA) closed in shunt-feedback is the foundation of the TIA. The proposed OTA is based on FeedForward topology (FF) together with inductive peaking technique to ensure stability rather than using the traditional Miller compensation technique. The TIA is able to produce GLoop unity gain bandwidth of 7.5GHz and high loop gain (i.e. 27dB @ 1GHz) using this method. The mixer and LNA's linearity will benefit from this. Utilizing TSMC 28nm CMOS technology, a prototype has been created using this methodology. The output integrated noise from 20MHz to 1.5GHz is lower than  $300\mu V_{rms}$  with a power consumption of 17mW, and the TIA achieves In-band OIP3 of 33dBm.

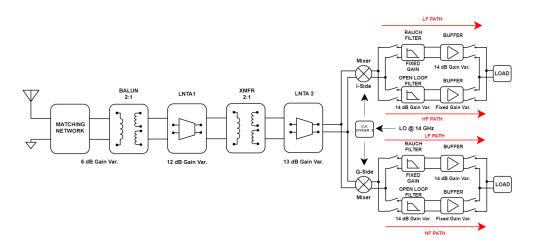

Additionally, a direct-conversion receiver for 5G applications is described. The 7GHz RF signal is down-converted to baseband by the receiver. Two cascaded LNTAs based on a common-gate transformer-based design make up the frontend. With an RF gain of 80mS and a gain variability of 31dB, it provides wideband matching from 6GHz to 8GHz. A double-balanced passive mixer is driven by the LNTA. The channel bandwidth from 50MHz to 2GHz is covered by two baseband paths. The first path, called as the low frequency path (LF), covers the channel bandwidth ranging from 50MHz to 400 MHz. In contrast, the second path, called as the high frequency path (HF), covers the channel bandwidth between 800MHz and 2GHz. Two baseband provide gain variability of 14dB, making the overall receiver able to have a gain configurability from 45dB to 0dB. Out-of-band (OOB) selectivity at 4 times the band-edge is greater than 33dB for each configurability. When the gain is at its maximum, the noise figure is less than 5.8dB, and the slope of the noise rise as the gain falls is less than 0.7dB/dB. The receiver guarantee an IB-OIP3 larger than 21dBm for any gain configuration. The receiver has been implemented in TSMC 28nm CMOS technology, consuming 51mW for LF path and 68mW for HF path. The measurement results are in perfect accordance with the requirements of the design.

## Contents

| 1        | $\mathbf{Evo}$ | lution | and Design Requirements of Wireless Standards                            | <b>5</b>  |

|----------|----------------|--------|--------------------------------------------------------------------------|-----------|

|          | 1.1            | Main   | Communication Metrics                                                    | 5         |

|          |                | 1.1.1  | Sensitivity and Noise Figure                                             | 6         |

|          |                | 1.1.2  | Non-Linearity                                                            | 7         |

|          | 1.2            | Evolut | tion of Wireless Generation                                              | 10        |

|          |                | 1.2.1  | Evolution from 1G to 3G                                                  | 11        |

|          |                | 1.2.2  | 4G LTE                                                                   | 13        |

|          |                |        | 1.2.2.1 MIMO                                                             | 14        |

|          |                |        | 1.2.2.2 Carrier Aggregation                                              | 15        |

|          |                | 1.2.3  | An evolution toward 5G                                                   | 15        |

|          |                | 1.2.4  | 5G                                                                       | 16        |

|          | 1.3            | Exam   | ple of Requirements                                                      | 17        |

|          |                | 1.3.1  | Sensitivity                                                              | 17        |

|          |                | 1.3.2  | Adjacent channel sectivity                                               | 18        |

|          |                | 1.3.3  | Specifications for 5G Receiver                                           | 19        |

|          |                | 1.3.4  | Conclusion                                                               | 20        |

|          |                |        |                                                                          |           |

| <b>2</b> | $\mathbf{Des}$ | ign of | Highly Linear TIA with 1.5 GHz of BW                                     | <b>21</b> |

|          | 2.1            | Gener  | al Consideration                                                         | 21        |

|          |                | 2.1.1  | Stability in Feedback System                                             | 24        |

|          | 2.2            | Desigr | n of TIA                                                                 | 25        |

|          | 2.3            | Desigr | n of OTA                                                                 | 26        |

|          |                | 2.3.1  | FeedForward Topology                                                     | 26        |

|          |                |        | 2.3.1.1 Passive zero creation with Inductive Peaking                     |           |

|          |                |        | technique $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 30        |

|          |                | 2.3.2  | OTA Design                                                               | 31        |

|          |                | 2.3.3  | TIA Stability                                                            | 35        |

|          | 2.4            | Measu  | rement Results                                                           | 38        |

| 3 | Full | Receiv  | er Arch   | itecture                               | <b>43</b> |

|---|------|---------|-----------|----------------------------------------|-----------|

|   | 3.1  | Propose | ed Receiv | ver                                    | 43        |

|   | 3.2  | Front-E | and       |                                        | 44        |

|   | 3.3  | High Fr | requency  | Baseband Path                          | 48        |

|   |      | 3.3.1   | Open-Lo   | op Filter                              | 48        |

|   |      | 3.3.2   | Wideban   | d TIA                                  | 50        |

|   | 3.4  | Low Fre | equency 1 | BaseBand Path                          | 51        |

| 4 | Mea  | sureme  | ent Resi  | lts of Full Receiver                   | 55        |

|   | 4.1  | Full Re | ceiver Ex | perimental Results                     | 55        |

|   |      |         |           | nent Results: High Frequency path      | 56        |

|   |      |         | 4.1.1.1   | Receiver Gain                          | 56        |

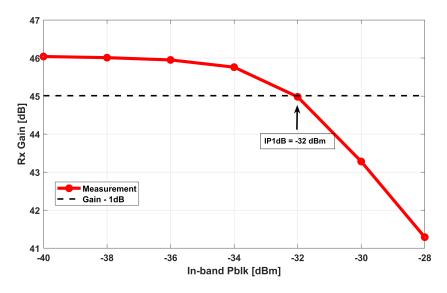

|   |      |         | 4.1.1.2   | Linearity and Compression Measurements | 58        |

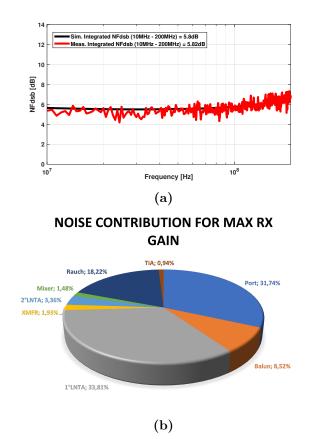

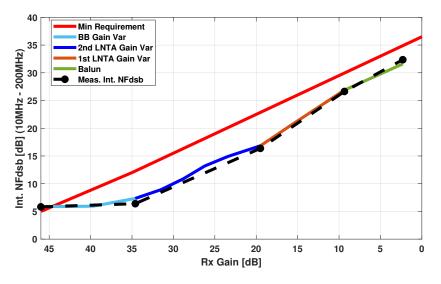

|   |      |         | 4.1.1.3   | Noise Performance                      | 59        |

|   |      | 4.1.2   | Measurer  | ment Results: Low Frequency path       | 61        |

|   |      |         | 4.1.2.1   | Receiver Gain                          | 64        |

|   |      |         | 4.1.2.2   | Linearity and Compression Measurements | 65        |

|   |      |         | 4.1.2.3   | Noise Performance                      | 67        |

|   | 4.2  | Receive | r Perform | nance Summary                          | 68        |

#### iv

## List of Figures

| 1.1  | An illustration of the relationship between sensitivity, SNR,     |    |

|------|-------------------------------------------------------------------|----|

|      | noise floor, and NF in the scenario that the receiver and an-     |    |

|      | tenna are matched.                                                | 6  |

| 1.2  | The IP3 (third-order intercept point) is defined as the intersec- |    |

|      | tion of the extended output power curves of the Fundamental       |    |

|      | and IM3 products on a log-scale                                   | 7  |

| 1.3  | The Description of IM3 falling onto desired band                  | 9  |

| 1.4  | Definition IIP3 as the intersect between the Fundamental and      |    |

|      | IM3 on log-log scale                                              | 11 |

| 1.5  | Schematic representation of carrier aggregation                   | 16 |

| 1.6  | ACS test for Operating Band n257                                  | 19 |

| 0.1  |                                                                   | 00 |

| 2.1  | Closed Loop TIA with big Input Capacitor.                         | 22 |

| 2.2  | Schematic representation of TIA with input referred voltage       | റെ |

| 0.9  | noise source                                                      | 23 |

| 2.3  | Output noise of TIA vs. $C_{IN}$                                  | 24 |

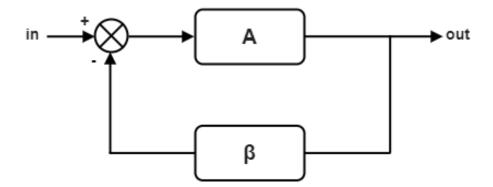

| 2.4  | Negative Feedback system.                                         | 24 |

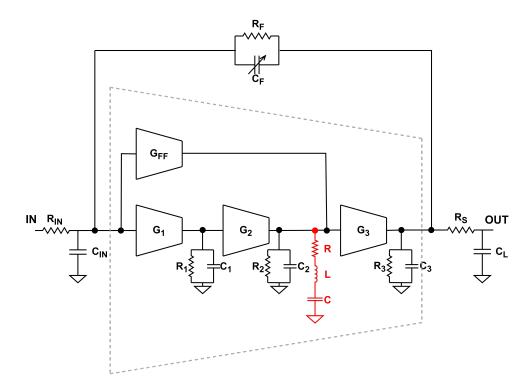

| 2.5  | The Schematic representation of the proposed TIA                  | 26 |

| 2.6  | The Schematic representation of the OTA with inductive peaking.   | 27 |

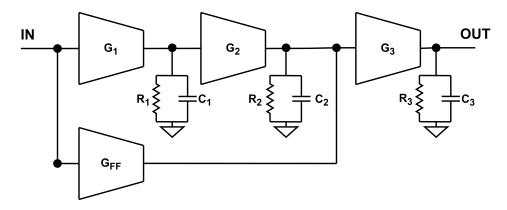

| 2.7  | The Block Diagram of FF Topology.                                 | 27 |

| 2.8  | The Block Diagram of The Proposed FF Topology                     | 28 |

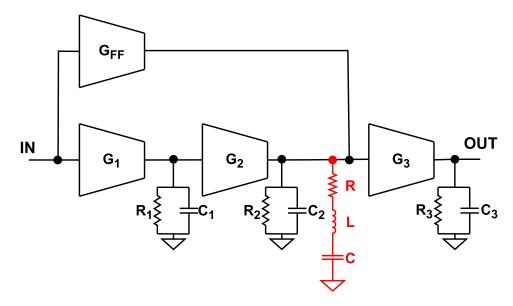

| 2.9  | The Block Diagram of The OTA with Passive Zero                    | 29 |

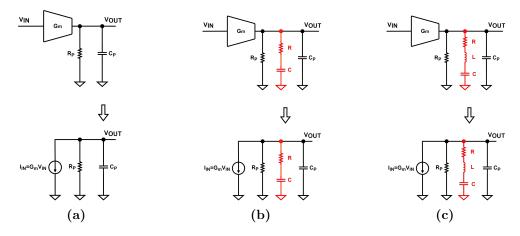

| 2.10 | Three simplified circuits to explain the different output loads   |    |

|      | of the FF/second stage: (a)Output load with the MOSFET's          |    |

|      | parasitic output resistance and capacitance; (b) output load      |    |

|      | with a zero cretaed by R and C; (c) output load employing         |    |

|      | inductive peaking.                                                | 30 |

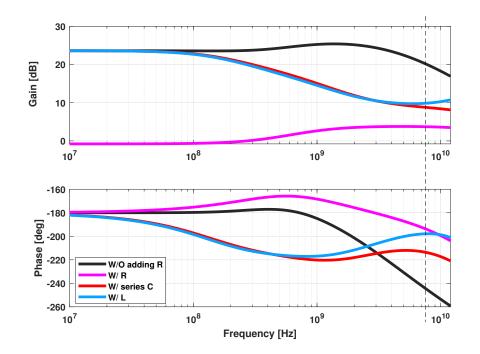

| 2.11 | The Effect of Inductive Peaking technique on the transfer func-   |    |

|      | tion of the FF stage                                              | 31 |

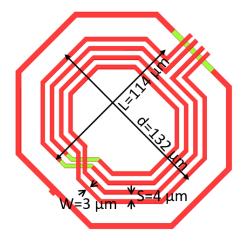

| 2.12 | Layout of Coupled Inductors.                                      | 32 |

|      |                                                                   |    |

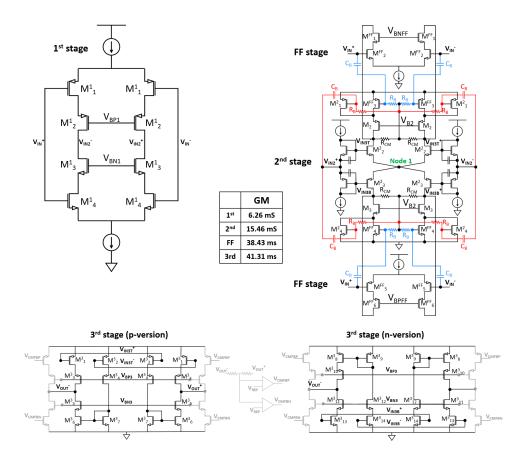

| 2.13 | The Complete Schematic of OTA.                                              | 33 |

|------|-----------------------------------------------------------------------------|----|

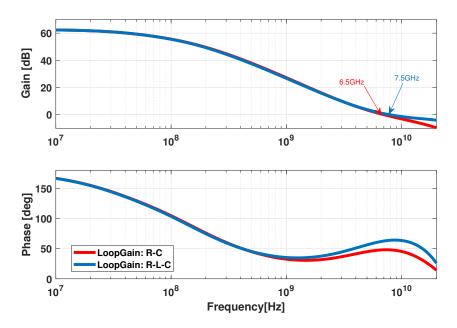

| 2.14 | The Response of the Loop gain with R-C and with R-L-C                       | 35 |

| 2.15 | The implemented TIA                                                         | 36 |

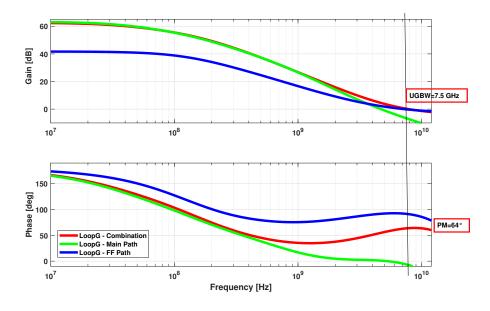

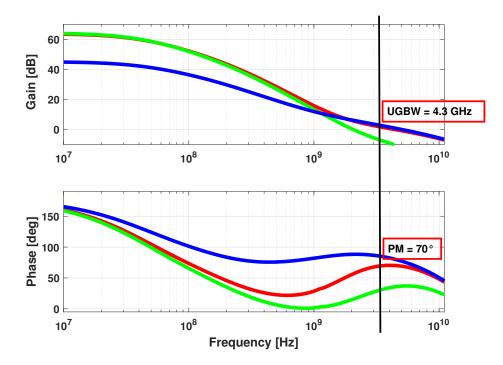

| 2.16 | Loop gain of the TIA.                                                       | 37 |

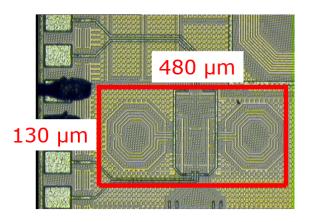

|      | Chip micro-photograph.                                                      | 38 |

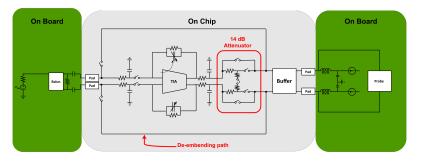

|      | Measurement setup for the stand-alone TIA.                                  | 38 |

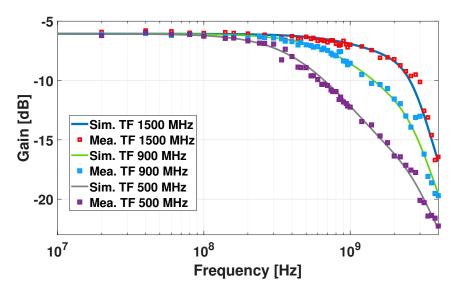

|      | The transfer function for different bandwidth configuration                 | 39 |

| 2.20 |                                                                             | 40 |

| -    | Input referred noise (up to $500MHz$ ).                                     | 41 |

| 9.1  |                                                                             | 49 |

| 3.1  | The block diagram of the implemented receiver                               | 43 |

| 3.2  | Simplified single-ended schematic of CG LNTA                                | 44 |

| 3.3  | The complete schematic of first LNTA                                        | 45 |

| 3.4  | The complete schematic of second LNTA                                       | 45 |

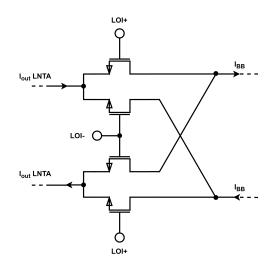

| 3.5  | The schematic of mixer (I-side)                                             | 47 |

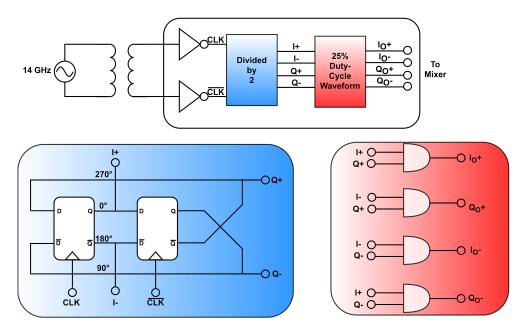

| 3.6  | 251% duty-cycle Divider                                                     | 47 |

| 3.8  | The complete schematic of open-loop filter with negative capac-             |    |

|      | itance                                                                      | 50 |

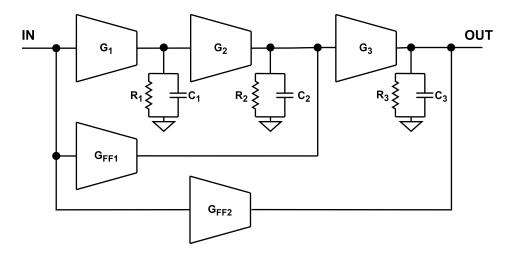

| 3.9  | The block diagram of the implemented TIA                                    | 51 |

| 3.10 | The Complete Schematic of OTA.                                              | 52 |

| 3.11 | The Loop Gain of the TIA.                                                   | 53 |

|      | The block diagram of low frequency baseband path                            | 53 |

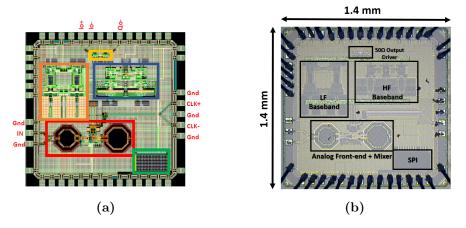

| 4.1  | (a) The layout of the full receiver. (b) The microphotograph of             |    |

| 4.1  |                                                                             | EG |

| 4.0  | the chip                                                                    | 56 |

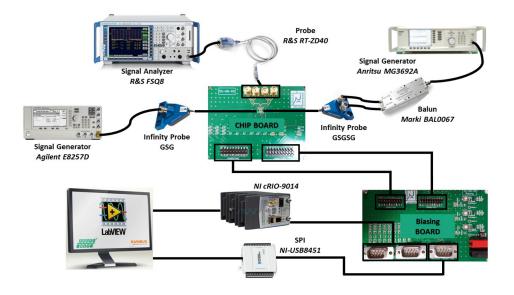

| 4.2  | The measurement setup for characterization of the receiver $P_{\text{rec}}$ | 57 |

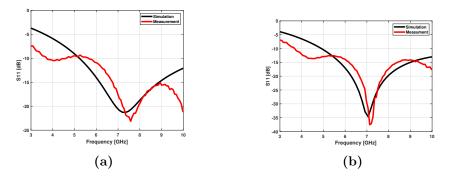

| 4.3  | Measurements of S11: (a) for max Rx gain (b) for min Rx gain.               | 57 |

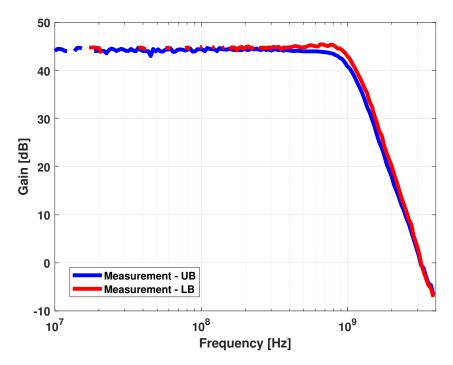

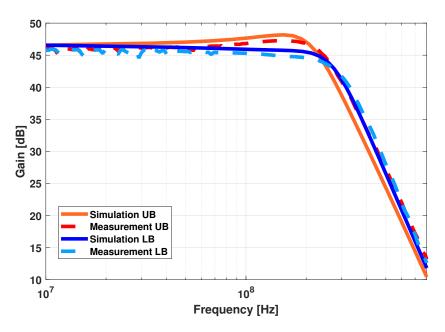

| 4.4  | The down-converted receiver gain for lower and upper band                   | 58 |

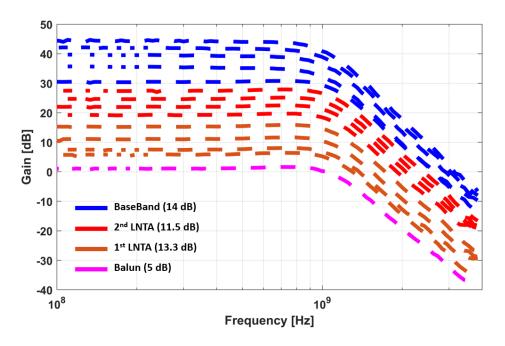

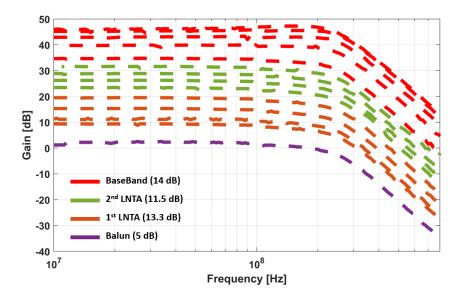

| 4.5  | The measured receiver gain variation for the HF-BB path                     | 59 |

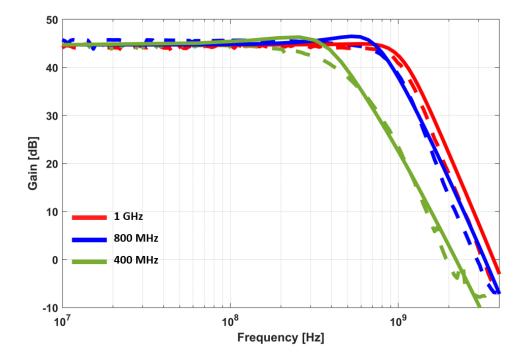

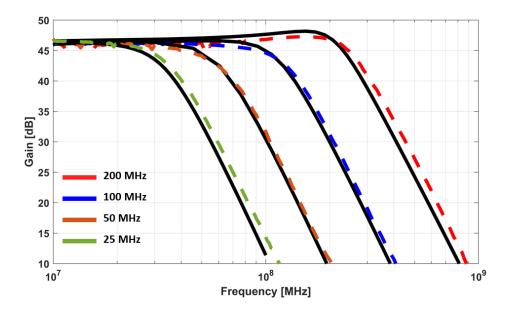

| 4.6  | The measured receiver bandwidth variation for HF-BB path by                 |    |

|      | changing the BW of second order open loop filter and TIA. $\ . \ .$         | 60 |

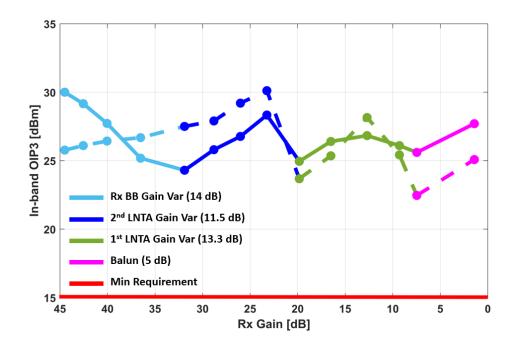

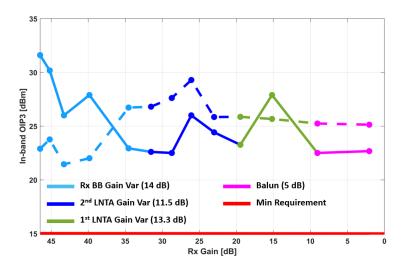

| 4.7  | The in-band OIP3 vs. receiver gain. The results are obtained by             |    |

|      | adding two tones at $f_{LO}$ +400MHz and $f_{LO}$ +500MHz so that           |    |

|      | the IM3 falls at 300MHz.                                                    | 61 |

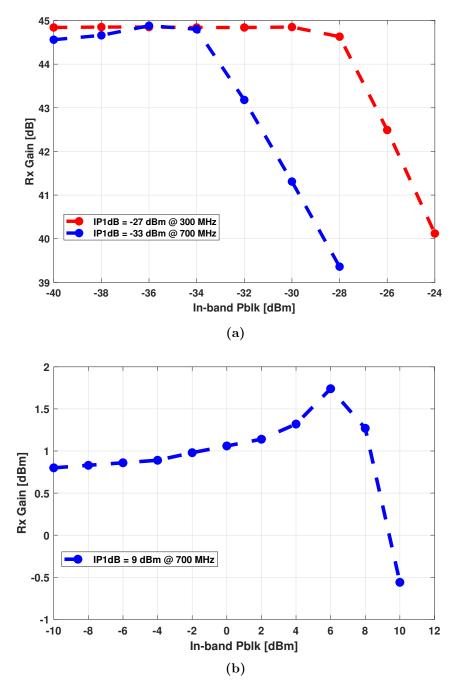

| 4.8  | (a) the in-band compression for maximum receiver gain with                  |    |

|      | blockers at $f_{blk} = f_{LO} + 700MHz$ and $f_{blk} = f_{LO} + 300MHz$     |    |

|      | (b) the in-band compression for maximum receiver gain with                  |    |

|      | blockers at $f_{blk} = f_{LO} + 700 MHz$ .                                  | 62 |

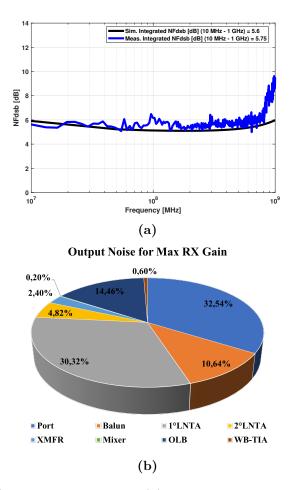

| 4.9  | (a) NFdsb max Rx gain (b) output noise contribution for max-                |    |

|      | imum Rx gain.                                                               | 63 |

|      |                                                                             |    |

vi

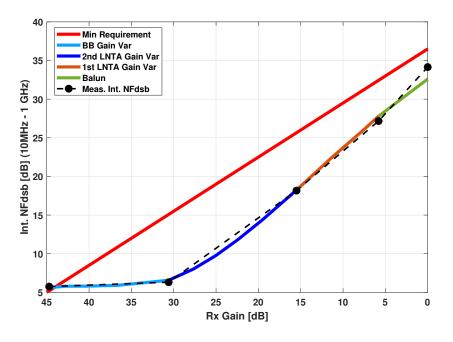

| 4.10 | The NFdsb vs. receiver gain.                                   | 64 |

|------|----------------------------------------------------------------|----|

| 4.11 | The down-converted receiver gain for lower and upper band      | 65 |

| 4.12 | The measured receiver gain variation for the LF-BB path        | 66 |

| 4.13 | The measured (dashed-line) and simulated (solid-line) receiver |    |

|      | bandwidth variation for LF-BB path by changing the BW of       |    |

|      | second order Rauch filter and TIA                              | 66 |

| 4.14 | The In-band OIP3 vs. receiver gain.                            | 67 |

|      | In-band compression for maximum receiver gain with blockers    |    |

|      | at $f_{blk} = f_{LO} + 160MHz$ .                               | 68 |

| 4.16 | (a) NFdsb max Rx gain (b) output noise contribution for max-   |    |

|      | imum Rx gain.                                                  | 69 |

| 4.17 | The NFdsb vs. receiver gain.                                   | 70 |

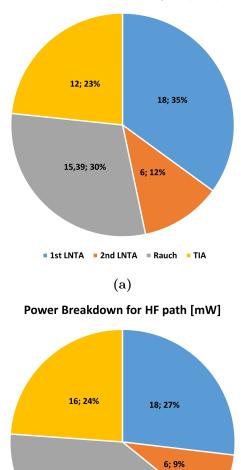

| 4.18 | (a) Power distribution for maximum Rx gain - LF path (b)       |    |

|      | Power distribution for maximum Rx gain - HF path               | 71 |

vii

### Introduction

Mobile communication systems are now widely used in people's daily lives. The tremendous increase in wireless system subscriptions has pushed the broad adoption of mobile devices over time and drastically increased the amount of data that networks must process. Even the services offered have expanded, moving beyond the most basic technologies like phone conversations to the most advanced ones like augmented reality and the Internet of Things (IoT). This is made feasible by the increasing data rate brought on by the development of mobile standards, starting with GSM and ultimately with 5G. Modern standards are improved in order to accomplish this by increasing the channel bandwidth, utilizing multiple operating bands, or using different antennas on the same device to send and receive data (MIMO). The 5G standard uses mmwave to provide channel bandwidth of 2GHz with carrier aggregation in order to enhance the bandwidth. These enhancements make transceiver design more challenging and impose very strict requirements on them, particularly on the receivers. As a result of using multiple bands, the receiver must be able to handle strong out-of-band (OOB) signals without compromising the desired signal. With many antennas, there is a possibility that the transmitted signal will be coupled with the receiving antennas, causing a significant interference in the receiver's input that could de-sensitize it. RF filters were employed in the classic receiver chain to reduce the unwanted OOB signals. Due to their size, these filters raise system complexity and chip cost. Due of these factors, creating a single wide-band receiver that can operate over many bands has become increasingly desirable in recent years. This necessitates paying close attention to the receivers' design since they must be able to handle strong, unfiltered OOB signals. The baseband portion needs special consideration since it must filter the unfiltered OOB signal without clipping or slewing while maintaining high linearity, which is more challenging as the channel bandwidth increases. The design of the Trans-Impedance Amplifier (TIA), which handles channel select filtering in the baseband region, is covered in this study. Operational Transconductance Amplifier (OTA) with parallel R-C feedback is the foundation of the TIA architecture. Inductive peaking is used in the design along with the FeedForward (FF) topology to provide stability. This method enables the TIA to function over a wide bandwidth (upto 1.5GHz) while maintaining high loop gain up to high frequencies, which guarantees good linearity (33dBm IB-OIP3).

A wide-band direct-conversion receiver design for 5G applications is also presented. The 7GHz RF signal is downconverted to baseband by the receiver. The receiver can provide more than 33dB of OOB selectivity at frequencies four times the band-edge, covering an RF bandwidth of 50MHz to 2GHz. The following summarizes how this thesis is structured:

**Chapter 1** outlines the key requirements and metrics that must be taken into account while designing a wireless receiver. The development of the wireless system is then described in great detail. This chapter presents the progression toward broad channel bandwidth and the specifications included in the most recent wireless standard (5G), with an emphasis on the receiver specifications.

**Chapter 2** for 5G and future generations, a closed-loop 1.5GHz bandwidth TIA is described in detail. Particular attention is devoted in the design of the OTA topology and the technique used to ensure the stability. Following the design presentation, the measurements of the prototype built using 28nm CMOS technology are given. The linearity and noise performance of this TIA are provided.

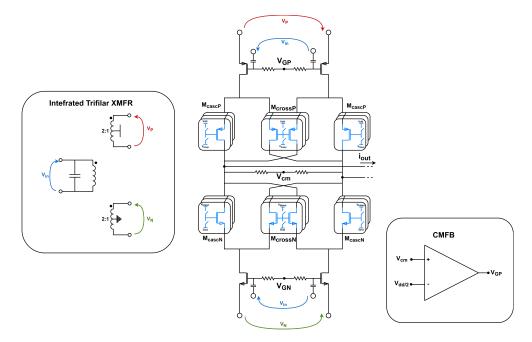

Chpater 3 the 5G wireless receiver design is described. Two cascaded LNTA with a cross-coupled CG architecture make up the front-end. The first LNTA is built around a trifiliar transformer, which provides matching and bias of the LNTA. The second LNTA, which was preceded by a transformer that provide current gain, so that reduces power consumption and enhances noise performance is described. The design of two baseband sections that cover the RF bandwidth range of 50MHz to 2GHz is discussed in the last section. The first path, which includes first order TIA after the Racuh filter, covers channel bandwidth from 50 MHz to 400 MHz. The second path, on the other hand, uses a 2nd-order open loop filter followed by a 1st order TIA to cover channel bandwidth from 800MHz to 2GHz.

**Chapter 4** presents the measurement results for the receiver discussed in Chapter 4. TSMC 28nm CMOS technology was used to implement the receiver.

The receiver measurement setup will be explained first, and the measurement results for both the high frequency (HF) and low frequency (LF) baseband paths will then be given. The measured receiver performance in comparison to the initial specifications will then be shown.

INTRODUCTION

### Chapter 1

## Evolution and Design Requirements of Wireless Standards

#### Abstract

In order to accommodate an increasing number of users and offer more services, wireless communications have evolved over time. To increase the data rate, several additional features have been created, necessitating complex wireless transceiver architecture. The main metrics for receiver design are covered in this chapter. An overview of the development of wireless standards is given, with special attention paid to the specifications necessary for designing a receiver for user equipment.

#### **1.1** Main Communication Metrics

The progress of the cellular system over the past decade has taken it from the First Generation to the Most Evolved Standard (5G) due to the growing number of subscribers in wireless communication systems. This progress requires a lot of operations that has to be performed both in analog and in digital domain. These could include data modulation and transmission on the transmitter (TX) side or signal detection and original data reconstruction on the receiver (RX) side. As number of wireless communication increases, the wireless environment becomes crowded, which resulted in strict requirements for each block in the receiver. Such requirements are provided in the standard and correspond to metrics that are unique to each block. To evaluate the wireless transceiver performances, certain fundamental design parameters are discussed in the following subsections.

#### 1.1.1 Sensitivity and Noise Figure

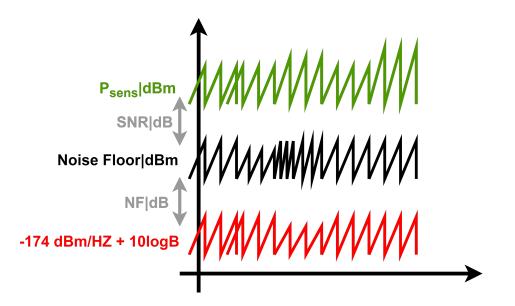

The receiver has to detect a small signal, but in the presence of significant noise, the signal cannot be detected with a quality that is acceptable. The parameter known as sensitivity specifies the minimum signal level that a receiver can detect while maintaining "acceptable quality" [1]. The signal-to-noise ratio that the system can tolerate determines the "acceptable quality". Sensitivity is defined as following:

$$P_{sens[dBm]} = P_{RS[dBm/Hz]} + NF_{[dB]} + 10logB + SNRmin_{[dB]}, \qquad (1.1)$$

where  $P_{RS[dBm/Hz]}$  is the noise power spectral density of the source (i.e. antenna),  $SNR_{min[dB]}$  is the minimum required Signal to Noise ratio at the output, and B is the channel bandwidth expressed in Hz. NF is the noise figure of the receiver defined as the ratio of the SNR at the input and at the output.

$$NF_{[dB]} = 10 \log\left(\frac{SNR_{in}}{SNR_{out}}\right).$$

(1.2)

Figure 1.1: An illustration of the relationship between sensitivity, SNR, noise floor, and NF in the scenario that the receiver and antenna are matched.

#### 1.1. MAIN COMMUNICATION METRICS

The system noise floor is represented by the first three terms in equation 1.1. If the receiver is matched to the antenna,  $P_{RS}$  corresponds to KT, which equals -174dBm/Hz. Therefore, the noise floor becomes:

$$P_{sens[dBm]} = -174dBm/Hz + NF_{[dB]} + 10logB.$$

(1.3)

Figure 1.1 shows this concept. The bit-error rate specified in the standard is what determines the minimum needed SNR, which is dependent on the employed modulation scheme. Since the detection becomes more sensitive to noise as the constellation points get closer, higher SNR is required. The maximum tolerable NF, which is the real requirement for the RF designer, can be calculated using the equation 1.1 after the minimum SNR and sensitivity are known.

#### 1.1.2 Non-Linearity

Non-linearity is another significant effect to take into account while designing the receiver. Although linear approximations could usually be used to model analog and RF circuits for small signal operations, nonlinearities typically result in interesting and important phenomena that cannot be predicted by

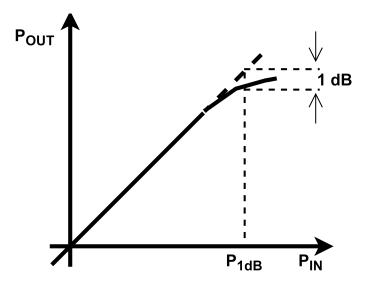

Figure 1.2: The IP3 (third-order intercept point) is defined as the intersection of the extended output power curves of the Fundamental and IM3 products on a log-scale.

small-signal models. The input/output characteristic of analog or RF circuit can be approximated with a Taylor's series expansion:

$$y(t) \approx \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t)$$

. (1.4)

where x(t) is the input signal, y(t) is the output signal,  $\alpha_2$  and  $\alpha_3$  are the second and third non-linear coefficient and  $\alpha_1$  is the small signal gain of the circuit when a small signal is applied. According to the equation 1.4, when a sinusoidal signal with frequency  $\omega_0$  is applied to the input of the circuit, a product of sinusoidal signals at integer multiple of  $\omega_0$  (harmonics) appears to the output. Substituting x(t) with  $A \cos(\omega_0 t)$  in 1.4, y(t) results in:

$$y(t) = \alpha_2 \frac{A^2}{2} + \left(\alpha_1 + \frac{3}{4}\alpha_3 A^2\right) A\cos(\omega_0 t) + \frac{1}{2}\alpha_2 A^2 \cos(2\omega_0 t) + \frac{3}{4}\alpha_3 A^3 \cos(3\omega_0 t)$$

(1.5)

In the equation 1.5, the first component on the right side is a dc quantity resulting from second-order non-linearity, the second term is referred to as the fundamental, and the third and fourth terms are the second and third order harmonics. It is clear from equation(1.5) that the gain of the fundamental depends not only on  $\alpha_1$ , but also on  $\alpha_3$ , which changes dramatically as amplitude (A) increases. Since  $\alpha_1$  and  $\alpha_3$  have the opposite sign in the fully differential situation, which is typically the case, the gain decreases as the amplitude increases. As a result, the input/output characteristic, as represented in figure 1.2, bends as the input amplitude increases. Therefore, the term associated with the third order distortion compress the gain. This effect is evaluated using a metric known as the 1-dB compression point, which is defined as the input amplitude level at which the gain decreases by 1 dB. The input 1-dB compression point is computed by taking the gain at the fundamental component  $\left(\alpha_1 + \frac{3}{4}\alpha_3 A_{IN,1dB}^2\right)$  and equate it to 1dB, resulting in  $A_{IN,1dB} = \sqrt{0.145 \left| \frac{\alpha_1}{\alpha_3} \right|}$ .

Strong undesired signal (interferer) present along with desired signal is another consequence that results in gain compression. To explain this effect,  $x(t) = A_0 cos(\omega_0 t) + A_1 cos(\omega_1 t)$  is substituted in the equation 1.4, and the term corresponding to the fundamental tone becomes:

$$y(t) = \left(\alpha_1 + \frac{3}{4}\alpha_3 A_0^2 + \frac{3}{2}\alpha_3 A_1^2\right) A_0 \cos(\omega_0 t) + \dots$$

(1.6)

This equation (1.6) makes it apparent that the gain of the desired signal decreases as the amplitude of the interference increases. Desensitization is the

Figure 1.3: The Description of IM3 falling onto desired band.

term of this effect, which reduce the SNR of the receiver.

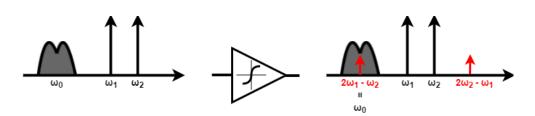

An other consequence of non-linearity is the third-order intermodulation (IM3). This occurs when the desired signal is present along with two tones at angular frequency  $\omega_1$  and  $\omega_2$ . If  $x(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t)$  is subsitute in 1.4, then y(t) becomes:

$$y(t) = \alpha_1 \left( A_1 \cos \omega_1 t + A_2 \cos \omega_2 t \right) + \alpha_2 \left( A_1 \cos \omega_1 t + A_2 \cos \omega_2 t \right)^2 + \alpha_3 \left( A_1 \cos \omega_1 t + A_2 \cos \omega_2 t \right)^3,$$

(1.7)

which has components (associated with third order non-linearity) at  $2\omega_1 - \omega_2$  and  $2\omega_2 - \omega_1$ :

$$y(t) = \dots + \frac{3}{4}\alpha_3 A_1^2 A_2 \cos(2\omega_1 t + \omega_2 t) + \frac{3}{4}\alpha_3 A_1^2 A_2 \cos(2\omega_1 t - \omega_2 t) + \frac{3}{4}\alpha_3 A_1 A_2^2 \cos(2\omega_2 t + \omega_1 t) + \frac{3}{4}\alpha_3 A_1 A_2^2 \cos(2\omega_2 t - \omega_1 t) + \dots$$

(1.8)

This mechanism is shown graphically in figure 1.3, where it is shown that the IM3 product may fall onto the desired band if  $\omega_0 = 2\omega_1 - \omega_2$ , which would reduce SNR. Receiver IM3 performance is evaluated using a two-tone test, in which two sinusoids of equal amplitude (A) are applied to the receiver input and the receiver IM3 is measured. From 1.8, it is clear that IM3 increases as  $A^3$ , which means that the relative ratio between the Fundamental and IM3 grows as  $A^2$ . Therefore, the IM3 is expressed in terms of IIP3 because it is preferable to have a quantity that is independent of amplitude A. This number represents the input amplitude level at which the amplitude of the input referred fundamental tone and the amplitude of the IM3 are equals at the output. The input level at which this occurs is known as the "input third intercept point (IIP3)", as shown in figure 1.4. In reality, higher-order nonlinearities may appear as amplitude A increases, causing the slopes of both the fundamental and IM3 functions to deviate from the expected value. As shown in figure 1.4, in order to measure IIP3, a low value of amplitude (A) is first applied to ensure that higher-order nonlinearities are negligible after this amplitude is increased. Then, the amplitudes of the fundamentals and IM3 products are plotted on a log-log scale, and these plots are extrapolated based on their slop (1 and 3). It must be noted that there should be a 3-dB increase in IM3 for every 1-dB increase in input amplitude in order to ensure that the signal keeps below higher-order nonlinearities. Using this method, IIP3 may be calculated as:

$$A_{IIP3[dBV]} = A_{[dBV]} + \frac{A_{[dBV]} - A_{IM3[dBV]}}{2}, \qquad (1.9)$$

where  $A_{IIP3[dBV]}$  is actual IIP3,  $A_{[dBV]}$  and  $A_{IM3[dBV]}$  corresponds to amplitude level of the fundamental and IM3 respectively, referred to the input of the receiver. The same formula can be used with the power level expressed in dBm.

Each wireless standard has a list of linearity tests that the receiver must fulfill. These indicate the amplitudes potential interferers as well as their distance from the desired signal band. From these specifications, linearity and compression requirements for the receiver can be constructed.

#### **1.2** Evolution of Wireless Generation

In the recent decades, wireless networks have developed continuously to meet the needs of an ever-expanding users and an increasing demand for data services. Different technology and new concepts have been applied to accelerate this development. The primary drivers behind this evolution are increasing data rates and larger system capacities. The Shannon Theorem [2], which states that the bit rate is directly proportional to the channel bandwidth, provides the answer to the question of how these requirements are satisfied. Therefore, increasing bandwidth is the simplest way to increase data rate. New mobile generations have evolved using this approach by increasing the channel bandwidth and allocating multiple channels from the same or different band to single user, based on the notion of channel aggregation.

Using a higher order modulation approach, which results in more bits per symbol, is an alternative method of increasing data rate. Because of the noise, denser constellations make it more difficult to detect bits. The design becomes more difficult as a result of the increased SNR requirements.

The employment of many antennas on both the transmitter and receiver sides is actually one of the core technologies of the most recent wireless system

**Figure 1.4:** Definition IIP3 as the intersect between the Fundamental and IM3 on log-log scale .

(MIMO). This technique enables simultaneous transmission and reception of several data signals over a single radio channel. More transmitting and receiving antennas enhance the link quality, reliability, and throughput between the transmitter and the receiver. The radio link's robustness could be increased using this technique, which would also increase SNR.

#### 1.2.1 Evolution from 1G to 3G

The mobile network's first generation (1G) was developed in 1980. It was developed to provide mobile services to mobile users and is based on analog transmission. 1G was composed of various standards, each based on a certain geographic region. For instance, Total Access Communication System (TACS) in western Europe, Nordic Mobile Telephone (NMT) in Scandinavian coun-

tries, and Advanced Mobile Phone (AMP) in North America. Similar characteristics were shared by these standards. As an example, the AMPS used FM modulation and operates in the 850 MHz cellular band with 832 channels that are separated by 30 kHz [3]. Frequency-Division-Duplexing (FDD), which uses two frequency bands for transmission and receiving, was employed by AMPS. The Frequency Division Multiple Access (FDMA) scheme, which assigns one channel per user and has poor capacity in crowded areas and requires huge frequency gaps to avoid interference, was used by 1G to address the multiple access problem. One channel is assigned to each user in the Frequency Division Multiple Access (FDMA) scheme, which was adopted by 1G to address the multiple access problem but has limited capacity in congested areas and requires wide frequency gaps to reduce interference. 1G cleared the way for the mass use of mobile phones despite other challenges that influence this network, such as poor hand-off reliability and safety issues [3] [4].

In 1990, the second generation (2G) was released. The primary improvement over 1G is that 2G is based on digital technology. This increased voice capacity and allowed for the adoption of new services including mobile fax, Short Messages Service (SMS), and voice mails. This standard is based on The Global System for Mobile Communication (GSM) [5], which was created as a unified wireless standard for Europe and has now become the most widely used cellular standard in the world. GSM uses FDD and works in a number of bands, including GSM900, GSM1800, and GSM1900. GSM uses GMSK modulation with a  $270 \, kbps$  data rate [6] and channels that are spaced  $200 \, kHz$ apart. GSM uses TDMA (Time Division Multiplexing Access), which is based on allocating the same channel in different time periods for different users, to increase the system capacity. These features enable the system capacity to be increased and the service to be extended to a large number of users. GPRS (General Packet Radio Service), also known as 2.5G, is a development of GSM. In contrast to GSM, which relied on circuit switching, GPRS introduced packet switching. In this case, packet switching divides data to transmit into different blocks known as packets and these packets are transmitted

across different paths to the receiver. This is in contrast to circuit switching, where a communication channel (circuit) is dedicated to two network nodes and it remains connected for the duration of the communication session. This limits the channel to the time required for packet transmission. MMS (Multimedia Messaging Service) and other internet-type services are made possible through GPRS. GSM was upgraded to EDGE (Enhanced Data Rates for GSM Evolution) in order to offer a higher data rate on a 200 kHz channel. This development is part of the 2.5G standard. The 8-PSK modulation scheme was used by EDGE to obtain a high data rate, which resulted in a data rate of  $473 \ kbit/s$  [7]. Because the points in the 8-PSK constellation are so close together, a higher SNR is needed to detect the received signal with a low BER (Bit Error Rate).

Code Division Multiple Access (CDMA) was used to establish the transition from second generation to third generation (3G). In CDMA, the signals can overlap in both time and frequency, in contrast to TDMA and FDMA. Each transmitter-receiver pair is given a special code at the beginning of every conversation. Before transmission, the data to be transmitted is multiplied by the assigned code, and the receiver uses the same code to decode the data. The total capacity of the system is better than TDMA and FDMA since multiple users can occupy the same bandwidth without interfering with one another, even though the code spreads the spectrum occupied by the transmitted signal (referred to as a "spread spectrum" approach). In the 3G standard, CDMA2000 and WCDMA (UMTS) were established as the two main standards. For example, the Universal Mobile Telecommunication System (UMTS) is characterized by 26 frequency bands that operate between 900 MHz and 2.1 GHz, with a 5 MHz channel spacing and the QPSK modulation scheme [8]. Data transmission at a rate of 2 Mbps was possible with UMTS. The demand for internet-type services, for which UMTS was designed, increased to the point that this standard needed to be updated. High-Speed Packet Access (HSPA) is the name of this standard, which offers a peak data rate of 14 Mbps [9].

#### 1.2.2 4G LTE

With the introduction of Long Term Evolution (LTE) in 2008, the fourth generation of mobile networks (4G) was launched in order to increase capacity compared to UMTS and meet the growing demand for data services and internet access. Primary objectives of LTE were to increase data speeds, enhance bit rates at the cell edge, improve spectral efficiency, ensure greater spectrum flexibility, and lower mobile power consumption. LTE has evolved into LTE-Advanced (Release 10) and LTE-Advanced-Pro (Release 13 and 14). The ability to switch to alternative access technologies (like UMTS and GSM) is granted in order to ensure seamless coverage. In order to enable global use, LTE is defined over a broad range of frequency bands, from 700 MHz to  $3.7 \, GHz$ . LTE provides larger channel bandwidth than earlier generations, continuing the patterns from the preceding generations. Variable carrier width, which has values ranging from 1.4 MHz to 20 MHz, in particular, offers more

flexibility. Consequently, this requires for a receiver with greater reconfigurability. LTE needs to solve multi-path transmission issues in order to reach higher data rates. In fact, due to inter-symbol-interference (ISI), signal quality decreases when the symbol time approaches the delay introduced by the channel. Orthogonal Frequency Division Multiplexing (OFDM) is a technique used by LTE to address this problem. This method involves first converting a high data rate stream from serial to N parallel streams with N times lower data rates. These are subsequently impressed on N different carrier frequencies, also known as sub-carriers. The total amount of spectrum occupation and data rate are the same as they were with single carrier modulation, but each of the N streams has a lower bit rate, making it possible to tolerate even more delay spread. In the first release of LTE (Rel. 8), only QPSK and 16QAM were used as modulation schemes. The most recent releases, however, combines these schemes with even higher-order modulation schemes, such as 64QAM and 256QAM.

Several significant LTE standard characteristics are discussed below:

#### 1.2.2.1 MIMO

According to the Multiple-Input Multiple-Output (MIMO) technique, LTE uses multiple antennas in Base Station (BS) and User Equipment (UE) to further increase possible data rate. Utilizing MIMO has the following three benefits:

- **Spatial Multiplexing:** By sending the data payload in a separate stream across spatially separated antennas, the data rate is increased. At the receiving end, multiple streams are combined into a single data stream using additional spatially separated antennas. This increases efficiency and bit rate by allowing the transmission of many signal streams in parallell using the available frequency and time resources.

- **Spatial Diversity:** Utilizes different transmissions over multiple antennas to increase signal quality and mitigate the effects of multi-path fading.

- Beam-forming: The linear arrays that will allow the antenna to focus on a specific area are likely to be used in this MIMO mode, which is the most complicated one. As a result, the individual UE will have a beam produced in their particular direction, reducing interference and increasing capacity.

In summary, MIMO, is an antenna technology that uses multiple antennas at the transmitter and receiver ends to enhance data rates and signal quality for 4G LTE. With the help of spatial multiplexing, antenna diversity, and beamforming, MIMO improves both signal quality and bit rate.

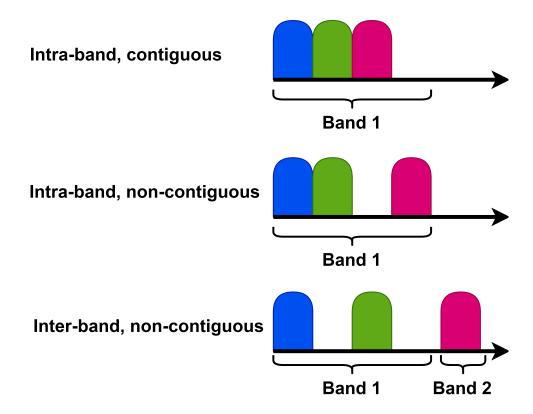

#### 1.2.2.2 Carrier Aggregation

In order to increase the channel bandwidth and subsequently the bit rate, carrier aggregation was introduced in LTE-Advanced. Component carriers (CC), are the names given to each aggregated carrier. The component carrier can be aggregated with a maximum of five component carriers, resulting in an aggregated bandwidth of 100 MHz. The component carrier can have a bandwidth of 1.4, 3, 5, 10, 15 or 20 MHz. There are numerous ways to aggregate the component carriers, but the simplest way is to group contiguous component carriers in the same band, a process known as intra-band contiguous aggregation. Separate carriers can be chosen in cases when this isn't a possibility. Figure 1.5 illustrates how they can come from the same band (intra-band non-contiguous carrier aggregation), but have gap or gaps in between or they may aggregate from separate band (inter-band carrier aggregation).

#### 1.2.3 An evolution toward 5G

Technologies beyond the fourth generation (4G) have being explored as it has become a commercial success. Release 13 and Release 14 have been introduced as the bridge from 4G to 5G. Compared to LTE-Advanced, in Release 13 a significant number of new features have been introduced. The opportunistic use of unlicensed spectrum is developing into a key addition to satisfy the increasing traffic demand, even as licensed spectrum continues to be 3GPP operators' top priority for delivering enhanced services and user experience. Operators will have the opportunity to employ unlicensed spectrum with a unified network thanks to licensed-assisted access. In LTE, carrier aggregation was only possible with up to 5 component carriers (CC), but with this release, 32 CCs could be aggregated, increasing data rates and making it easier to combine several CC from different bands. Release 13 significantly enhances cellular network support for Machine-Type Communications (MTC) and the Internet of Things (IoT). Full Dimension MIMO (FD-MIMO), which increases the number of antenna from 8 to 64, has also been introduced. V2X, a new class of services, is one of the new ones added in Release 14. Reduced latency is the primary objective of this standard. Given that emerging applications like IoT and V2X require low latency, LTE offers latency of less than 10 ms. However,

#### 16 CHAPTER 1. WIRELESS STANDARDS AND DESIGN METRICS

Figure 1.5: Schematic representation of carrier aggregation

1 ms over-the-air latency has been deemed to be a crucial requirement of 5G communication systems [10].

#### 1.2.4 5G

Recent releases of the 3GPP protocol have expanded its services to include fields like Machine Type Communication (MTC), Device-to-Device (D2D), and Vehicle Communication (V2X). These already offered services are expected to be improved by 5G, which will also expand the range of services provided to include augmented reality, digital TV, public safety, and drone communication [11]. Two frequency ranges have been established by the 3GPP in Release 15: Frequency range 1 (FR1) [12], which covers the range from 410MHz to 7.125GHz, and Frequency range 2 (FR2) [13], which covers the range from 24.25 to 52.6GHz. In comparison to 4G, the channel bandwidth has been enhanced up to 100MHz. While FR2, which operates in the mmwave frequency spectrum, has a channel bandwidth of 400MHz that may be increased by carrier aggregation to reach the GHz range.

Moving to mmWaves is difficult because small-wavelength waves attenuate more quickly, for example because of atmospheric conditions. However, smaller antenna array components can be arranged closely together due to shorter wavelengths. In the mmWave spectrum, it is practical to create antenna arrays of tens or even hundreds of antenna elements. In addition to compensating for the increased losses suffered by mmWaves, this method produces antenna systems with high antenna gains and narrow beams that may also reduce interference due to their narrow beams.

#### **1.3** Example of Requirements

This section includes some of the key requirements specified by the mobile standards as well as some quantitative examples from the most recent Releases. The RF receiver sensitivity and adjacent channel selectivity have been given special consideration.

#### 1.3.1 Sensitivity

Wireless standards specify a reference sensitivity power level (REFSENS) that must be transmitted to the two antenna ports in order to ensure that the throughput meets the specified criteria for the expected modulation and coding scheme, known to as the reference channel. For example, in 3GPP Release 15 [13], specifications are given for reference channels with low SNR that use QPSK modulation and a 1/6 coding rate. In this scenario, sensitivity is needed to guarantee a throughput of 95% of the maximum achievable, which translates to an SNR of -2.6dB. For each band and each permitted carrier bandwidth, sensitivity is described in the standard. The sensitivity necessary for power class 3 is shown in table 1.1. For instance, by using a 100MHz bandwidth with

| Operating band  | <b>REFSENS</b> (dBm) / Channel bandwidth |         |         |         |  |

|-----------------|------------------------------------------|---------|---------|---------|--|

| Operating ballu | 50 MHz                                   | 100 MHz | 200 MHz | 400 MHz |  |

| n257            | -88.3                                    | -85.3   | -82.3   | -79.3   |  |

| n258            | -88.3                                    | -85.3   | -82.3   | -79.3   |  |

| n260            | -85.7                                    | -82.7   | -79.7   | -76.7   |  |

| n261            | -88.3                                    | -85.3   | -82.3   | -79.3   |  |

Table 1.1: Reference sensitivity for power class 1

the n257 band and replacing the sensitivity value in 1.1, the necessary NF could be derived, leading to:

$$P_{sens[dBm]} = -85.3 = -173.8 + NF_{[dB]} + (-2.6) + 10log_{10}(100MHz) + IM_{[dB]},$$

(1.10)

the IM, or implementation margin, which stands for "implementation margin", is expected to be 2.5 dB in this testing condition and accounts for any non-idealities that can affect signal processing before the demodulator. Consequently, the NF needed to pass the test is 8.6dB.

#### 1.3.2 Adjacent channel sectivity

Adjacent channel selectivity (ACS) quantifies the receiver's ability to receive the desired signal in the desired channel, in the presence of an adjacent channel signal at a given frequency offset from the frequency of the desired channel, without degrading receiver performance. The receiver must meet the minimum specifications defined in a given standard. Tables 1.2 and 1.3, for example, show the specifications set forth for ACS for the FR1 and mmWave bands, respectively.

| RX        | Channel bandwidth |                    |        |         |        |  |

|-----------|-------------------|--------------------|--------|---------|--------|--|

| parameter | 10 MHz            | $15 \mathrm{~MHz}$ | 20 MHz | 40 MHz  | 50 MHz |  |

| ACS [dB]  | 33                | 33                 | 33     | 33      | 33     |  |

| RX        | Channel bandwidth |                    |        |         |        |  |

| parameter | 60 MHz            | 80 MHz             | 90 MHz | 100 MHz |        |  |

| ACS [dB]  | 33                | 33                 | 33     | 33      |        |  |

Table 1.2: ACS for FR1 bands with  $F_{DL} \ge 3300 MHz$  and  $F_{UL} \ge 3300 MHz$

| RX            | Channel bandwidth |         |         |         |  |  |

|---------------|-------------------|---------|---------|---------|--|--|

| parameter     | 50 MHz            | 100 MHz | 200 MHz | 400 MHz |  |  |

| ACS [dB] for  | 23                | 23      | 23      | 23      |  |  |

| band $n257$ , |                   |         |         |         |  |  |

| n258, n261    |                   |         |         |         |  |  |

| ACS [dB] for  | 22                | 22      | 22      | 22      |  |  |

| band n260     |                   |         |         |         |  |  |

Table 1.3: ACS for FR1 bands with  $F_{DL} \ge 3300 MHz$  and  $F_{UL} \ge 3300 MHz$

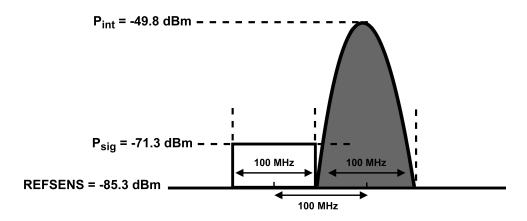

Figure 1.6: ACS test for Operating Band n257.

There are different test for ACS in the presence of an interferer on the adjacent channel. For bands in the FR1 and mmWave bands, these tests are different. However, in both cases, the desired signal is set 14 dB above REF-SENS, and the interference has a variable amplitude depending on the carrier bandwidth. In the case of mmWave, the interferer power is set at 35.5 dB above REFSES for the n257, n258 and n258 operating bands, and at 34.5 dB above REFSENS for the n270 operating band. Figure 1.6 illustrates the situation for the operating band n257 with a channel bandwidth of 100MHz as an example. This needs to be tested using an interferer with the same bandwidth and 35.5 dB more power than the REFSENS (-85.3dBm).

#### 1.3.3 Specifications for 5G Receiver

The sensitivity and selectivity specifications for a general 5G receiver have previously been defined. The receiver discussed in this thesis (chapter 3) has more exacting requirements than other receivers, not just in terms of noise and selectivity but also in terms of linearity, matching, and gain configuration. Table 1.4 lists the specifications for the receiver. The proposed receiver must support RF channel bandwidths ranging from 50 MHz to 2 GHz with a carrier frequency of 7 GHz. The receiver's gain should be programmable down to 0 dB, with a maximum gain of 45 dB. In all gain settings, the receiver should be able to achieve +15 dBm of IP3 at the output of the receiver. It should have a noise figure of less than 5 dB, and for every dB of gain reduction, the noise figure shouldn't rise by more than 0.7 dB.

| Item                      | Condition                          | Specs | Unit  |

|---------------------------|------------------------------------|-------|-------|

| Carrier Frequency         |                                    | 7000  | MHz   |

|                           | Mode (50,100,400,                  |       |       |

| RF Channel BW             | 400, 800, 1600 and 2000)           |       | MHz   |

| Input VSWR                | in all modes                       | 1.5   |       |

| Gain Control              | Max Gain                           | 45    | dB    |

| Range                     | Min Gain                           | 0     | dB    |

| Noise Figure              | @LNA input, max gain               | 5     | dB    |

| Noise Figure Slope        |                                    | 0.7   | dB/dB |

| Input P1dB                | Max Gain, inband                   | -39   | dBm   |

| Input P1dB                | Min Gain, inband                   | 6     | dBm   |

| OIP3                      | All gain step, $P_{RxOUT} = -8dBm$ | >15   | dBm   |

| Analog Filter Selectivity | From Bandwidth to 4 x bandwdith    | -33   | dB    |

| In-band Flatness          | in all modes                       | 1     | dB    |

| Power Consumption         | Max gain, Max BW                   |       | mW    |

Table 1.4: The Specification of the Receiver.

#### 1.3.4 Conclusion

This chapter provided an overview of the key wireless standard requirements as well as a discussion of how mobile networks have evolved. It should be obvious at this time that the trend is toward faster speeds, multiple bands, multiple antennas, and greater carrier bandwidths. Several bands and antennas make it highly desirable to have receivers that can function over multiple bands, which eliminates the need for extra RF filters and duplexers. This suggests a number of difficulties, particularly in terms of linearity. This problem is reflected in the baseband receiver design, which is often a Trans-Impedance Amplifier (TIA). A highly linear TIA design with large bandwidth will be shown in the following chapter.

### Chapter 2

## Design of Highly Linear TIA with 1.5 GHz of BW

#### Abstract

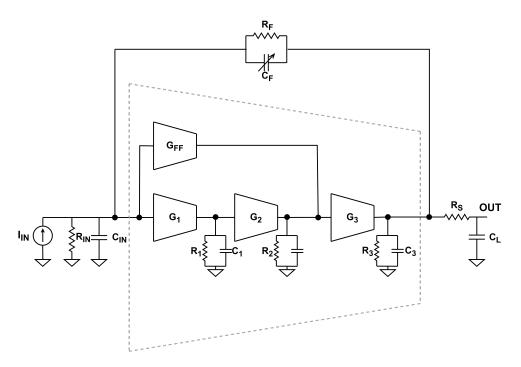

As previously said, the design of the baseband has become more difficult due to new wireless standards. One of the key reasons is that, when carrier aggregation is taken into account, the bandwidth may approach the GHz range. The operational transconductance amplifier (OTA), whose unity gain frequency impacts the accuracy of the transfer function and distortion, sets a restriction on the maximum bandwidth of a closed loop filter. Both of these concerns are influenced by the OTA gain vs. frequency relationship, thus it should be maximized up to the filter band-edge and maintained at a sufficiently high up to the frequency of the furthest blocker.

In this chapter a trans-impedance amplifier closed in feedback with a shunted R-C will be presented. In order to support both 5G and future wireless standards it has a programmable bandwidth up to 1.5 GHz. Feedforward compensation together with inductive peaking is used to ensure stabilization.

#### 2.1 General Consideration

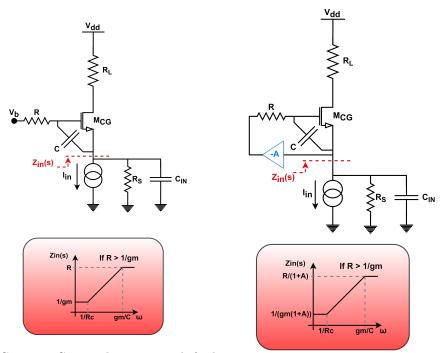

High linearity, very little noise, and low power consumption are all requirements for baseband filters. As previously mentioned, as RF frequencies increase, it becomes more difficult to meet these requirements. Either a transimpedance amplifier (TIA) filtering or higher order filter makes up the first block in the widely used current-mode receiver architecture following the mixer [14]. In addition to the requirements mentioned above, baseband must ensure low input impedance up to very high frequencies in order to preserve

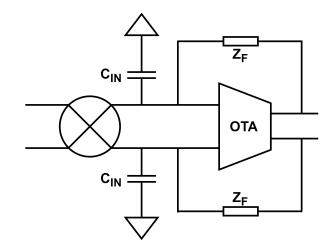

Figure 2.1: Closed Loop TIA with big Input Capacitor.

the RX front-end's linearity. Operational Transconductance Amplifier (OTA) closed in loop is the base for TIA implementation. Since the TIA's input impedance increases as gain decreases, which happens as frequency increases, A large shunt capacitance is connected to the TIA's virtual ground node to provide a low impedance path for high frequency components in order to address this problem, as shown in the figure 2.1. When there are strong OOB interferers present, this capacitor preserves the front-end IIP3 by providing low input impedance [15] and filters down converted interferers to improve TIA OOB IIP3.

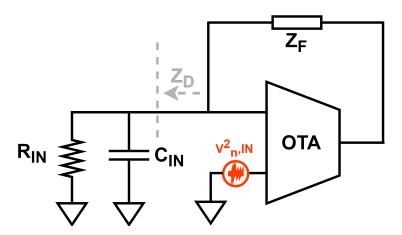

The issue with such a large capacitor is that the noise performance degrades. This capacitor could be of the order of pF as in [16] and [17]. Let's consider the figure 2.2, where the input referred voltage noise source is shown. By computing the noise transfer function (NTF) to the TIA output, the following result is obtained:

$$NTF = \frac{\overline{V_{n,OUT}^2}}{\overline{V_{n,IN}^2}} = \left| 1 + \frac{Z_F}{Z_D} \right|^2.$$

(2.1)

where  $Z_D$  is the driving impedance and  $Z_F$  is the impedance of the feedback network, as shown in figure 2.2. When  $Z_F$  is assumed to be parallel of RF and

Figure 2.2: Schematic representation of TIA with input referred voltage noise source.

CF, 2.1 transforms to the following:

$$NTF = \left|\frac{R_{IN} + R_F}{R_{IN}}\right|^2 \left|\frac{1 + s\frac{C_{IN}R_FR_{IN}}{R_F + R_{IN}}}{1 + sC_FR_F}\right|^2$$

(2.2)

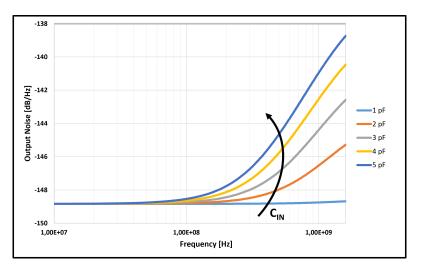

It is evident from equation 2.2 that NTF has a zero, which is given by the expression  $\omega_Z = 1/(C_{IN}(R_D||R_F))$ , which becomes  $\omega_Z \approx 1/(C_{IN}R_D)$  in the event that  $R_F >> R_D$ . As  $C_{IN}$  increases,  $\omega_Z$  shifts to lower frequencies, which worsens the TIA's in-band noise. This condition is depicted in figure 2.3 where it compares the output noise of TIA vs.  $C_{IN}$ . In this illustration, the cut-off frequency of TIA is set to 1.5 GHz, and  $R_{IN}$  is selected to be 100 Ohm. When 1pF is used,  $C_{IN}$  results in a zero at  $\omega_z = \omega_0$  in the NTF. Beyond this  $C_{IN}$  value, however, the integrated noise increases with the square of  $C_{IN}$  and becomes unacceptable. A 2<sup>nd</sup> order open loop filter is placed in front of the TIA as the proposed solution. Low input impedance should be guaranteed by the TIA in order to ensure strong linearity for an expanded frequency range of the open loop filter. The OTA must have a high loop gain up to GHz of frequency range and low power consumption in order to meet this requirement.

Figure 2.3: Output noise of TIA vs. C<sub>IN</sub>.

Figure 2.4: Negative Feedback system.

#### 2.1.1 Stability in Feedback System

As with any feedback system, stability is a crucial consideration in circuit design, especially when the bandwidth is as wide as it is in this case. If nothing is done, the circuit can become unstable and stop working as it should. Intuitively, the instability is caused by the excessive phase shift of the element present in the loop. Above a certain frequency, this excessive phase shift puts the circuit into positive feedback, which causes instability.

The needed unity gain frequency with GHz of bandwidth makes challenging the stabilizing of the amplifier.

Consider a general negative feedback system as shown in figure 2.4, the closed

#### 2.2. DESIGN OF TIA

loop transfer function can be expressed as follows:

$$G(s) = \frac{A(s)}{1 + \beta A(s)},\tag{2.3}$$

The amplifier's open-loop gain is represented by the quantity  $A\beta$ ; if  $A\beta$  is significantly higher than 1, the feedback network  $\beta$  alone decides total transfer function in the equation 2.1. It should be noted that 2.1 goes to infinity if  $\beta A(s = j\omega) = -1$ . The circuit can boost its own noise up to the point when it starts to oscillate. Alternatively said, the circuit might oscillate at frequency  $\omega_1$ . As a result, the condition in which the circuit may oscillate can be written as follows:

$$\begin{aligned} |\beta H(j\omega_1)| &= 1, \\ \angle \beta H(j\omega_1) &= -180^\circ. \end{aligned}$$

$$(2.4)$$

The 2.4 is called "Barkhausen's criteria". Since the negative feedback adds an additional 180° phase shift, the total phase shift is now 360°. This transforms the feedback into a positive one causing instability. Therefore, the total phase shift for  $\beta A = 1$  should be more positive than  $-180^{\circ}$  to prevent instability.

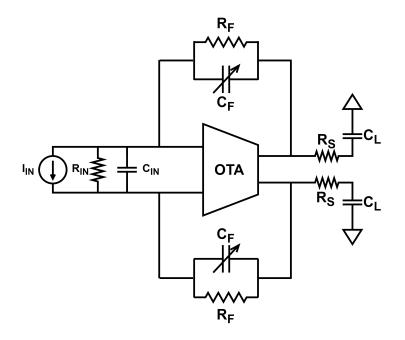

#### 2.2 Design of TIA

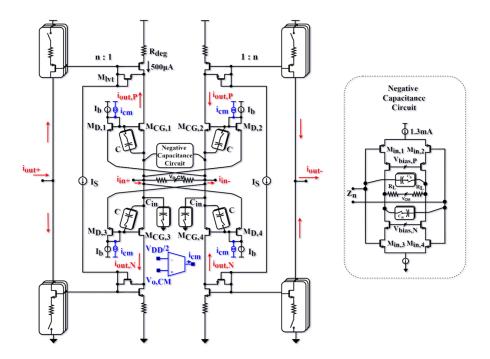

As shown by figure 2.5, the proposed TIA is based on an operational transconductance amplifier (OTA) with a parallel R-C feedback network. The implemented TIA should have a bandwidth of up to GHz, requiring several GHz of unity gain bandwidth for the OTA. Additionally, the TIA should have excellent linearity, which means the OTA needs a high loop gain for a wide frequency range. In essence, there are two techniques to increase the gain of the OTA: cascading, which involves utilizing a multi-stage amplifier, and cascoding, which means stacking more transistors on top of one another in a single-stage amplifier to increase the output resistance, which increases the gain. Cascoding is very challenging in low voltage environments. Since stacking additional transistors reduces the voltage headroom available for transistors to operate in the proper biasing condition in the presence of a significant output swing of the signal. Therefore, using a multi-stage amplifier is the only way to increase the gain. The main disadvantage of this approach is that it causes an extra phase shift in the frequency response since each stage of the cascade acts as a capacitive load for the previous stage. Therefore, frequency compensation is crucial when using a multi-stage amplifier.

In this work, an unconventional Feed-Forward architecture has been used to

Figure 2.5: The Schematic representation of the proposed TIA.

implement an OTA with three stages, and inductive peaking has been used to guarantee stabilization [18] [19], as illustrated in figure 2.6.

#### 2.3 Design of OTA

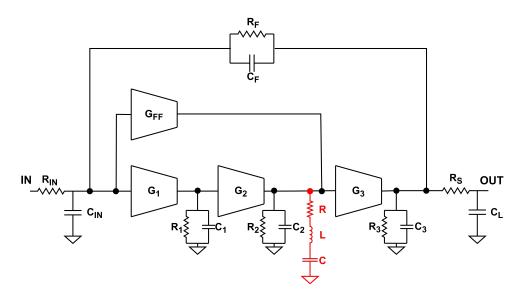

As mentioned above, the OTA was designed using an unconventional feedforward topology, as illustrated in figure 2.6, in order to achieve wide bandwidth and ensure loop stability over a broad frequency range.

#### 2.3.1 FeedForward Topology

As was already mentioned, OTA with three stages has been used in this work. Stability issues arise due to the phase shifts introduced by each additional stage. There have been numerous compensating methods for multi-stage amplifiers documented in the literature [20]. The most traditional one employs pole splitting (Miller effect) to increase the non-dominant pole's frequency while pulling back the dominant pole to a sufficiently low frequency. However, this restricts the bandwidth that may be employed, particularly for a large capacitive load, unless very high power consumption is used in the output

Figure 2.6: The Schematic representation of the OTA with inductive peaking.

Figure 2.7: The Block Diagram of FF Topology.

stage to force the second pole out sufficiently. Additionally, the possible gain at frequency near to the UGBW is constrained by the -20dB per decade form of the frequency response.

The feedforward topology is a topology that can achieve high gain at high frequency and ensure stability even for a very large UGBW.

In general, the number of FF path needed to introduce the necessary zeros to

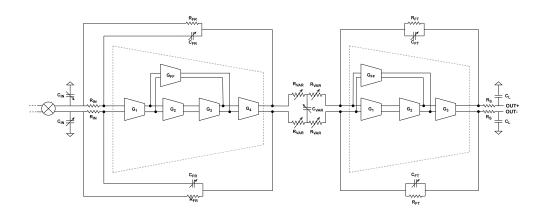

ensure stability is equal to the number of stages in the main path minus one, as shown in figure 2.7. A fifth order structure using this topology was used to build a continuous-time sigma-delta ADC sampled at 8 GHz using 28 nm CMOS technology [21]. The amplifier used in the integrators has a unity gain frequency of 6.7 GHz and a gain of 28 dB at 1 GHz, however it consumes more than 135 mW. The bottom FF stage dissipates a substantial amount of the power (40 mW). In order to ensure rail to rail output swing, this stage needs an extremely high gm and cannot benefit from current re-use through element stacking. The topology proposed employs a third order FF topology, shown in figure 2.8, and eliminates the outer FF path of figure 2.7. The FF path defines the unity gain frequency and phase margin, while the main path provides the most of the gain. In order to avoid limiting of the output swing, the FF path is connected from the OTA input to the input of the last stage. Compared to the outer FF stage in figure 2.7, this topology uses less power.

Assume that the main path has three stages with DC gains  $A_1$ ,  $A_2$ , and  $A_3$  each introducing a pole at  $\omega_{P1} = 1/R_1C_1$ ,  $\omega_{P2} = 1/R_2C_2$  and  $\omega_{P3} = 1/R_3C_3$ , respectively. The FF stage, on the other hand, has a DC gain  $A_{FF}$  and shares  $\omega_{P2} = 1/R_2C_2$  with the second stage. The transfer function can be easily calculated and is expressed as follows:

$$TF(s) = \frac{(A_1 A_2 + A_{FF}) \left(1 + \frac{A_{FF} s}{(A_1 A_2 + A_{FF}) s}\right) A_3}{(1 + s/\omega_{P1}) (1 + s/\omega_{P2}) (1 + s/\omega_{P3})}.$$

(2.5)

The position of the zero that the FF path introduces can be calculated using the 2.5:

$$\omega_{Z1} = -\omega_{P1} \left( 1 + \frac{A_1 A_2}{A_{FF}} \right) \approx -\frac{g m_1}{C_1} \frac{g m_2}{g m_{FF}}.$$

(2.6)

Figure 2.8: The Block Diagram of The Proposed FF Topology.

Figure 2.9: The Block Diagram of The OTA with Passive Zero.

According to 2.6, the location of the zero is approximately equal to  $\alpha$  times the GBW product of the first stage, where  $\alpha$  is the ratio of the second stage's to the FF stage's transconductance. It is also obvious that there will be a tradeoff between the power consumption and the possible UGBW as the location of the zero increases correspondingly to the product of the first and second stage's transconductance. Since there are three stages in the main path, which correspond to three poles, and only one zero is introduced by the FF stage, there may still be stability problems. There are two ways to solve this problem: the first is to move the pole associated to the second and FF stage beyond the unity gain frequency ( $\omega_u$ ), and the second is to add another zero. The first option is not feasible because, in order to move beyond  $\omega_u$ , output resistance must be very low, which causes the OTA gain to drop to an unacceptable level. As a result, the second method is used, passively producing the zero while maintaining gain and saving power, as shown in figure 2.9. In addition, using inductive peaking improves the unity gain bandwidth.

The relationship between  $\omega_u$  and the zero determines the stability of the opamp. Since  $\omega_u$  is approximately equal to  $\frac{gm_{FF}Rgm_3}{C_L}$  in the first order, As a result, the ratio is  $\frac{\omega_u}{\omega_Z} = \frac{gm_{FF}}{gm_1} \frac{gm_3}{gm_2} \frac{C_1}{C_L} gm_{FF}R$ . Given that the other terms in this expression can be precisely controlled,  $gm_{FF}R$  is crucial. A replica circuit could be used to adjust the bias current that results in the right  $gm_{FF}R$  in order to solve this problem.

**Figure 2.10:** Three simplified circuits to explain the different output loads of the FF/second stage: (a)Output load with the MOSFET's parasitic output resistance and capacitance; (b) output load with a zero cretaed by R and C; (c) output load employing inductive peaking.

#### 2.3.1.1 Passive zero creation with Inductive Peaking technique

In order to comprehend the advantage of the inductive peaking method. Consider the scenario in figure 2.10a, where there is no load adjustment. Figure 2.11 illustrates the transfer function of the FF stage in this scenario. As can be seen, the phase shift causes a poor phase margin (24°). As previously said, moving the pole associated to the second and FF stage beyond  $\omega_u$  will improve the phase margin. This may be accomplished by placing a small resistance in parallel, but doing so reduces the overall gain of OTA [Fig.2.11]. A capacitor in series with the resistor might be added, as illustrated in figure 2.10b, to maintain gain up to the frequency of interest. The phase margin, as illustrated in figure 2.11, is improved by this method and it becomes 48°.

Inductive peaking is utilized to reduce the phase margin to a level acceptable [Fig.2.10c]. For  $\frac{V_{OUT}}{V_{IN}}$ , the inductive peaking technique provides a transfer function of third order. However, given that C is more than ten times larger than C<sub>Par</sub>, it is plausible to suppose that C can be replaced by a short circuit close to  $\omega_u$ , leading to the following simplified transfer function:

$$\frac{V_{OUT}}{V_{IN}}(s) = -G_m \frac{R_{Par}(R+sL)}{(R+R_{Par}) + s(C_{Par}R_{Par}R+L) + s^2 L C_{Par}R_{Par}}.$$

(2.7)

Figure 2.11 illustrates how the R||RP-CP pole causes a 35-degree phase shift around  $\omega_u$  in the absence of an inductor (L). A 1.2nH inductor has the effect

Figure 2.11: The Effect of Inductive Peaking technique on the transfer function of the FF stage.

of causing the phase to change more slowly before the resonant frequency but more quickly after. This leads  $\omega_u$  to grow by 1GHz (from 6.5 to 7.5 GHz), and it also produces a 19° phase shift around  $\omega_u$  (i.e. 7.5 GHz).

The area is the problem with employing an inductor. Generally, the area is influenced by the inductance value, which is connected to the position of the zero and, eventually, to the desired UGBW. Smaller area is achieved, constructively coupling the two differential inductors to maximize their resulting value, as shown in figure 2.12. Additionally, since a high quality factor is not necessary, narrow windings are used. The inductor dominates the OTA area in the situation under consideration. However, as the UGBW is extended, the inductor area will decrease and the benefits of increased bandwidth will be even higher.

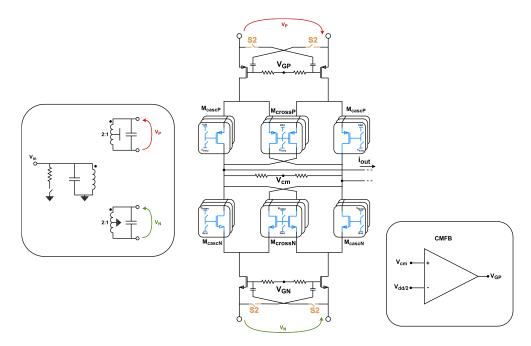

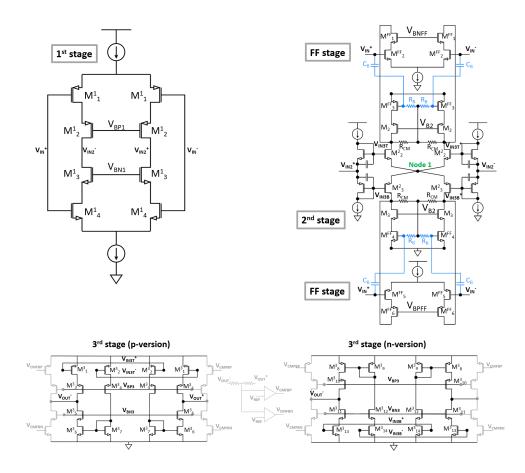

# 2.3.2 OTA Design

The OTA is designed using a third order FF architecture, whose complete schematic is shown in figure 2.13, to achieve high loop gain and preserve good

Figure 2.12: Layout of Coupled Inductors.

linearity.

The first stage is a high gm class A complementary p-n structure. The transistor sizes are selected to bias in a deep sub-threshold region, so as to have a high gm/I ratio. For a high DC gain, the input differential pairs are cascoded. Its small signal voltage gain is equal to the output impedance times the transconductance (gm) of the input transistors  $M_1^1$  and  $M_4^1$ . Consequently, the expression for small signal voltage gain is:

$$A_v = (gm_1 + gm_4) R_{out}, (2.8)$$

where  $R_{out}$  is the parallel of  $gm_2 R_{ds,2} R_{ds,1}$  and  $gm_3 R_{ds,3} R_{ds,4}$ .

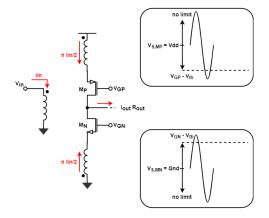

Class-AB low-gain wideband amplifier makes up the second stage. A class AB behavior is required because, in the event of a large signal present at the band edge or, or even worse, outside the band, such as a large current at 4 GHz, the last stage should be able to absorb the current even if the signal swing is filtered out since it is outside the band. At the output of the second stage, a class AB behavior is required in order to avoid entering into slewing and preventing early compression because a certain voltage swing is required at the input of the last stage in order to absorb large current.

By considering that Node 1 behaves as ground for differential signals, its operational principle can be understood. The output resistance multiplied by the sum of the  $M_2^2$  and  $M_3^2$  transconductances results in the small signal voltage

Figure 2.13: The Complete Schematic of OTA.

gain. It can be expresses in the following way:

$$A_{v} = (gm_{2} + gm_{3}) \left( R_{outT} || R_{outB} \right), \qquad (2.9)$$

where  $R_{outT}(R_{outB})$  is the parallel combination of the resistance seen by the drain of  $M_2^2$  and  $M_2$  ( $M_3^2$  and  $M_3$ ).

A boosting capacitor is placed between the input and the gate of the load transistor at the section of the schematic that is highlighted in red. Intuitively, as the frequency increases,  $C_B$  turns into a short circuit and feeds the input signal to the load transistor as well, taking use of the load transistor's transconductance. This results in a multiplication of the total equivalent gm by about a factor of two. This increases the phase margin and expands the bandwidth by creating a zero-pole doublet separated by an octave.

$$\omega_{Z} = \frac{1}{C_{B}R_{B}\left(1 + \frac{gm_{1}^{2}}{gm_{2}^{2}}\right)} \quad and \quad \omega_{P} = \frac{1}{C_{B}R_{B}}.$$

(2.10)

Two resistors  $(R_{CM})$ , each with a value of  $50k\Omega$ , are connected between the output node and the gate of the load transistors  $(M_1^2 \text{ and } M_4^2)$  to provide the common mode feedback (CMFB). Large resistance was chosen because, for differential signals, these two resistances appear parallel to the output node's resistance; otherwise, choosing a small value would result in a small voltage gain.

The second stage has two differential outputs, one at the drain of the pmos load transistors and the other at the drain of the n-mos load transistors, as illustrated in figure 2.13. Conceptually, the FF stage might also make use of p-n stacking (i.e.  $M_2^{FF}$  and  $M_5^{FF}$  could be stacked). If the input transistors are not cascaded, the large biasing current would reduce the gain of the second stage. Due to supply voltage limitation, cascoding translating into using two parallel FF stages, one with n-mos and the other with p-mos input transistors. Even in the FF stage, the boosting capacitor (CB) has been included (drawn in blue); in this instance, the load transistors  $(M_3^{\acute{F}F}$  and  $M_4^{FF})$  are driven by the input of the OTA, as opposed to the second stage, where they are driven by the signal from the output of the first stage. The p-mos and n-mos load transistors of the second stage and of the FF stage are merged together and drive the complementary p-n push-pull output stage. Figure 2.14 shows the effect of the inductive peaking technique on the overall loop gain when compared to the solution using only R-C. This shows a phase margin improvement of almost 20 degrees.

The third stage, or last stage, is a class AB amplifier to maximize the output driving capacity. In order to connect them directly to the two outputs of the second/FF stage, two parallel class AB amplifiers have been implemented, one with n-mos input transistors and the other with p-mos input transistors, so as to have 4gm at output. Let's only take into consideration the design with n-mos input transistors in order to comprehend its operation principle. The transistors  $M_{13}^3$  are controlled by the previous stage, whereas transistors  $M_8^3$  are driven by a current mirror made up of transistors  $M_{14}^3$  and  $M_9^3$ . The quiescent current of the class AB stage can be controlled very precisely, being set through a current mirror. Common mode feedback circuits are still necessary but only to compensate for the mismatches between the p-mos and n-mos

Figure 2.14: The Response of the Loop gain with R-C and with R-L-C.

current mirrors.

An extremely low common mode gain are the major benefit of implementing a n only (p only) output stage. This is crucial to stabilize the common mode response of the OTA, since the FF path is positive feedback for common mode signal.

The common mode voltage of the output nodes is set by the common mode feedback (CMFB) circuit of Figure 2.13 (Drawn in Gray). The output's common mode voltage is extracted using two identical resistors with values of  $50k\Omega$ , and it is then compared to a reference voltage of vdd/2. In order to reduce the error between the reference voltage and common mode voltage, the output of the CMFB amplifier regulates the current in the two branches of the output stage through the two generators controlled by  $V_{CMFBP}$  and  $V_{CMFBN}$ . The CMFB amplifier is implemented through a differential pair with differential-to-single-ended conversion.

### 2.3.3 TIA Stability

Figure 2.15 reports the implemented TIA. Even if the implemented version is fully differential, the single ended version is reported for simplicity's sake.

Figure 2.15: The implemented TIA.

| Value     | Unit                                   |

|-----------|----------------------------------------|

| 1         | $k\Omega$                              |

| 90        | fF                                     |

| 530       | Ω                                      |

| 180 - 530 | fF                                     |

| 500       | fF                                     |

| 50        | Ω                                      |

|           | 1     90     530     180 - 530     500 |

Table 2.1: The design parameter of the implemented TIA

Table 2.1 lists the value of passive components utilized in TIA. The cut-off frequency of the TIA is specifically determined by the values of  $R_F$  and  $C_F$ , and  $C_F$  is a tunable capacitor that is used to modify the TIA's closed loop bandwidth. As previously stated,  $R_{IN}$  and  $C_{IN}$  stand in for the driving impedance of the prior stage. While  $C_L$  represents the load capacitance, which represents

Figure 2.16: Loop gain of the TIA.

| Corner     |      | TT  |     |     | SS |     |     | $\mathbf{FF}$ |     |      | $\mathbf{SF}$ |      |      | $\mathbf{FS}$ |     |

|------------|------|-----|-----|-----|----|-----|-----|---------------|-----|------|---------------|------|------|---------------|-----|

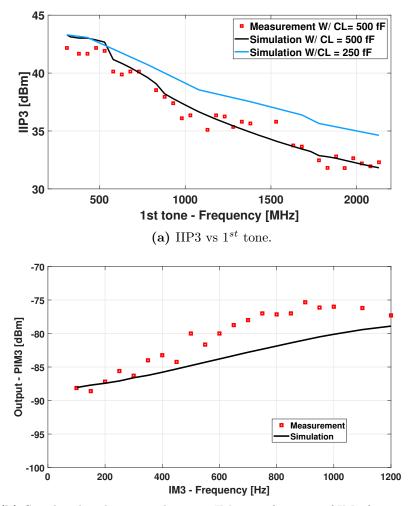

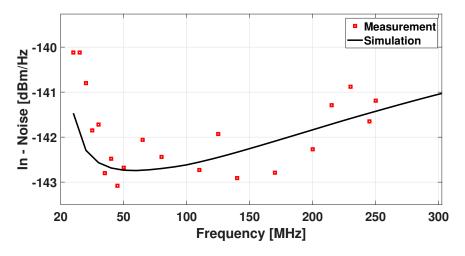

| Temp. [C]  | -50  | 27  | 100 | -50 | 27 | 100 | -50 | 27            | 100 | -50  | 27            | 100  | -50  | 27            | 100 |