### UNIVERSITÀ DEGLI STUDI DI PAVIA

## DIPARTIMENTO DI INGEGNERIA INDUSTRIALE E DELL'INFORMAZIONE

DOTTORATO DI RICERCA IN MICROELETTRONICA XXIX CICLO

## HIGH DENSITY ANALOG CIRCUITS FOR SEMICONDUCTOR PIXEL DETECTORS

### **Tutor:**

Prof. Lodovico Ratti Prof. Gianluca Traversi

### **Coordinatore del Dottorato:**

Chiar.mo Prof. Guido Torelli

Tesi di Dottorato di Francesco De Canio

Anno Accademico 2015/2016

# \_CONTENTS

1

### Introduction

| 1        | ASI | C requ | uirements for the CMS pixel detector at the HL-                |           |

|----------|-----|--------|----------------------------------------------------------------|-----------|

|          | LH  | С      |                                                                | 3         |

|          | 1.1 | The C  | MS experiment at the LHC                                       | 3         |

|          |     | 1.1.1  | Large Hadron Collider                                          | 3         |

|          |     | 1.1.2  | Overview of the CMS Experiment                                 | 5         |

|          |     | 1.1.3  | Current status of the CMS pixel detectors                      | 7         |

|          |     | 1.1.4  | The phase 1 upgrade of the CMS pixel detector                  | 9         |

|          |     | 1.1.5  | The phase 2 upgrade of the CMS pixel detectors                 | 12        |

|          | 1.2 | The R  | D53A demonstrator chip                                         | 16        |

|          |     | 1.2.1  | RD53A chip design and assembly                                 | 17        |

| <b>2</b> | Rac | l-Hard | Bandgap Voltage Reference                                      | <b>23</b> |

|          | 2.1 | Radiat | tion effects on CMOS transistors and integrated circuits       | 24        |

|          |     | 2.1.1  | Radiation-matter interaction                                   | 24        |

|          |     | 2.1.2  | Radiation effects on MOS transistors                           | 26        |

|          |     | 2.1.3  | Layout techniques for the design of radiation-tolerant         |           |

|          |     |        | circuits                                                       | 30        |

|          | 2.2 | Rad H  | Iard Bandgap Voltage Reference                                 | 32        |

|          |     | 2.2.1  | Guidelines and specifications                                  | 33        |

|          | 2.3 | Design | and simulation results                                         | 34        |

|          |     | 2.3.1  | Working principle of bandgap voltage reference                 | 34        |

|          |     | 2.3.2  | Current mode bandgap reference based on MOS bi-                |           |

|          |     |        | ased in weak inversion region                                  | 38        |

|          |     | 2.3.3  | Design of the operational amplifier $\ldots$ $\ldots$ $\ldots$ | 39        |

|          |     | 2.3.4  | Startup circuit                                                | 42        |

|          |     | 2.3.5  | Bandgap voltage reference                                      | 42        |

|          |     |        |                                                                |           |

|    |       | 2.3.6  | Design of the second version of the bandgap voltage reference        | 49  |

|----|-------|--------|----------------------------------------------------------------------|-----|

|    | 2.4   | Chara  | cterization and irradiation results                                  |     |

|    | 2.1   | 2.4.1  | Characterization and irradiation results of the first                | 01  |

|    |       |        | prototype of bandgap voltage reference                               | 51  |

|    |       | 2.4.2  | Characterization and irradiation results for the second              |     |

|    |       |        | prototype of bandgap voltage reference                               | 57  |

| 3  | Low   | -Powe  | r, Low Voltage, Differential I/O link                                | 67  |

|    | 3.1   | Introd | uction                                                               | 68  |

|    | 3.2   | SLVS   | system and specifications                                            | 69  |

|    | 3.3   | Perfor | mance qualification                                                  | 70  |

|    |       | 3.3.1  | Lossy transmission line and intersymbol interference                 |     |

|    |       |        | (ISI)                                                                |     |

|    |       | 3.3.2  | Impendance mismatch and reflection                                   | 75  |

|    |       | 3.3.3  | Noise and timing jitter                                              |     |

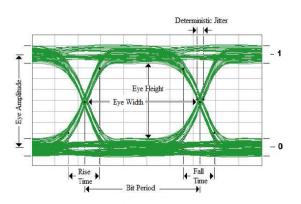

|    |       | 3.3.4  | Eye diagram                                                          |     |

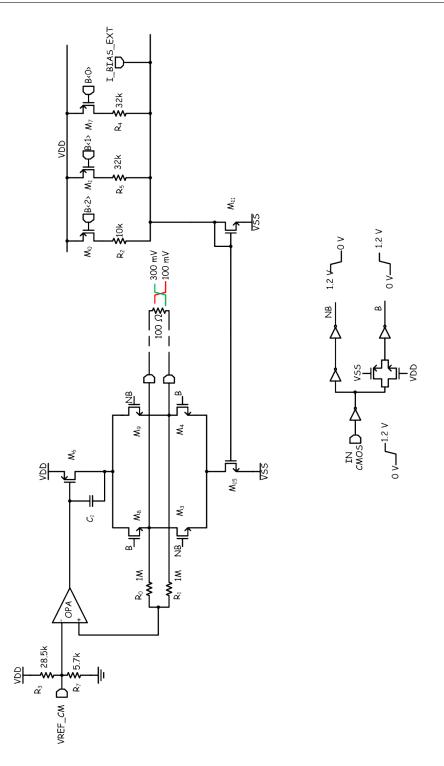

|    | 3.4   | 0      | $\mathbf{n}$ and simulation results of the SLVS transmitter $\ldots$ | 81  |

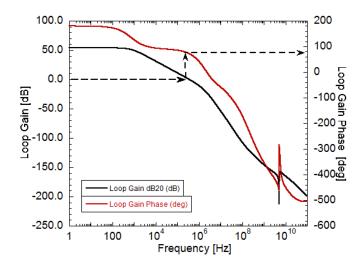

|    |       | 3.4.1  | Operational amplifier and stability of the common                    |     |

|    |       |        | mode feedback                                                        |     |

|    |       | 3.4.2  | Phase splitter                                                       |     |

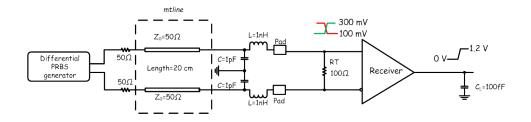

|    |       | 3.4.3  | Test Bench                                                           |     |

|    | ~ ~   | 3.4.4  | Simulation results                                                   |     |

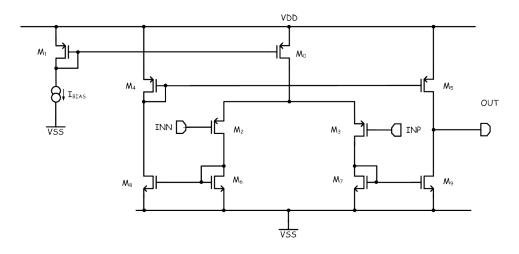

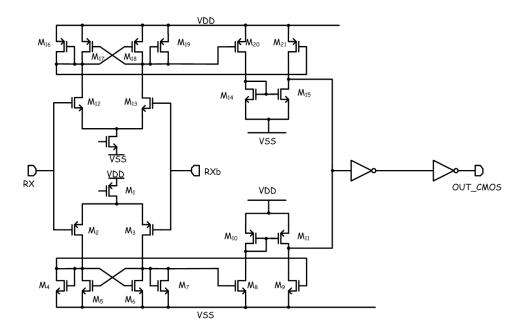

|    | 3.5   | 0      | and simulation results of the SLVS receiver                          |     |

|    |       | 3.5.1  | Small-signal analysis                                                |     |

|    | 0.0   | 3.5.2  | Simulation results                                                   |     |

|    | 3.6   |        | cterization and irradiation results                                  |     |

|    |       | 3.6.1  | Test setup                                                           |     |

|    |       | 3.6.2  | Experimental results                                                 |     |

|    |       | 3.6.3  | Irradiation results                                                  |     |

|    |       | 3.6.4  | Jitter components analysis                                           | 111 |

| Co | onclu | isions |                                                                      | 115 |

| Bi | bliog | graphy |                                                                      | 117 |

### \_\_\_\_\_LIST OF FIGURES

| 1.1  | the CMS detector.                                                  | 4  |

|------|--------------------------------------------------------------------|----|

| 1.2  | LHC timeline                                                       | 5  |

| 1.3  | transverse section of the CMS detector and signatures for          |    |

|      | different particles crossing the volume                            | 6  |

| 1.4  | layout of the PSI46V2 chip employed in the CMS silicon tracker.    | 7  |

| 1.5  | block diagram of the pixel cell of the PSI46V2 chip employed       |    |

|      | in the CMS innermost silicon pixel layer                           | 8  |

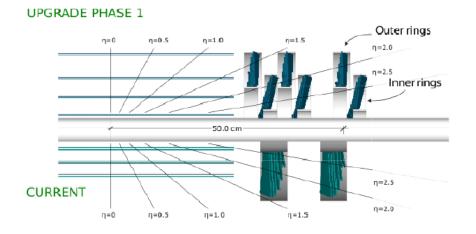

| 1.6  | comparison between the current 3 layers (bottom) and the           |    |

|      | Phase 1 upgrde 4 layers for the CMS silicon tracker                | 10 |

| 1.7  | block diagram of the PSI46DIG ASIC chip.                           | 11 |

| 1.8  | block diagram of the $3^{rd}$ generation of front-end chip for the |    |

|      | innermost layer of the CMS silicon tracker.                        | 14 |

| 1.9  | preliminary floorplan of the RD53A chip                            | 17 |

| 1.10 | example of the new design approch. Four custom analog pix-         |    |

|      | els are surrounded by a digital sea, where the digital standard    |    |

|      | cells are automatically placed and routed by synthesis tool        | 18 |

| 1.11 | schematic of the analog pixel front-end designed at LBNL           | 19 |

| 1.12 | schematic of the analog pixel front-end designed at FNAL           | 20 |

| 1.13 | schematic of the analog pixel front-end designed at Universi-      |    |

|      | ties of Bergamo and Pavia and INFN Pavia.                          | 21 |

| 1.14 | schematic of the analog pixel front-end designed at INFN           |    |

|      | Torino                                                             | 21 |

| 1.15 | analog chip bottom block diagram.                                  | 22 |

| 0.1  |                                                                    |    |

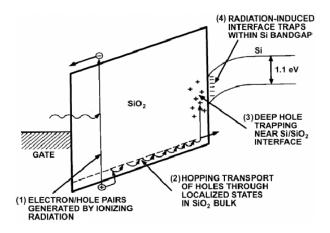

| 2.1  | schematic energy band diagram for MOS structure, indicating        | 00 |

| 0.0  | major physical processes underlying radiation response             | 26 |

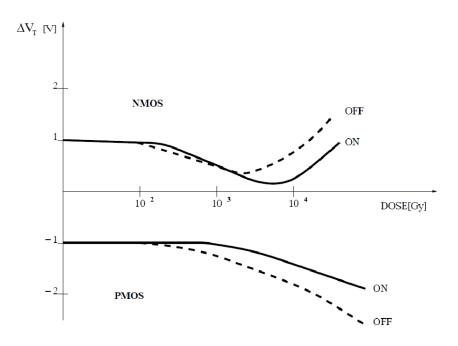

| 2.2  | variation of the threshold voltage as a function of the Total      | ~= |

|      | Ionizing Dose (TID) for PMOS and NMOS devices                      | 27 |

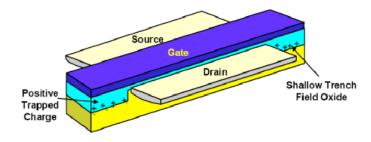

| 2.3  | conceptual drawing (not to scale) showing how positive charge<br>build-up in STI oxides can lead to lateral leakage currents in |    |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

|      | NMOS devices.                                                                                                                   | 28 |

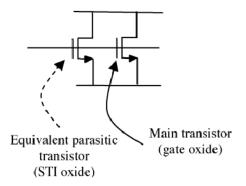

| 2.4  | circuit model for an NMOS exposed to ionizing radiation with                                                                    |    |

|      | the parasitic devices due to charge trapped in the STI                                                                          | 29 |

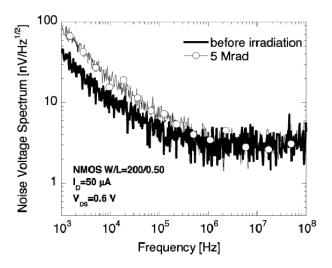

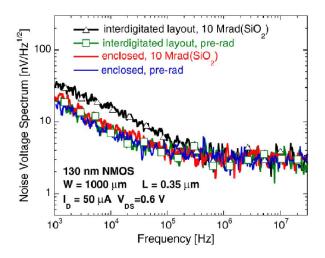

| 2.5  | Noise voltage spectra before irradiation and after exposure to                                                                  |    |

|      | a 5 Mrad total dose of X-rays for an NMOS with $W/L=200/0.5$                                                                    |    |

|      | in the 65 nm process, at 50 $\mu$ A drain current                                                                               | 29 |

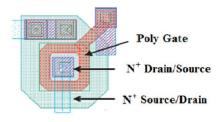

| 2.6  | layout of an enclosed transistor (ELT) for rad-hard design                                                                      | 30 |

| 2.7  | example of an enclosed layout for a multifinger device                                                                          | 31 |

| 2.8  | Noise voltage spectra before irradiation and after exposure to                                                                  |    |

|      | a 10 Mrad total dose for NMOSFETs with enclosed layout                                                                          |    |

|      | and with interdigitated layout, at 50 $\mu$ A                                                                                   | 31 |

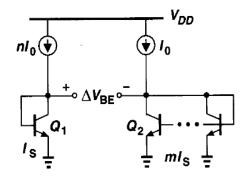

| 2.9  | generation of positive TC                                                                                                       | 35 |

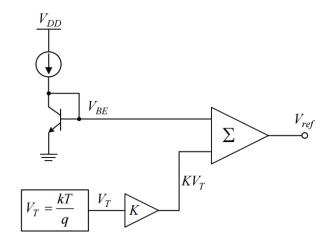

|      | block diagram of the bandgap voltage reference                                                                                  | 36 |

| 2.11 | schematic of the current mode bandgap voltage reference based                                                                   |    |

|      | on bipolar devices.                                                                                                             | 37 |

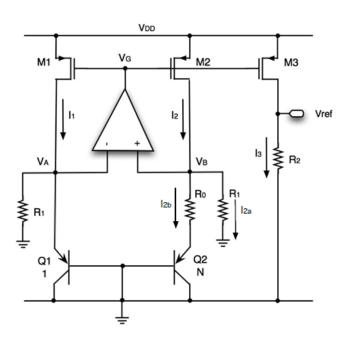

| 2.12 | schematic of the current mode bandgap voltage reference based                                                                   |    |

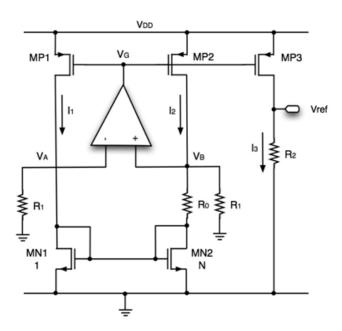

|      | on MOSFETs in sub-threshold region                                                                                              | 40 |

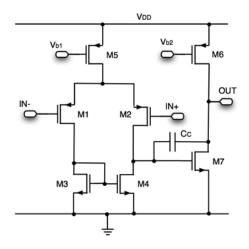

| 2.13 | schematic of the proposed operational amplifier                                                                                 | 41 |

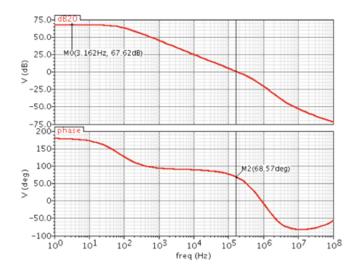

| 2.14 | open-loop frequency response of the operational amplifier at                                                                    |    |

|      | room temperature                                                                                                                | 42 |

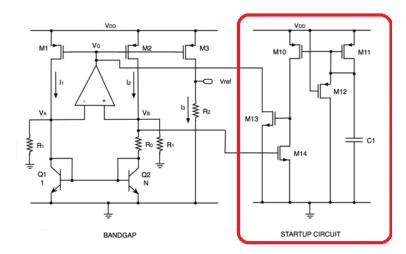

| 2.15 | schematic of the proposed startup circuit                                                                                       | 43 |

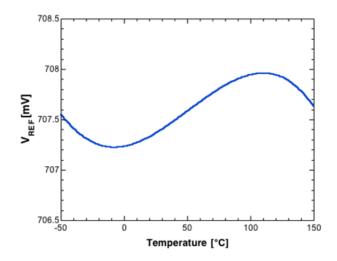

| 2.16 | voltage at the output of the BGR based on bipolar devices                                                                       |    |

|      | simulated in nominal condition                                                                                                  | 44 |

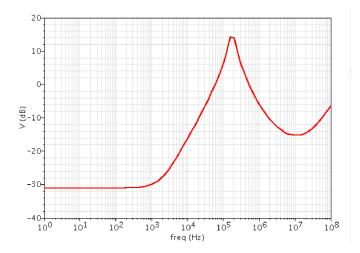

| 2.17 | simulated PSR for the bandgap reference circuit based on                                                                        |    |

|      | bipolar devices                                                                                                                 | 44 |

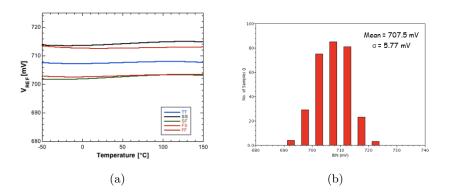

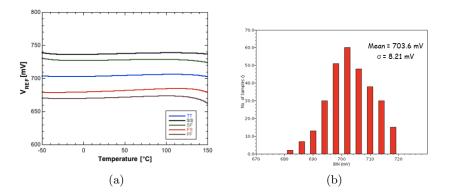

| 2.18 | (a) four corners simulations and (b) Monte Carlo simulation                                                                     |    |

|      | for the bandgap reference circuit based on bipolar devices.                                                                     | 45 |

| 2.19 |                                                                                                                                 |    |

|      | layout simulations of the bandgap reference with bipolars                                                                       |    |

|      | transistors.                                                                                                                    | 46 |

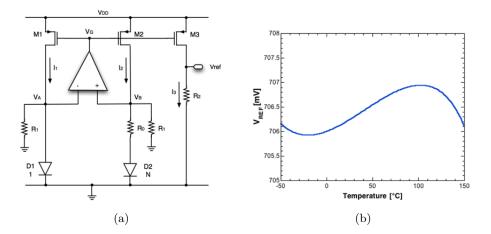

| 2.20 | (a) schematic and (b) output voltage as a function of the                                                                       |    |

|      | temperature in nominal conditions for the bandgap reference                                                                     |    |

|      | circuit based on diode devices.                                                                                                 | 46 |

| 2.21 | (a) output voltage as a function of the temperature as ob-                                                                      |    |

|      | tained from four corners simulations and (b) Monte Carlo                                                                        |    |

|      | simulation results for the bandgap based on diodes                                                                              | 47 |

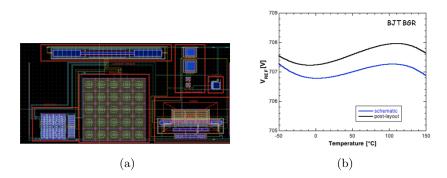

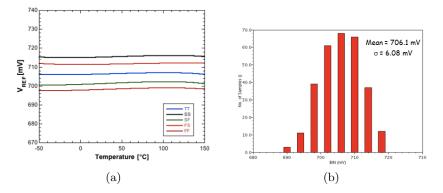

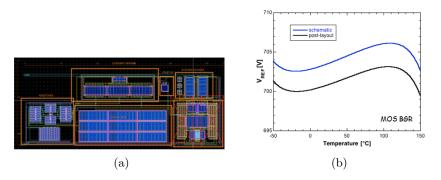

| 2.22 | (a) layout and (b) comparison between pre and post layout                                                                       |    |

|      | simulations for the bandgap with diodes.                                                                                        | 48 |

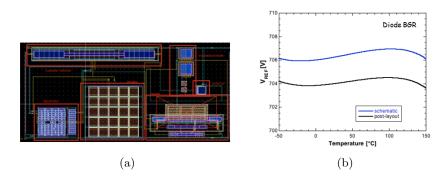

| 2.23 | (a) schematic of the bandgap based on MOS in sub-threshold                                                                      |    |

|      | region and (b) output voltage as a function of the temperature                                                                  |    |

|      | in nominal conditions.                                                                                                          | 48 |

| 2.24  | (a) output voltage for four corners simulations and (b) Monte<br>Carlo simulations for the bandgap output voltage at room |    |

|-------|---------------------------------------------------------------------------------------------------------------------------|----|

|       | temperature.                                                                                                              | 49 |

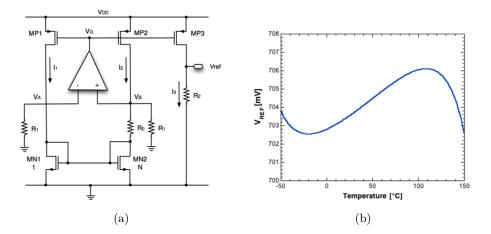

| 2.25  | (a) layout and (b) comparison between pre and post layout                                                                 |    |

|       | simulations for the bandgap based on MOS devices                                                                          | 49 |

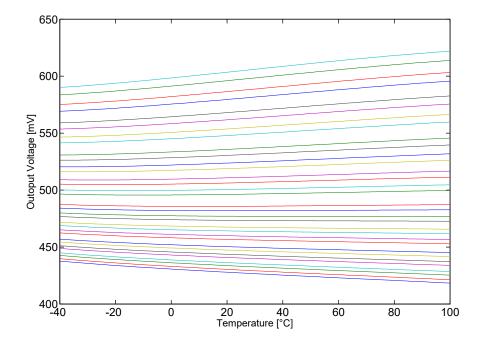

| 2.26  | output voltage vs. temperature for the 32 possible values of                                                              |    |

|       | $R_0$                                                                                                                     | 50 |

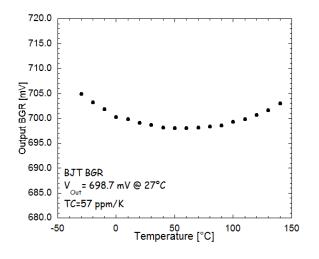

| 2.27  | measurement of the output voltage vs. temperature for the                                                                 |    |

|       | bandgap based on bipolar transistors.                                                                                     | 51 |

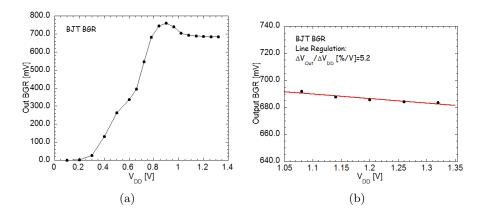

| 2.28  | (a) output voltage of the bandgap vs power supply and (b)                                                                 |    |

|       | line regulation for the bandgap based on bipolar devices                                                                  | 52 |

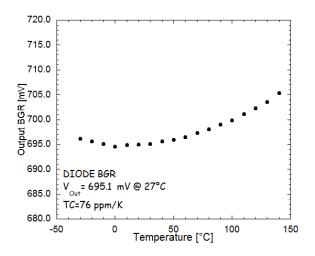

| 2.29  | output voltage vs. temperature for the bandgap based on diode.                                                            | 53 |

| 2.30  | (a) output voltage as a function of the power supply and (b)                                                              |    |

|       | line regulation of the bandgap based on diode devices                                                                     | 53 |

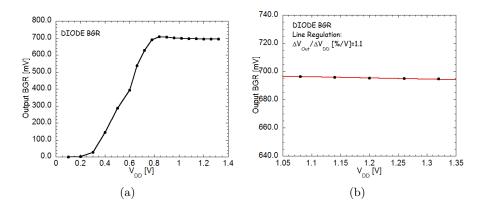

| 2.31  | output voltage vs. temperature for the bandgap based on                                                                   |    |

|       | MOS devices in weak inversion.                                                                                            | 54 |

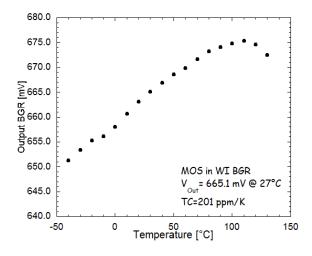

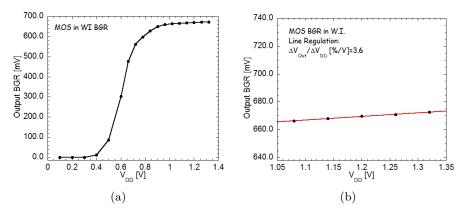

| 2.32  | (a) output voltage vs power supply and (b) line regulation for                                                            |    |

|       | the bandgap based on MOS transistors                                                                                      | 54 |

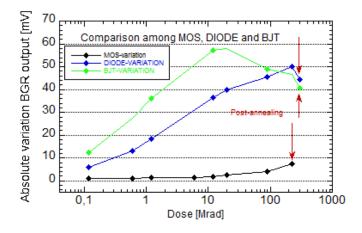

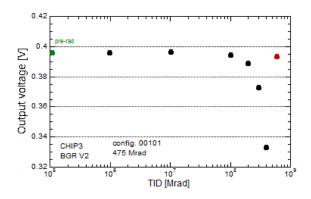

| 2.33  | output voltage vs. TID for the three kinds of BGRs irradiated                                                             |    |

|       | at room temperature and biased as in the real application.                                                                | 56 |

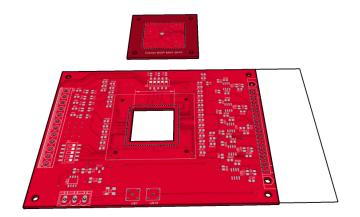

| 2.34  | layout of the PCB test board                                                                                              | 57 |

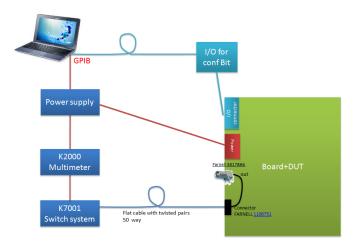

| 2.35  | block diagram of the automated test system.                                                                               | 58 |

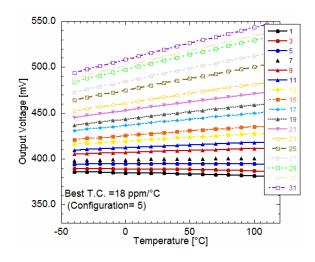

| 2.36  | bandgap output voltage vs. temperature for different config-                                                              |    |

|       | urations of the trimming resistor                                                                                         | 59 |

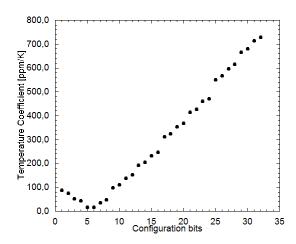

| 2.37  | temperature coefficient vs. configuration bits                                                                            | 60 |

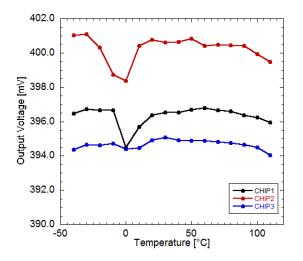

| 2.38  | bandgap output voltage as a function of the temperature for                                                               |    |

|       | three different chips.                                                                                                    | 60 |

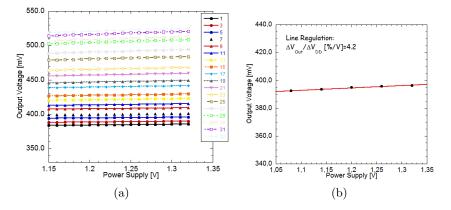

| 2.39  | (a) output voltage vs. power supply and (b) line regulation                                                               |    |

|       | for the second version of the bandgap based on MOS in sub-                                                                |    |

|       | threshold region.                                                                                                         | 61 |

| 2.40  | output voltage as a function of the dose in the sample irradi-                                                            |    |

|       | ated with 10 keV X-rays.                                                                                                  | 62 |

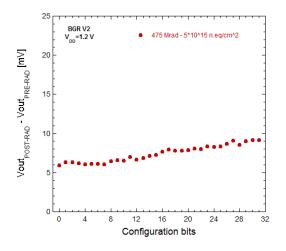

| 2.41  | variation of bandgap output voltage after irradiation with                                                                |    |

|       | 3 MeV protons at the CN accelerator in Legnaro                                                                            | 63 |

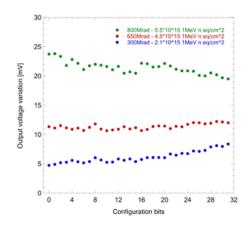

| 2.42  | bandgap output voltage variation as a function of the config-                                                             |    |

|       | uration bits for different fluences and TIDs, from the $10 \text{ MeV}$                                                   |    |

|       | proton source at the TANDEM accelerator in Legnaro                                                                        | 63 |

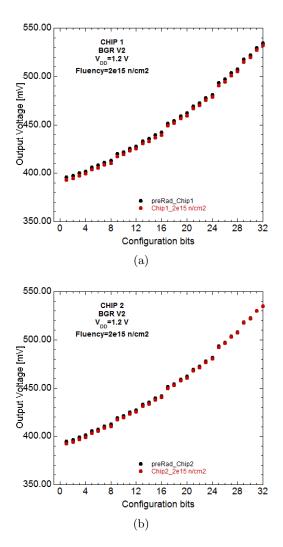

| 2.43  | output voltage as a function of the configuration bits for two                                                            |    |

|       | chips irradiated with a fluence of $2 \cdot 10^{15}$ n.eq/cm <sup>2</sup> at the                                          |    |

|       | neutron source in Ljubljana                                                                                               | 64 |

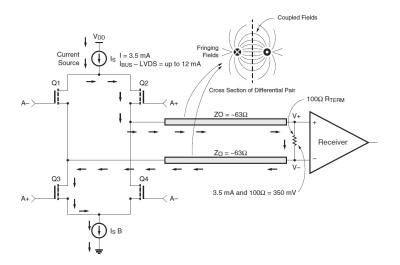

| 3.1   | point-to-point LVDS link.                                                                                                 | 68 |

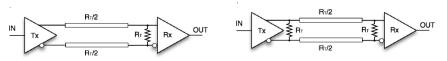

| 3.2   | differential solution for high-speed data link.                                                                           | 69 |

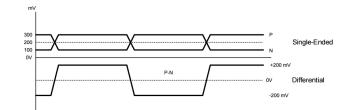

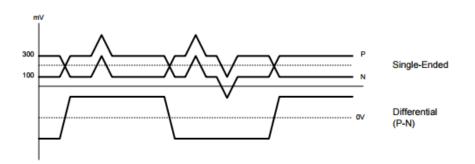

| 3.3   | single ended and differential SLVS waveforms                                                                              | 70 |

| J . J |                                                                                                                           |    |

| 3.4  | common-mode noise rejection                                                    | 70  |

|------|--------------------------------------------------------------------------------|-----|

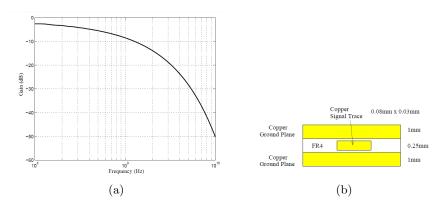

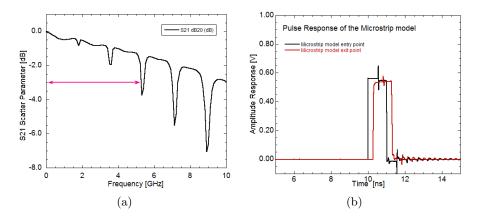

| 3.5  | (a) S21 parameter and (b) cross-sectional view of 50 cm (FR4)<br>PCB stripline | 72  |

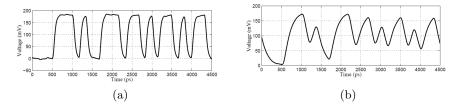

| 3.6  | (a) data transmitted at 6 Gbit/s and (b) received signal at                    | 12  |

| 5.0  | 6 Gbit/s affected by ISI due to a lossy channel                                | 72  |

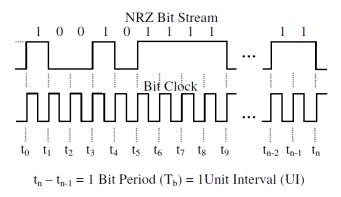

| 3.7  | example of an NRZ random signal                                                | 73  |

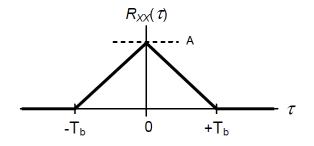

| 3.8  | autocorrelation of a random NRZ stream.                                        | 73  |

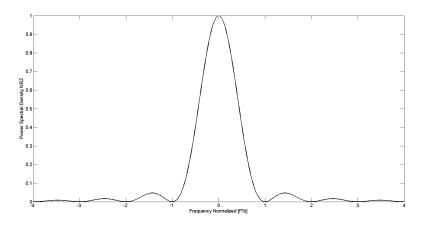

| 3.9  | power spectral density of a random bit stream.                                 | 74  |

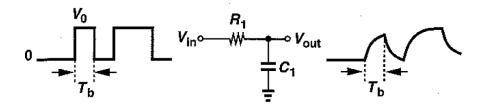

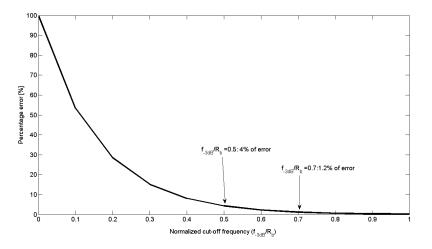

|      | response of a single pole system to a random stream                            | 74  |

|      | error as a function of the fractional bandwidth.                               | 75  |

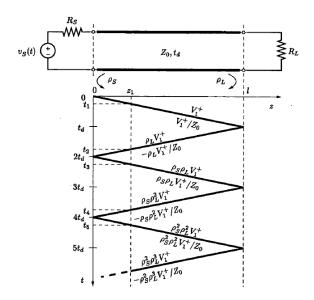

|      | lattice diagram for a lossless transmission line with unmatched                |     |

| -    | terminations                                                                   | 76  |

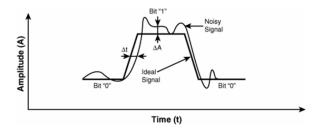

| 3.13 | ideal digital signal and a noisy version of the same signal                    | 77  |

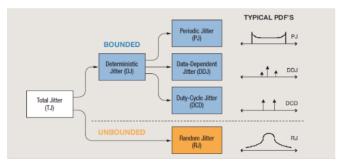

| 3.14 | main components of the jitter: noise, system-phenomena and                     |     |

|      | data-dependent contributions.                                                  | 79  |

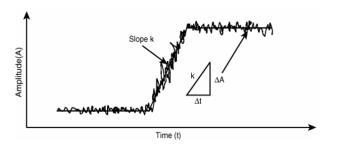

| 3.15 | amplitude noise to timing jitter conversion through the linear                 |     |

|      | model                                                                          | 79  |

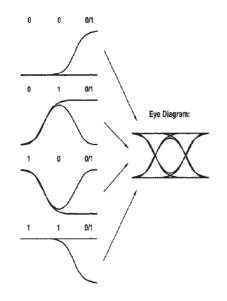

| 3.16 | generation of the eye diagram.                                                 | 80  |

|      | example of eye diagram with the relevant eye parameters. $\ . \ .$             | 81  |

| 3.18 | schematic of the SLVS transmitter                                              | 82  |

| 3.19 | schematic of the symmetrical operational amplifier $\ . \ . \ .$ .             | 83  |

|      | Bode diagram of the common mode loop gain                                      | 84  |

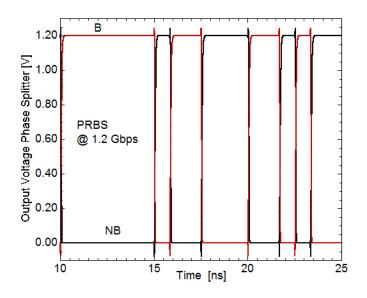

| 3.21 | outputs of the Phase Splitter block, when at the input a PRBS                  |     |

|      | signal at 1.2 Gbit/s is applied.                                               | 85  |

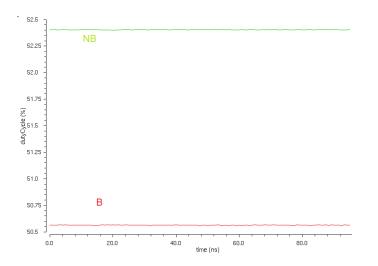

| 3.22 | duty-cycle distortion during a transient simulation. The input                 | ~   |

|      | signal is a clock at 1.2 GHz.                                                  | 85  |

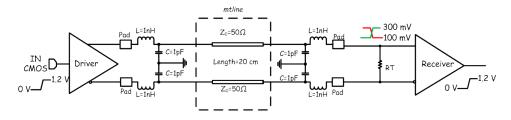

|      | test bench for the transmitter                                                 | 86  |

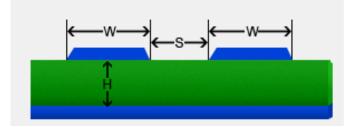

|      | cross section of the microstrip.                                               | 86  |

| 3.25 | (a) S21 insertion loss scatter parameter of the microstrip and                 | 07  |

| 2.96 | (b) impulse response of the microstrip line                                    | 87  |

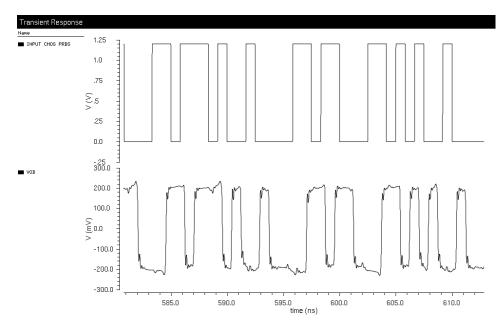

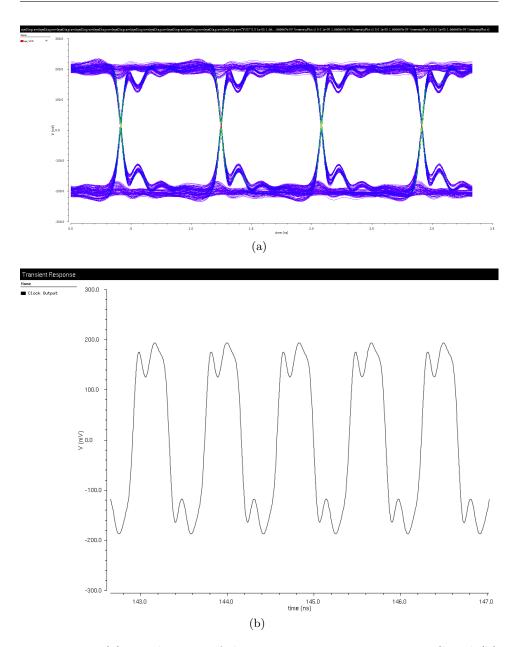

| 3.20 | differential output of the transmitter. Stimulated with a PRBS at 1.2 Gbit/s   | 88  |

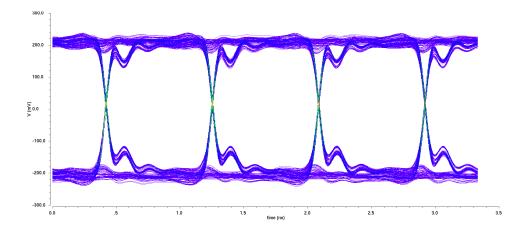

| 3.27 | simulation of the transmitter eye diagram taken at the input                   |     |

|      | termination resistance of the receiver.                                        | 89  |

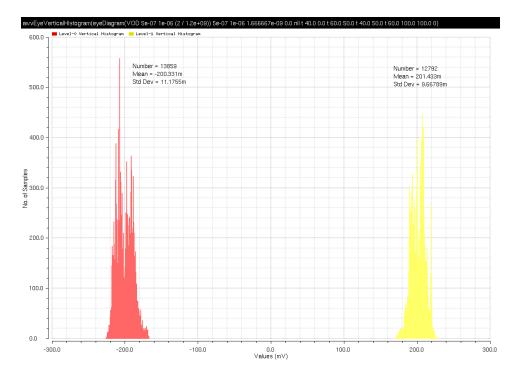

| 3.28 | histogram of the eye diagram levels                                            | 89  |

| 3.29 | (a) eye diagram of the transmitter output at $-20$ °C and (b)                  |     |

|      | transient response applying a clock input signal at $-20$ °C. $% 10^{\circ}$ . | 90  |

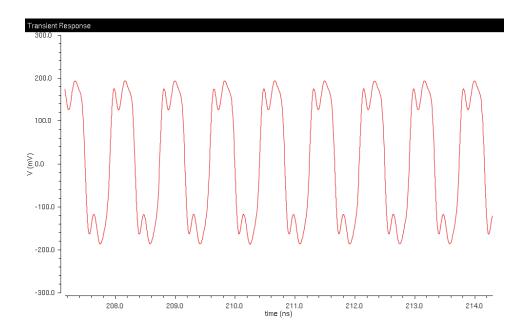

| 3.30 | differential signal at the driver output. Input signal is a clock              |     |

|      | at 1.2 GHz at room temperature and nominal condition. $\ . \ .$                | 91  |

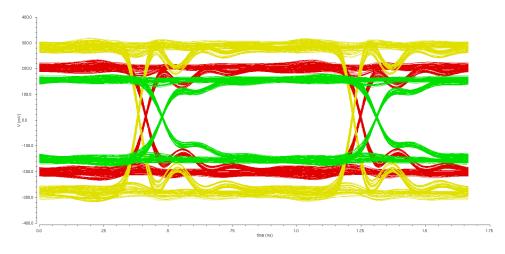

| 3.31 | eye diagram simulated in three different corners: the green                    |     |

|      | diagram obtained in the slow corner, the red one in the typical                | 6.5 |

|      | corner and the yellow one in the fast corner                                   | 92  |

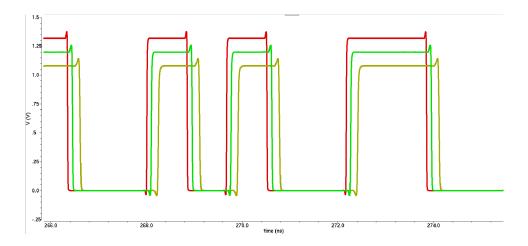

| 3.32 | differential output of the driver, stimulated by a clock signal                                                        |     |

|------|------------------------------------------------------------------------------------------------------------------------|-----|

|      | obtained from PVT simulations. The green time diagram                                                                  |     |

|      | refers to the slow corner, the red diagram to the typical corner                                                       |     |

|      | and the yellow one to the fast corner                                                                                  |     |

|      | layout of the transmitter.                                                                                             |     |

|      | schematic of the receiver.                                                                                             | 94  |

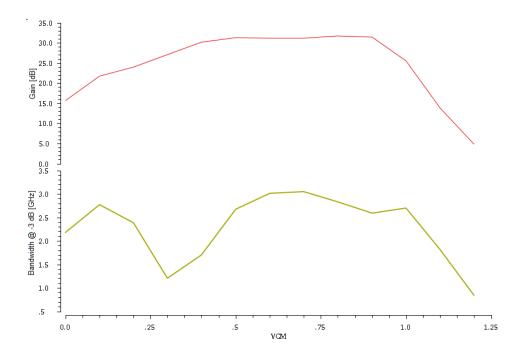

| 3.35 | bandwidth and gain of the receiver as a function of the com-                                                           |     |

|      | mon mode voltage of the input signal                                                                                   |     |

| 3.36 | test bench used to stimulate the SLVS receiver                                                                         | 96  |

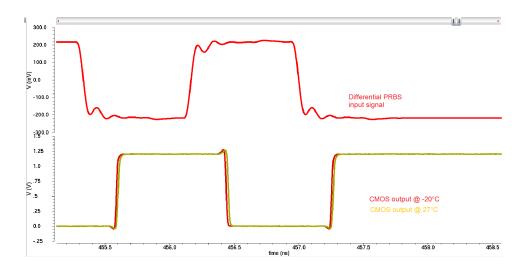

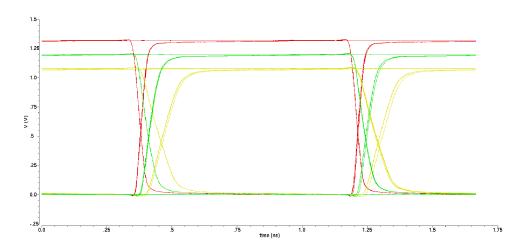

| 3.37 | top plot is the PRBS differential input of the receiver at 1.2 Gbit/s and peak value $V_{ID} = \pm 200$ mV. The bottom |     |

|      | plot is the transient response of the receiver in nominal con-                                                         |     |

|      | ditions for two different temperatures, $-20$ °C (red line) and                                                        |     |

|      | 27 °C (yellow line). $\ldots$                                                                                          | 97  |

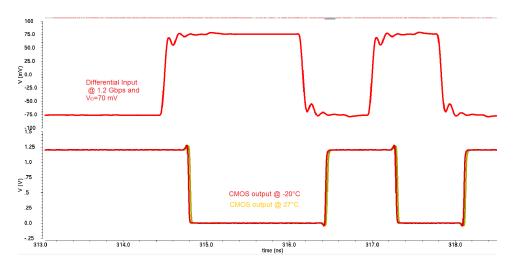

| 3.38 | output CMOS of the receiver in worst case operating condi-                                                             |     |

|      | tions $(V_{ID} = \pm 70 \text{ mV})$ .                                                                                 | 97  |

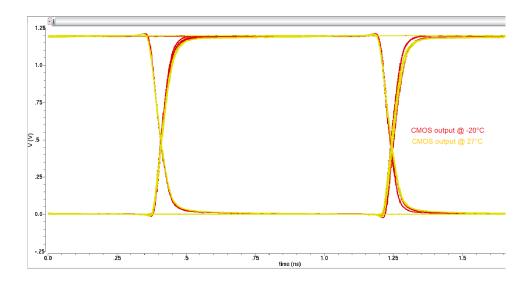

| 3.39 | eye diagram of the output receiver signal. Stimulated by a                                                             |     |

|      | PRBS signal 1.2 Gbit/s and differential input signal $V_{ID}$ =                                                        |     |

|      | $\pm 200 \text{ mV}$ .                                                                                                 | 98  |

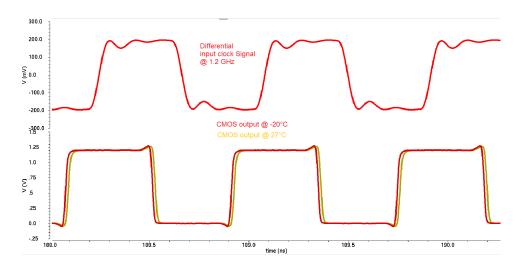

| 3.40 | transient response of the receiver when a 1.2 GHz clock signal                                                         |     |

|      | is applied for two operating temperatures: $-20$ °C (red line)                                                         |     |

|      | and 27 $^{\circ}C$ (yellow line)                                                                                       | 98  |

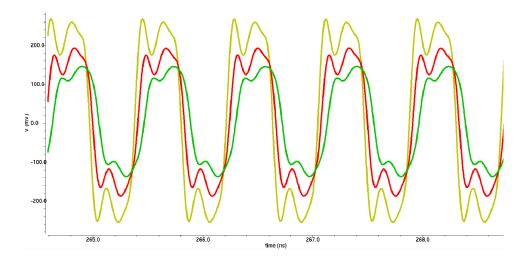

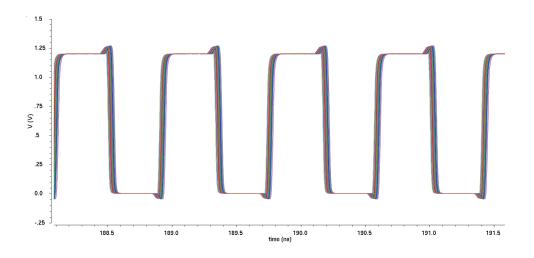

| 3.41 | CMOS output of the receiver from PVT simulations. Red                                                                  |     |

|      | line refers to the fast corner, green line to the typical corner                                                       |     |

|      | and yellow line to the slow corner.                                                                                    | 100 |

| 3.42 | Eye diagram of the receiver output from PVT simulations.                                                               |     |

|      | Red line refers to the fast corner, green line to the typical                                                          |     |

|      | corner and yellow line to the slow corner                                                                              | 101 |

| 3.43 | Monte Carlo simulation results                                                                                         | 101 |

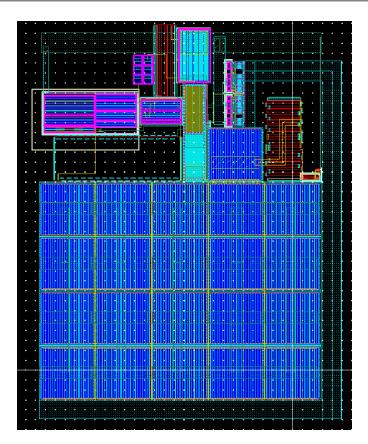

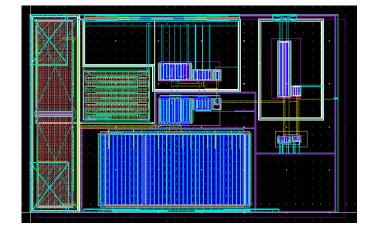

| 3.44 | layout of the SLVS receiver.                                                                                           | 102 |

| 3.45 | layout of the chip with transmitter and receiver (red box)                                                             |     |

|      | submitted in May 2015                                                                                                  |     |

| 3.46 | block diagram of the test bench setup and PCB test board                                                               |     |

|      | with two ASICs, which are directly bonded on the PCB                                                                   | 103 |

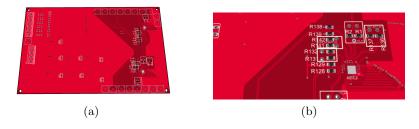

| 3.47 | (a) 3D sketch of the PCB test board and (b) zoom of the top                                                            |     |

|      | layer of the PCB.                                                                                                      | 104 |

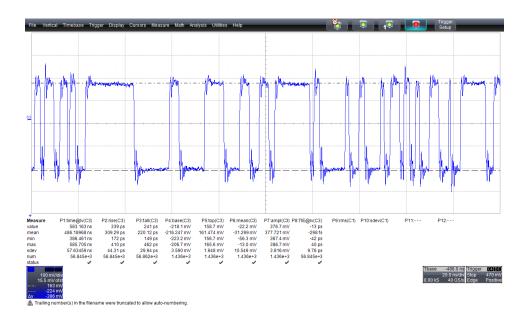

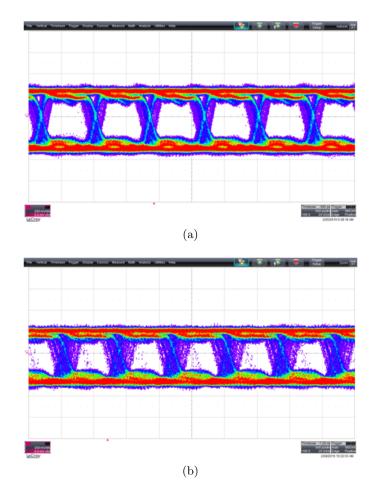

|      | eye diagram at 1.2 Gbit/s of the transmitter signal                                                                    | 104 |

| 3.49 | measurement of the output waveform of the transmitter, with                                                            |     |

|      | the relevant parameters                                                                                                | 105 |

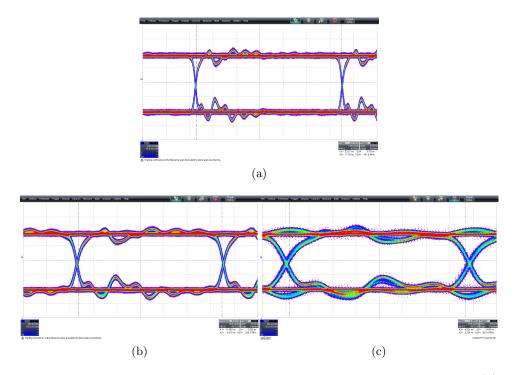

| 3.50 | measurements of the eye diagram of the transmitter at (a)                                                              |     |

|      | 160 Mbit/s, (b) 320 Mbit/s and (c) 640 Mbit/s                                                                          | 106 |

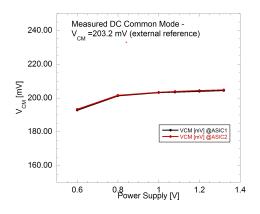

| 3.51 | measured output common mode voltage $(V_{CM})$ as a function                                                           |     |

|      | of the power supply $(V_{DD})$                                                                                         | 107 |

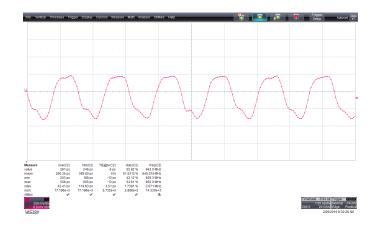

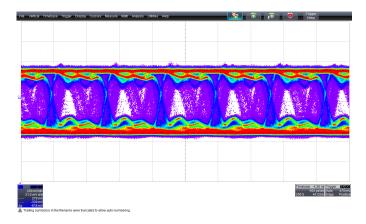

| measurement of the differential output of the transmitter stim-        |                                     |

|------------------------------------------------------------------------|-------------------------------------|

| ulated by a clock signal at 640 MHz                                    | 107                                 |

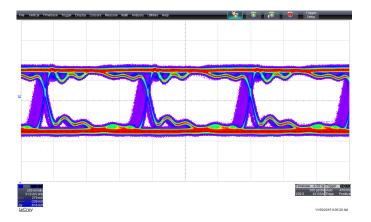

| eye diagram of the receiver, as a response to a differential           |                                     |

| PRBS at 1.2 Gbit/s and differential input of $V_{ID} = 100 \text{ mV}$ |                                     |

| (worst case condition). The measurement has been performed             |                                     |

| at the output of the CML driver                                        | 108                                 |

| eye diagram of the receiver as a response to a differential            |                                     |

| PRBS at 640 Mbit/s and differential input of $V_{ID} = 100$ mV.        |                                     |

| The measurement has been performed at the output of the                |                                     |

| CML driver                                                             | 108                                 |

| eye diagram receiver output, as a response to a PRBS at                |                                     |

| 1.2 Gbit/s and with $V_{ID} = 150$ mV. This is the minimum             |                                     |

| detectable signal at 1.2 Gbit/s                                        | 109                                 |

| measured eye diagram of the receiver in nominal condition at           |                                     |

| 1.2 Gbit/s                                                             | 109                                 |

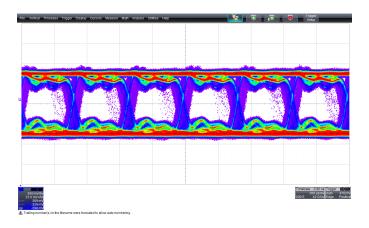

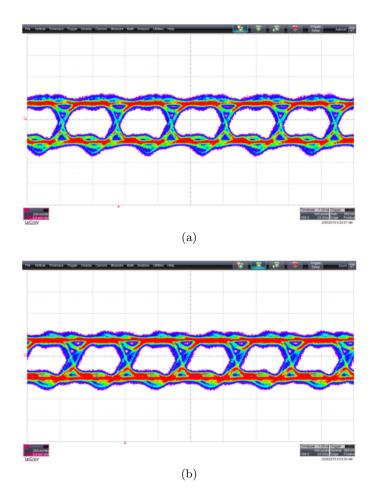

| eye diagram measurements for the transmitter, stimulated by            |                                     |

| a 1.2 Gbit/s PRBS signal (a) before irradiation and (b) after          |                                     |

| irradiation with a TID of 550 Mrad                                     | 110                                 |

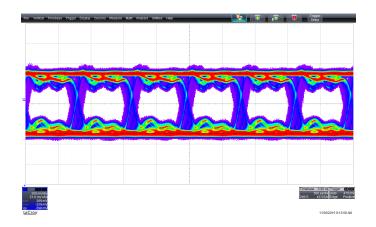

| eye diagram measurements for the receiver, stimulated by a             |                                     |

| 640 Mbit/s PRBS signal (a) before irradiation and (b) after            |                                     |

| irradiation with a TID of 550 Mrad                                     | 111                                 |

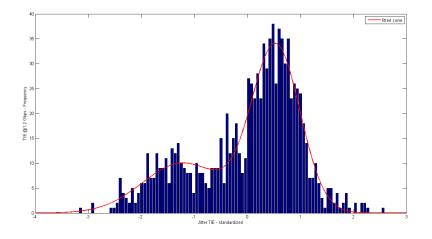

| histogram of the fitted model                                          | 113                                 |

|                                                                        | ulated by a clock signal at 640 MHz |

### LIST OF TABLES

| 1.1  | main specifications of the PSI46V2 chip                             | 9  |

|------|---------------------------------------------------------------------|----|

| 1.2  | comparison between PSI46V2 and PSI46DIG readout chip                |    |

|      | specifications                                                      | 12 |

| 1.3  | specification for the $3^{rd}$ generation of hybrid pixel detectors |    |

|      | for the innermost layer of the CMS silicon tracker.                 | 13 |

| 1.4  | evolution of the main requirements of the pixel detectors           |    |

|      | ASIC for the innermost layer of the CMS silicon tracker             | 14 |

| 1.5  | specification for the RD53A analog front-end.                       | 19 |

| 2.1  | design specifications of the BGR.                                   | 33 |

| 2.2  | main parameters as a function of the temperature                    | 41 |

| 2.3  | output voltage and temperature coefficient of the bandgap           |    |

|      | based on bipolar transistors from four corner simulations.          | 45 |

| 2.4  | simulations results in nominal conditions for the bandgap           |    |

|      | based on diode devices.                                             | 47 |

| 2.5  | simulations results from four corner simulations for the bandgap    |    |

|      | based on diode devices.                                             | 47 |

| 2.6  | four corners simulation results for the bandgap based on MOS        |    |

|      | in weak inversion region                                            | 49 |

| 2.7  | main parameters (before irradiation) for the bandgap refer-         |    |

|      | ence circuit based on diode devices                                 | 52 |

| 2.8  | main parameters (before irradiation) for the bandgap refer-         |    |

|      | ence circuits.                                                      | 55 |

| 2.9  | output voltage and temperature coefficient for the three chips      |    |

|      | tested in the climatic chamber                                      | 60 |

| 2.10 | variation of the bandgap output voltage in a chip exposed to        |    |

|      | 10 keV X-rays                                                       | 61 |

| 2.11 | variation of the bandgap output voltage with 10 MeV protons         |    |

|      | at the TANDEM accelerator (Legnaro)                                 | 62 |

| 2.12 | performance comparison with similar bandgap reference cir- |     |

|------|------------------------------------------------------------|-----|

|      | cuits                                                      | 65  |

| 3.1  | transmitter SLVS JEDEC DC specifications.                  | 71  |

| 3.2  | receiver SLVS JEDEC DC specifications                      | 71  |

| 3.3  | output current configuration of the SLVS transmitter       | 81  |

| 3.4  | microstrip properties                                      | 86  |

| 3.5  | comparison of the driver performance                       | 91  |

| 3.6  | performance of the transmitter in PVT simulations          | 93  |

| 3.7  | comparison of the receiver performance                     | 99  |

| 3.8  | comparison of the receiver performance in PVT simulations  | 99  |

| 3.9  | eye diagram parameters                                     | 106 |

| 3.10 | parameters of the fitted model                             | 112 |

#### UNIVERSITA' DEGLI STUDI DI PAVIA

Dipartimento di Ingegneria Industriale e dell'Informazione

#### High Density Analog Circuits for Semiconductor Pixel Detectors

Francesco DE CANIO

### Abstract

An upgrade of the physics experiments, also called "phase 2 upgrade", is in progress at the LHC (Large Hadron Collider), the particle collider installed at CERN in Geneva, and will become operational in 2022-2023. The experiment upgrade will follow the upgrade of the accelerator itself, which will change its name to HL-LHC (High Luminosity LHC). CERN (Centre Européen pour la Recherche Nucléaire) is leading an international collaboration, called RD53, whose aim is to design a new generation of hybrid pixel readout chips to enable the ATLAS and CMS phase 2 upgrade. The submission of the first demonstrator chip, called RD53A, is foreseen for April 2017. The chip will be designed, using a 65 nm CMOS technology for the first time in the high energy physics (HEP) community, to be compliant with extremely high particle rates and radiation levels. In particular, the readout circuit under development will need to withstand extremely high total ionizing doses, in the order of 1 Grad in 10 years of operation in the experiment. With respect to the pixel detectors currently employed in the LHC experiments, the new chip will feature a significantly finer granularity, with a pixel pitch of 50  $\mu$ m in both X and Y directions.

A number of functional blocks or IP (Intellectual Property) blocks, are required for a complete ASIC system. The IP blocks have to be designed and optimized taking into account the very harsh radiation environment and the resulting effects on individual transistors and more complex circuits. In this work, the development of two IP blocks is presented and discussed. In particular, a rad-hard bandgap voltage reference and a differential IO link have been designed and characterized. They will be included in the RD53A demonstrator chip, in particular, in the monitoring and IO sections.

The rad-hard bandgap reference has been designed in two different versions: the first one has been designed using the same architecture (i.e. a bandgap reference based on a current mode approach) for three circuits. Each circuit exploits a different active device (i.e. bipolar, diode or MOS in sub-threshold region) to generate a temperature dependent voltage reference. The purpose of this first version was to understand which solution is the best in term of radiation hardness. The power supply is 1.2 V and the layout has the same area, 260  $\mu$ m x 120  $\mu$ m, for the three different circuits. In this first prototype, the best choice in terms of temperature insensitivity is provided by the circuit using the bipolar transistor as the voltage reference device. Indeed the temperature coefficient is 76 ppm/K with an output voltage of 700 mV at room temperature. In terms of radiation hardness, instead, the best solution is the one based on the MOSFET transistor in weak inversion region. Indeed, the maximum voltage shift after irradiation with a total dose of 225 Mrad  $(SiO_2)$  is less than 8 mV, to be compared to the 40 mV shift which was detected in the case both of the circuit based on bipolar transistors and of the one based on diodes. A second version of the bandgap has then been submitted and characterized, based on MOS transistors in weak inversion. In this second prototype, new features have been incorporated. In particular, the biasing current has been increased by a factor of about 4, in order to mitigate the TID effect. Also a trimmable resistor has been included in order to minimize mismatch and process variation induced effects. The output voltage at room temperature is close to 400 mV and the temperature coefficient in a range between -40 °C and -110 °C is 18 ppm/K (after trimming). The second prototype has also been irradiated with 10 keV X-rays at CERN, with a total ionizing dose close to 500 Mrad. The maximum shift of the output voltage is 16%.

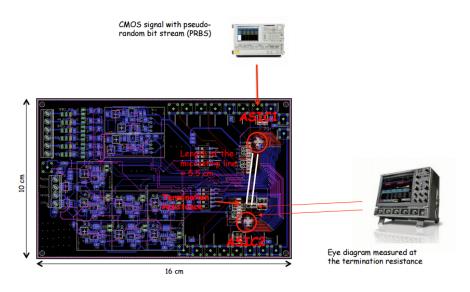

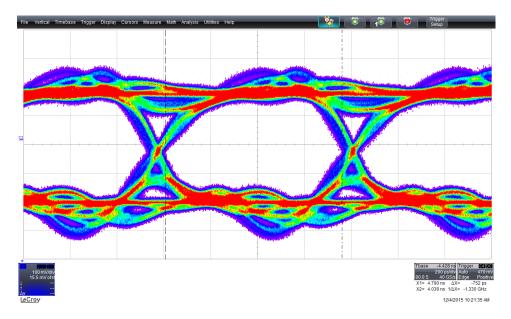

The second IP developed in this work is a differential IO link again use in to severe radiation environment. Differential signaling is an almost mandatory choice to remove or minimize the effects of common mode disturbances in the harsh environment of the HL-LHC experiments. The transmitter and receiver, both biased at 1.2 V, comply with the SLVS JDEC specification: output common mode of the driver is 200 mV and the output differential mode is  $\pm 200$  mV on a 100  $\Omega$  termination resistance. The transmitter has been characterized with a microstrip transmission line on a test PCB with a length close to 5.5 cm. The maximum data rate is 1.2 Gbps with a jitter of 9.8 ps. After exposure to a total ionizing dose of 550 Mrad, the differential IO link did not show any significant performance degradation.

### INTRODUCTION

The research activity carried out in this work is relevant to the design and characterization of high density analog circuits for semiconductor pixel detectors. This activity has been developed in the framework of the CERN RD53 collaboration, whose aim is the design of the next generation of hybrid pixel readout chips for the ATLAS and CMS phase 2 pixel upgrades. The ultimate goal of this three year project is the development of an innovative chip for pixel detectors, using a 65nm CMOS technology for the first time in the High Energy Physics (HEP) community. The detectors are to be used in experiments with extremely high particle rates and radiation levels at the future high luminosity colliders, in particular at the so called high luminosity LHC (Large Hadron Collider), an upgraded version of the present LHC accelerator. In this thesis, the design, simulation, characterization and also irradiation results of two Intellectual Property (IP) blocks are described: a rad hard bandgap voltage reference and an SLVS link composed of a driver and a receiver.

The first chapter begins with a brief introduction of the requirements for the upgrade (phase 2) of HL-LHC. Then it describes the general requirements for the final chip demonstrator of the RD53 collaboration, called RD53A, in which the IPs described in this thesis will be integrated.

The second chapter is devoted to the design of a rad-hard bandgap voltage reference. Two different versions have been developed: the first one has been designed using the same architecture (i.e. a bandgap reference based on a current mode approach) for three circuits. Each circuit exploits a different active device (i.e. bipolar transistors, diode or MOS in sub-threshold region) generating the voltage reference as a function of the temperature. The purpose of this first version was to understand which solution is the best in terms of radiation hardness. The second version, based only on MOS in sub-threshold region, is an improved version of the one designed in the first run. This new version includes the possibility to trim a component in order to mitigate the variations introduced by process, mismatch and radiation effects.

Chapter three discusses the design and characterization of an SLVS driver and receiver system, with a maximum data-rate up to 1.2 Gbit/s. These devices, which comply with the JEDEC specifications, will be used in the RD53 demonstrator chip.

### CHAPTER 1.

### ASIC REQUIREMENTS FOR THE CMS PIXEL DETECTOR AT THE HL-LHC

#### Contents 1.1 The CMS experiment at the LHC ..... 3 1.1.1Large Hadron Collider 3 1.1.2Overview of the CMS Experiment 51.1.3Current status of the CMS pixel detectors . . . . 7 1.1.4The phase 1 upgrade of the CMS pixel detector . . 9 1.1.5The phase 2 upgrade of the CMS pixel detectors . 12The RD53A demonstrator chip ..... 1.216 1.2.1RD53A chip design and assembly . . . . . . . . 17

This chapter is dedicated to a general overview of the CMS experiment at the LHC (Large Hadron Collider), describing the proposed timeline and upgrades for the pixel detectors. The second part is dedicated to the activity carried out by the RD53 collaboration, which aims to the design of the next generation of ASIC pixel detectors for HL-LHC.

### 1.1 The CMS experiment at the LHC

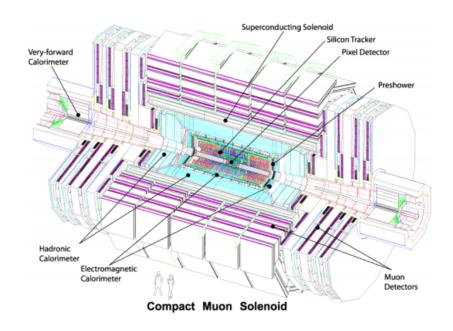

The Compact Muon Solenoid (CMS), shown in figure 1.1, is one of the two general purpose detectors for particle physics experiments installed at the LHC.

#### 1.1.1 Large Hadron Collider

The Large Hadron Collider is the largest particle collider in the world, installed at CERN, where CMS is one of the four main experiments. The

Figure 1.1: the CMS detector.

collider has been designed in order to work with a nominal centre-of-mass energy of 4 TeV and a nominal luminosity of  $10^{34}$  cm<sup>2</sup>s<sup>-1</sup> at 40 MHz bunch crossing rate.

In 2013-2014, the LHC suffered the first planned Long Shut-down, called LS1. The aim of this operation was to improve the machine performance. After the first shut-down, beam energies between 7 TeV and 14 TeV were achieved. A second shut-down (LS2) is foreseen in the 2018-2019 period. In that occasion, the LHC luminosity will be be raised to twice the nominal luminosity. This performance improvement, called *phase 1 upgrade*, will also require an upgrade of the detectors, because the present version of the detector could not be operated in the environment of the upgraded accelerator. A new version of the pixel detectors will be introduced in 2018-2019.

As displayed in figure 1.2, which shows the LHC upgrade timeline, LHC will suffer another long shut-down period, called LS3, from 2023 to 2025, during which the High Luminosity (HL)-LHC will be installed. Its name comes from the huge luminosity of the collider: the beam energy will be around 14 TeV and the luminosity will be increased by a factor of 5 to 7 with respect to the nominal luminosity. During LS3, the CMS experiment (and also the ATLAS experiment) will be upgraded (*phase-2 upgrade*), to

comply with the increased environment hostility. In the ALICE and LHCb experiments, major detector upgrades are instead foreseen during LS2.

Figure 1.2: LHC timeline.

#### 1.1.2 Overview of the CMS Experiment

The goal of the CMS experiment is to investigate a wide range of physics phenomena, including the search for the Higgs boson, extra dimensions, and particles that could make up dark matter. The CMS detector has approximately the shape of a cylinder 21.6 m high and with a base diameter of 16.6 m. The total weight of the detector is about 14000 tonnes. It is located in an underground cavern at Cessy in France, just across the border from Geneva. In July 2012, along with ATLAS, CMS discovered the Higgs boson.

CMS consists of four detectors, which exploit the different properties of particles to catch and measure the energy and momentum. The CMS detector is required to provide a high performance system to detect and measure muons, a high resolution method to detect and measure electrons and photons (an electromagnetic calorimeter), a high quality central tracking system to give accurate momentum measurements, and a "hermetic" hadron calorimeter, designed to entirely surround the collision region and prevent particles from escaping.

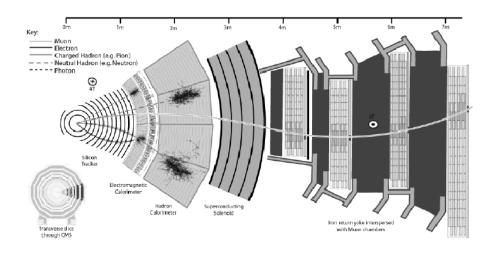

The CMS detector is built around a huge solenoid magnet, in order to take advantage of the properties of the charged particles: the higher a charged particle momentum, the less its path is curved in the magnetic field. Thus, once its path has been tracked, its momentum can be calculated. A strong magnet is therefore needed to enable accurate measurements even of the very high momentum particles, such as muons. The solenoid takes the form of a cylindrical coil of a superconducting cable that generates a magnetic field of 4 T. As anticipated, the CMS detectors are composed by four different layers, as shown in figure 1.3. From the innermost layer, the detectors are: the silicon tracker, the electromagnetic calorimeter (ECAL), the hadron calorimeter (HCAL) and the external muon chamber, which is separated form the previous detector by the superconducting solenoid.

Figure 1.3: transverse section of the CMS detector and signatures for different particles crossing the volume.

The tracker can reconstruct the paths of high-energy muons, electrons and hadrons and it is composed by 13 layers in the central region and 14 layers in the endcaps. The innermost three layers (up to 11 cm radius from the interaction point) consist of  $100 \times 150 \ \mu\text{m}$  pixels. The next four layers (up to 55 cm radius) consist of  $10 \ \text{cm} \times 180 \ \mu\text{m}$  silicon strips, followed by the remaining six layers of 25 cm  $\times 180 \ \mu\text{m}$  strips, out to a radius of 1.1 m. With a total active silicon area of 200 m<sup>2</sup>, the CMS tracker is the largest full-silicon tracking system, with 1440 pixel-modules and 14148 strip modules, corresponding to 66 million pixels and 9.3 milion silicon strips.

The tracking system is followed by the electromagnetic calorimeter (ECAL), which achieves accurate measurements of electron and photon position and energy. The third detector is the hadronic calorimeter (HCAL), which is used for measurement of energy and direction of particle jets and the reconstruction of missing transverse energy contributions[1]. The last detector is the one dedicated to muon detection and is the farthest from the beam interaction point, because muons can penetrate several meters of iron without interaction.

#### 1.1.3 Current status of the CMS pixel detectors

The silicon pixel tracking system in CMS is located very close to the interaction point, implying a very high track density and particle fluence which require radiation hard sensors and electronics. In particular, the innermost layer, which is at about 4 cm from the interaction region, is subjected to a charged particle flux of the order of 100 MHz/cm<sup>2</sup>.

Each pixel sensor cell is bump-bonded to a full-custom ASIC, designed in a 0.25  $\mu$ m CMOS technology using special layout techniques which ensure the required radiation hardness. Therefore, the lifetime of the tracker is limited by the damage in the silicon sensor. The innermost layer of the silicon pixel tracker has been designed in order to survive at least 2 years at the nominal LHC luminosity, while 10 years of lifetime is expected for the third layer.

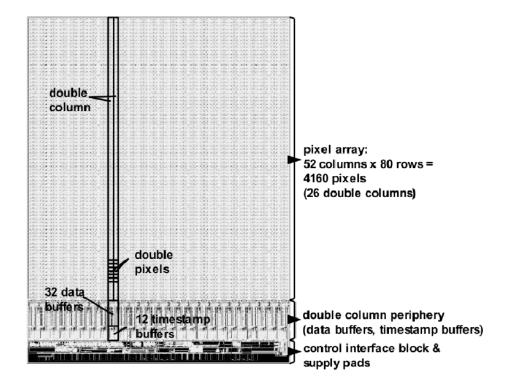

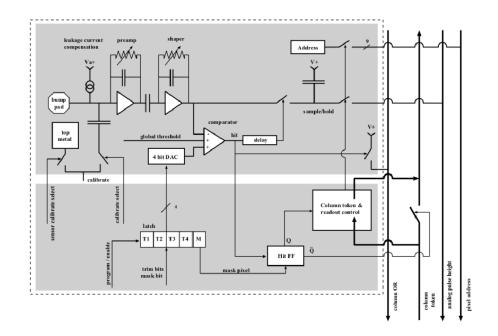

The pixel sensor for the innermost layer in the silicon tracker is composed by 52 columns x 80 rows (4160 cells). Each pixel has an area of 100  $\mu$ m x 150  $\mu$ m. The signal generated when a charged particle passes through the sensor, is processed and read out by a full-custom ASIC bump-bonded to the sensor. The ASIC chip, called PSI46V2, is shown in figure 1.4[2], [3].

Figure 1.4: layout of the PSI46V2 chip employed in the CMS silicon tracker.

The PSI46V2 has an area of 7.8 mm x 9.8 mm, where 7.8 mm x 8 mm are taken by the core pixel matrix and 7.8 mm x 1.8 mm are used for the chip periphery. The core pixel matrix is composed by 52 columns x 80 rows of pixel. Each pixel cell is bump-bonded to a sensor. In the chip, two adjacent columns are assembled in order to share services, such as power distribution, bias and data-buses. Each pixel cell has to provide some storage and buffering capabilities for the signals coming from the sensors. On the other hand, only when a trigger signal is sent to the the detectors, the chip itself has to read the pixel matrix and send the data off-chip. In particular, the PSI46V2 uses a full analog readout. Indeed, charge information is retrieved by only a sample-and-hold circuit, placed in each pixel cell. This piece of information is transferred to the analog buffer in the chip periphery. Thus, the readout is performed in analog form, using a 40 MHz serial analog link.

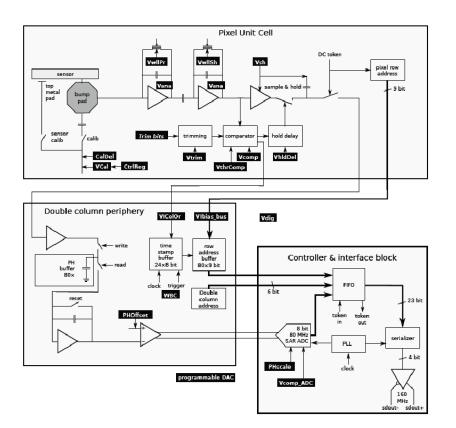

Figure 1.5 shows the block diagram of the pixel cell of the PSI46V2 chip. The charged particle, which passes though the sensor, generates a signal. Such signal is sent to the analog front-end system by means of the bumpbonding interconnection. The front-end system is composed by a charge sensitive amplifier (CSA) and a shaper. The output of the shaper is connected to a continuos-time voltage comparator. The comparator threshold is adjustable with an 4-bit DAC.

Figure 1.5: block diagram of the pixel cell of the PSI46V2 chip employed in the CMS innermost silicon pixel layer.

The power supplies are 1.5 V for the analog section and 2.5 V for the digital section. The overall power consumption is 120 mW, with 29  $\mu$ W for pixel cell. The overall chip configuration uses an  $I^2C$  serial programming interface at 40 MHz. Table 1.1 summarizes the main specifications of the PSI46V2 chip.

| Parameters               | Values                              |  |

|--------------------------|-------------------------------------|--|

| pixel size               | $100~\mu{\rm m} \ge 150~\mu{\rm m}$ |  |

| chip size                | 7.9  mm x  9.8  mm                  |  |

| technology               | CMOS 0.25 $\mu m$                   |  |

| number of pixel          | 52  columns x  80  rows             |  |

| readout                  | full-analog                         |  |

| readout speed            | $40 \mathrm{~MHz}$                  |  |

| nominal charge threshold | $3 {\rm ~ke^-}$                     |  |

| supply voltage           | 1.5 V (A), 2.5 V (D)                |  |

| power consumption        | $\approx 30 \mu W/pixel$            |  |

|                          |                                     |  |

Table 1.1: main specifications of the PSI46V2 chip.

#### 1.1.4 The phase 1 upgrade of the CMS pixel detector

The phase 1 pixel upgrade for CMS is planned to meet the requirements at the expected peak luminosity of 2 times the nominal luminosity. Furthermore, the innermost barrel layer has to be replaced, due to radiation damage in the sensor module.

In particular the main goals of the upgrade are:

- optimization of the layout for four barrel pixel detectors in the inner tracker;

- reduction of the material budget;

- improvement in the efficiency and minimization of radiation induced degradation;

- minimization of data loss in the new pixel readout chip (ROC).

During the upgrade, a new external layer will be introduced, as shown in figure 1.6. Also a new, smaller diameter beam pipe, needed to accommodate the innermost pixel layer, will replace the older one in order to have the detectors as close as possible to the beam. The new barrel layer will increase the number of pixel modules from 768 to 1184 and the number of pixels from 48 to 79 million. Quadruplicating the tracks seeds will greatly reduce the fake rate.

Figure 1.6: comparison between the current 3 layers (bottom) and the *Phase 1 upgrde* 4 layers for the CMS silicon tracker.

The amount of material around the interaction region can exacerbate the multiple scattering issue and degrade the detector accuracy in momentum measurement. In order to solve this problem, in the phase 1 upgrade a different cooling system will be adopted and the electronic boards and connections will be located out of the interaction volume.

Another improvement concerns the pixel readout chip (ROC). Indeed, the new design of the ROC will use a 160 Mbit/s LVDS data link instead of the 40 Mbit/s analog link currently being used. There will be 24 time stamp buffer cells, twice the current number. The data buffer size will increase from 32 to 80, and an additional buffer will be added to the readout chip level. Indeed, the current detectors have a relatively large amount of data loss, due to an insufficient readout speed[5].

In order to efficiently operate at increased data rate, an improved version of the present pixel detector ASIC, called PSI46V2 has been designed. The new chip, called PSI46DIG, has been designed in 0.25  $\mu$ m CMOS technology. Such improvements, including digital readout blocks, have been incorporated, in order to guarantee the high tracking performance required by the *phase 1*.

The block diagram of the new PSI46DIG chip is shown in figure 1.7. The core architecture is mostly unaltered. Indeed, some improvements have been included in the new analog front-end: in particular the charge threshold has been reduced from  $3.5 \text{ ke}^-$  to  $1.5 \text{ ke}^-$ . However, most of the new features are in the chip periphery. An 8 bit SAR ADC has been included in order to perform on-chip charge digitization. Also, an LVDS link operated at

Figure 1.7: block diagram of the PSI46DIG ASIC chip.

160 Mbit/s has been included for the digital readout. The PSI46DIG can be considered the second generation of the hybrid pixel detector for the CMS silicon tracker. Table 1.2 shows a comparison between PSI46V2 and PSI46DIG readout chip specifications[5].

| Parameter                    | PSI46V2                                 | PSI46DIG                            |

|------------------------------|-----------------------------------------|-------------------------------------|

| chip size                    | 7.9  mm x  9.8  mm                      | $7.9 \text{ mm} \ge 10.2 \text{mm}$ |

| pixel size                   | $100~\mu\mathrm{m}\ge150~\mu\mathrm{m}$ | $100~\mu{\rm m}\ge150~\mu{\rm m}$   |

| technology                   | CMOS 0.25 $\mu {\rm m}$                 | CMOS 0.25 $\mu {\rm m}$             |

| charge readout               | analog                                  | digital 8bit                        |

| redout speed                 | $40 \mathrm{~MHz}$                      | 160  Mbit/s (LVDS)                  |

| double-column readout speed  | $20 \mathrm{~MHz}$                      | 20  MHz  or  40  MHz                |

| PLL for clock moltiplication | no                                      | yes                                 |

| threshold                    | $3.5 \ \mathrm{ke^-}$                   | $1.5 \text{ ke}^-$                  |

Table 1.2: comparison between PSI46V2 and PSI46DIG readout chip specifications.

#### 1.1.5 The phase 2 upgrade of the CMS pixel detectors

As already mentioned, during the third long shutdown (LS3) of LHC (2023-2025), the collider will be upgraded to the High Luminosity LHC stage with a luminosity up to 5-7 times the nominal luminosity and an energy of 14 TeV. At this luminosity, the foreseen particle hit rate will rise to about 500 MHz/cm<sup>2</sup> (almost 10 times the present hit rate) and the foreseen total ionizing dose (TID) will be close to 1 Grad in 10 years of lifetime, while the particle fluence is expected to be about  $2 \cdot 10^{16}$  (1MeV)n.eq/cm<sup>2</sup>. Such a harsh radiation environment requires the installation of a new generation of hybrid pixel detectors in the CMS innermost layer of the silicon tracker, able to withstand these radiation doses. Moreover, the pixel detectors for the CMS phase 2 upgrade (as this new experiment stage is called), will have to cope with the very high data rate and guarantee an increased track resolution.

The pixel size is a critical aspect and the chosen one represents a tradeoff between physics performance requirements, sensor technology, scale of integration of the front-end chip process and interconnection technology. At the moment, in the technical proposal, the pixel size of the sensor for the inner tracker is 50  $\mu$ m x 50  $\mu$ m or 25  $\mu$ m x 100  $\mu$ m in order to guarantee the required resolution. In each pixel cell for the pixel detector ASIC, an analog front-end chain is integrated in order to perform the signal amplification and hit discrimination with a minimum detectable charge close to 1 ke<sup>-</sup>. Another challenge for the third generation of the pixel detectors, besides resolution, is the hit rates per unit area, that is close to 2 GHz/cm<sup>2</sup>. To summarize the main goals of the new pixel detector ASIC are:

• higher radiation hardness for the innermost layer, indeed the working period in very harsh radiation environment is supposed to be  $\sim 10$  years with up to  $\sim 1$  Grad total dose;

- increased granularity, with pixels 50 μm x 50 μm in area and a pixel matrix of 1024 rows x 256 columns;

- improved rate capability of the ROCs, with a bandwidth increased from 40 Mbit/s ( $1^{st}$  generation) to 3 Gbit/s ( $3^{rd}$  generation);

- lower power consumption, with a power budget around 0.4  $\frac{W}{cm^2}$  and an estimated front-end chip area of 4 cm<sup>2</sup>.

General ASIC specifications for the  $3^{rd}$  generation of hybrid pixel detectors are shown in table 1.3, while table 1.4 shows the evaluation of the requirements evolution for the pixel detectors.

Table 1.3: specification for the  $3^{rd}$  generation of hybrid pixel detectors for the innermost layer of the CMS silicon tracker.

| Parameters              | Specifications                                                                              |  |  |

|-------------------------|---------------------------------------------------------------------------------------------|--|--|

| number of barrel layers | 4                                                                                           |  |  |

| charged particle flux   | $500 \text{ MHz/cm}^2$                                                                      |  |  |

| total radiation damage  | 1 Grad in 10 years                                                                          |  |  |

| pixel size              | 50 $\mu \mathrm{m} \ge 50 \ \mu \mathrm{m}$ or 25 $\mu \mathrm{m} \ge 100 \ \mu \mathrm{m}$ |  |  |

| chip size               | $\sim 4 \ { m cm}^2$                                                                        |  |  |

| hit-rate                | $1-2 \text{ GHz/cm}^2$                                                                      |  |  |

| hit-time resolution     | < 25  ns                                                                                    |  |  |

| signal threshold        | $1 - 1.8 \ {\rm ke^-}$                                                                      |  |  |

| charge resolution       | 4-8 bits                                                                                    |  |  |

| power budget            | $< 0.4 \ {\rm W/cm^2}$                                                                      |  |  |

| hit memory per chip     | 16 Mbit                                                                                     |  |  |

65 nm CMOS technology has been chosen as the technology for the design of the new pixel detector for the phase 2 upgrade. The choice of the 65 nm CMOS technology is mainly dictated by the good radiation tolerance of the process, also validated through experimental measurements. This technology will bring some further advantages. As compared to the 250 nm technology used for the previous generations of front-end chips, it can offer larger speed and low power consumption. It is true that the 65 nm CMOS technology is used for the first time in HEP experiments. Nevertheless, it is a mature technology, used in many commercial applications and it guarantees long-term availability. The latter characteristic is very important, because will have to be available for the time the phase 2 upgrade becomes operational (2022-23) and for several year after that.

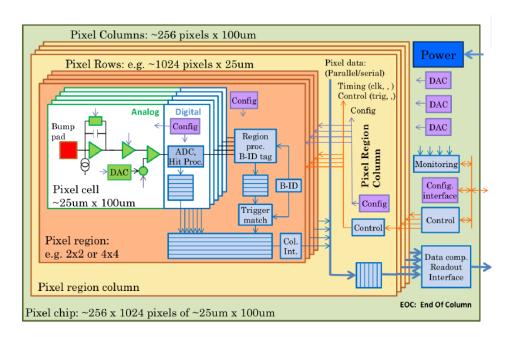

Figure 1.8 shows the block diagram of the hierarchical organization of the front-end chip for the innermost layer of the CMS silicon tracker. A small signal must be detected and amplified in each pixel by a low noise

| Parameter or<br>FEATURE | CMS $1^{st}$ generation<br>LHC Phase 0 | CMS $2^{nd}$ generation<br>LHC Phase 1 | $\begin{array}{c} \text{CMS } 3^{rd} \text{ generation} \\ \text{LHC Phase } 2 \end{array}$ |

|-------------------------|----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------|

| pixel size              | $100~\mu{\rm m} \ge 150~\mu{\rm m}$    | $100~\mu{\rm m} \ge 150~\mu{\rm m}$    | $50~\mu{\rm m} \ge 50~\mu{\rm m}$                                                           |

| technology              | $CMOS \ 250 \ nm$                      | CMOS $250 \text{ nm}$                  | CMOS 65 nm                                                                                  |

| power supply            | 1.5 V(A), 2.5 V (D)                    | 1.5 V(A), 2.5 V (D)                    | 1.2 V(A), 1.0 V(D)                                                                          |

| Max Particle Flux       | $\sim 50 \ \mathrm{MHz/cm^2}$          | $\sim 200 \ {\rm MHz/cm}^2$            | $\sim 500 \text{ MHz/cm}^2$                                                                 |

| Max Pixel Flux          | $0.2 \text{ GHz/cm}^2$                 | $\sim 0.6 \ {\rm GHz/cm^2}$            | $\sim 2 \text{ GHz/cm}^2$                                                                   |

| Rad. Hardness           | 0.15 Grad                              | 0.35 Grad                              | 1 Grad                                                                                      |

| Signal Threshold        | $2500-3000e^-$                         | $1500-2000e^-$                         | $\sim 1000~{\rm e^-}$                                                                       |

| ASIC side               | $\sim 1 \text{ cm}^2$                  | $\sim 4 \text{ cm}^2$                  | $\sim 4 \text{ cm}^2$                                                                       |

| Hit memory per chip     | $\sim 0.1~{\rm Mb}$                    | 1 Mb                                   | $\sim 16 {\rm ~Mb}$                                                                         |

| Chip output bandwidth   | $\sim 40 \text{ Mb/s}$                 | $\sim 320 \text{ Mb/s}$                | $\sim 3 { m ~Gb/s}$                                                                         |

| Power Budget            | $\sim 0.3 \; { m W/cm^2}$              | $\sim 0.3 \; { m W/cm^2}$              | $< 0.4 \mathrm{~W/cm^2}$                                                                    |

Table 1.4: evolution of the main requirements of the pixel detectors ASIC for the innermost layer of the CMS silicon tracker.

Figure 1.8: block diagram of the  $3^{rd}$  generation of front-end chip for the innermost layer of the CMS silicon tracker.

charge sensitive amplifier and, eventually, digitized for further processing. The large number of pixels (100k - 1M) implies that the analog circuit design has to address some critical aspects for physical layout area and for very low power consumption. To overcome these limitations, a design approach based on subdividing the chip array in regions of 4x4 pixel cells will be explored in order to share digital resources.

The chip will include also a number of so called IP (intellectual property) blocks, typically located in the chip periphery. The IP blocks will have to be designed and optimized for the specific pixel application, in such a way to deal with the expected levels of radiation. A non-exhaustive list of these IP blocks follows:

- current and voltage references, they must provide a stable reference independent of variations in supply voltage, temperature, fabrication process parameters and radiation;

- compact low speed (static) Digital to Analog Converters (DAC) are required for generating adjustable analog biases;

- analog to digital converters (ADC) are required for monitoring some parameters (e.g. temperature, supply voltage, etc);

- temperature measurement circuits;

- adjustable (and self-calibrating) timing generators are required to align the sampling point of the pixel detector to the bunch collisions and be capable of making timing sweeps of calibration pulses across the sampling clock period;

- phase locked loops (PLL) are required for clock recovery from encoded input and for high speed serial readout;

- high speed, low power output drivers will be required to drive the local data link to the location of the final high speed serializer and driver for the optical link;

- command decoder and clock recovery to process incoming serial input;

- SEU hard static memory cells; they do not have to be logic library elements, but can be designed as an analog block in order to achieve the maximum possible tolerance for storage of configuration values;

- voltage regulators and DC-DC converters;

- programmable processors, for example a DSP (digital signal processor) or AM (associative memory block), these could be used for many things, not necessarily for processing hit data, for example self testing or of the chip functions could be implemented;

- analog test and calibration circuits, for example to obtain a chip-bychip calibration of the charge injection absolute scale.

In this thesis, the design and characterization of two IP blocks will be discussed. In particular, the description of a rad-hard bandgap voltage reference will be described in chapter 2 and the description of a differential IO link system, in particular an SLVS transmitter and an SLVS receiver, will be described in chapter 3. In the following section, a general overview of the first demonstrator for the CMS pixel front-end chip is provided. The aim of this chip is to demonstrate the feasibility of the third generation of pixel front-end ASICs using for the first time the 65 nm CMOS technology in the High Energy Physics community despite the very harsh radiation environment, the very high resolution requirements and the necessity to comply with very large particle rates.

#### 1.2 The RD53A demonstrator chip

RD53 is an international collaboration, whose final goal is the design of the next generation of pixel readout chips to enable the ATLAS and CMS Phase 2 pixel upgrades. The collaboration started in 2013 and includes research groups from: Bonn, CPPM, LBNL, LPNHE Paris, NIKHEF, New Mexico, UC Santa Cruz, INFN Bari, INFN Pavia, Fermilab, INFN Padova, INFN Perugia, INFN Pisa, PSI, RAL, Torino, CERN and RAL. The duration of the project is estimated in three years (2013-2016) and will lead to a final chip demonstrator, called RD53A.

The requirements for pixel detector ASIC for CMS and ATLAS, while not identical, are quite similar. So, RD53 will design a first demonstrator CHIP (RD53A) with common requirements and features for the two experiments[7], [8]. However, a cross-experiment collaboration does not imply that ATLAS and CMS will adopt the same ASIC for their phase 2 upgrades.

The engineering run of RD53A is foreseen for April 2017. The aim is to demonstrate, in a 65 nm CMOS technology, stable low threshold operation and compatibility with high hit and trigger rate, as required for HL-LHC upgrades of ATLAS and CMS, in a large format IC. RD53A is not intended to be a final production IC for use in the experiments. It will contain design variations for testing purposes, making the pixel matrix non-uniform.

The RD53A IC will have an area of 20x11.8 mm<sup>2</sup> and will consist of a matrix will composed by 400 rows and 192 columns. Each pixel will have an area of 50x50  $\mu$ m<sup>2</sup>[9]. The main features of the chip are summarized in the following list:

- tolerance to TIDs larger than 500 Mrad;

- high hit rate: 2 GHz/cm<sup>2</sup>;

- dead time loss: < 1%;

- trigger rate: 1 MHz;

- low threshold:  $1000 e^-$ ;

- serial powering

#### 1.2.1 RD53A chip design and assembly

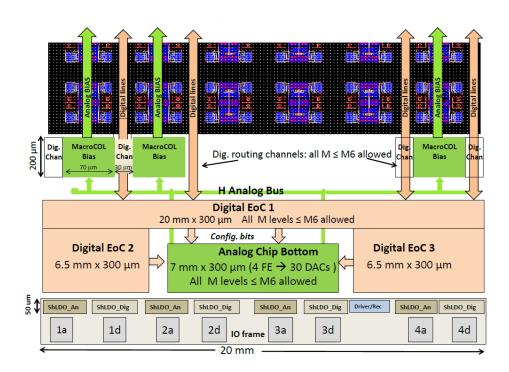

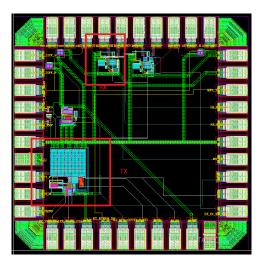

Figure 1.9: preliminary floorplan of the RD53A chip

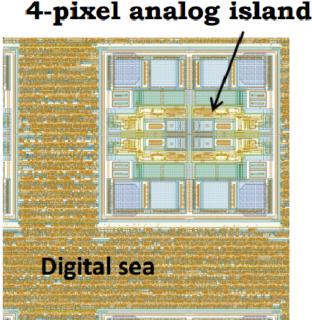

The preliminary floorplan of the RD53A chip is shown in the figure 1.9. The top side shows the pixel matrix, in which each pixel is an analog island surrounded by a digital sea. Such design methodology is a new approach used in the HEP community, which enables the use of place and route automatic tools for VLSI chips. An analog island including the analog sections of four pixels is shown in figure 1.10.

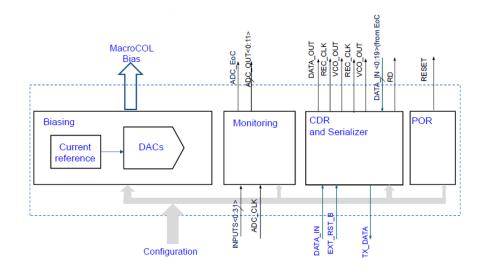

Each pixel region is composed by a 4x4 analog pixel cell to share the digital function (i.e. buffering and time-stamp generation). For each two columns of pixels, there is a column base block (MacroCOL Bias) at the end of the column. Such block provides the biasing and voltage reference and the calibration levels for the pixels in the column. The current references are generated in the analog chip bottom (ACB) block through a voltage bandgap reference. The current reference is used by a current DAC, providing the

Figure 1.10: example of the new design approch. Four custom analog pixels are surrounded by a digital sea, where the digital standard cells are automatically placed and routed by synthesis tool.

biasing reference to the Macro COL Bias. The purpose of the DAC is to compensate for mismatch variations among pixel columns.

The digital EoC (End of Column) manages the readout of the pixel matrix and sends the data off-chip by means of an SLVS transmitter. There will be also an SLVS receiver for ASIC programming (i.e. threshold level, calibration level, current reference, etc...). The transmitter and receiver will be presented and discussed in chapter 3.

At the bottom of the floorplan, the I/O frame is shown. This frame includes the shunt-LDO (Low Drop-Out) and the wire bond pads. Shunt-LDOs are used to address the inefficiency issue due to power distribution in such large systems, as the CMS detectors. Phase 2 upgrade will consists of millions of channels grouped in modules. The modules are powered by cables with a length up to 100 m, introducing significant power losses. A serial powering approach has been proposed to overcome this problem. In a serial powering configuration, modules are placed in series and powered by a constant current source. Shunt regulators are used at module level to generate the supply voltage of the current supply and the LDO is used to regulate the output voltage[10]. In the RD53A chip, 5 shunt-LDOs are foreseen in order to power four front-end topologies and the analog chip bottom (ACB) block.

The pixel matrix includes four topologies of analog front-end, each with a bump bond pad at the channel input for interconnection with the sensor. The analog channel has to comply with the following requirements: a typical input of 10 ke<sup>-</sup>, a minimum detectable charge of 0.1 MIP (minimum ionizing particle), i.e. 1000 e<sup>-</sup>, and an input dynamic range as large as 30 ke<sup>-</sup> (3 MIPs) and a hit time response shorter than 25 ns. The main requirements for the analog front-end are summarized in the table 1.5.

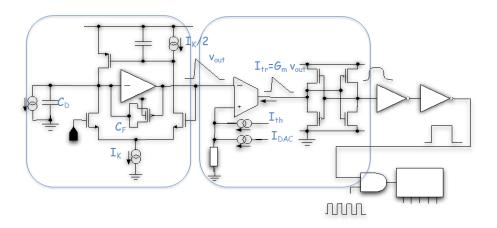

The pixel matrix will include four different analog front-end, designed by four different institutes: the Lawrence Berkeley National Laboratory (LBNL), the Fermi National Accelerator Laboratory (FNAL), the Universities of Bergamo and Pavia and INFN Pavia and, finally, INFN Torino. The schematic diagram of each analog front-end are shown in figure 1.11, 1.12, 1.13 and 1.14. More details about the realization and measurement results of the analog front-ends can be found in the literature [12], [13], [14].

| Parameters                | Specifications       |  |

|---------------------------|----------------------|--|

| Input polarity            | Negative             |  |

| Pixel capacitance         | < 100  fF            |  |

| Pixel leakage current     | $<10~\mathrm{nA}$    |  |

| Minimum detectable charge | $1 \text{ ke}^-$     |  |

| Threshold                 | $600 e^{-}$          |  |

| Equivalent Noise Charge   | $< 130 {\rm ~e^{-}}$ |  |

| hit time response         | < 25  ns             |  |

Table 1.5: specification for the RD53A analog front-end.

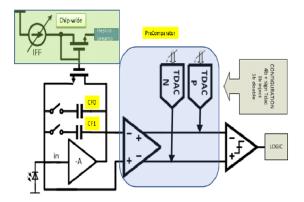

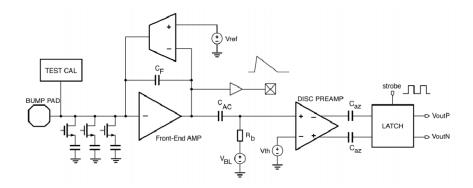

Figure 1.11: schematic of the analog pixel front-end designed at LBNL.

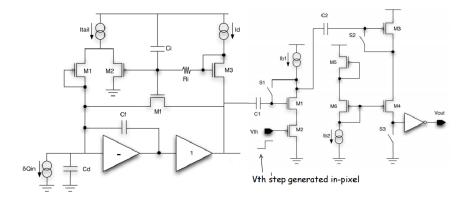

Figure 1.12: schematic of the analog pixel front-end designed at FNAL.