## Università degli Studi di Pavia

Facoltà di Ingegneria Dipartimento di Ingegneria Industriale e dell'Informazione

DOCTORAL THESIS IN MICROELECTRONICS XXXI CICLO

# Design of Wideband Architectures for Modern Communication Standards

Supervisor: Chiar.mo Prof. Rinaldo CASTELLO Coordinator: Chiar.mo Prof. Guido TORELLI

Author: Arianna Coccia

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy.

${\it October}~2018$

## **Declaration of Authorship**

I, Arianna COCCIA, declare that this thesis titled, 'Design of Wideband Architectures for Modern Communication Standards' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

"Do or Do Not. There is No Try"

Maestro Yoda

#### UNIVERSITÀ DEGLI STUDI DI PAVIA

## Abstract

Facoltà di Ingegneria Dipartimento di Ingegneria Industriale e dell'Informazione

Doctor of Philosophy

#### Design of Wideband Architectures for Modern Communication Standards

by Arianna Coccia

Modern communication standards demand wideband solutions, with increasing channel bandwidths. At the same time, massive MIMO is quickly approaching, asking for low-cost and low-power architectures. This thesis is focused on the design of RF blocks, suitable for state-of-the-art applications. The work is divided in two parts. In the first one an innovative transmitter architecture based on a current-mode passive mixer topology with a closed-loop RF amplifier is presented. The second part deals with the analysis and design of a broadband, inductorless noise-cancelling low-noise transconductance amplifier. Measurement (TX) and simulation (TX and LNTA) results are reported, to validate the proposed designs.

## Contents

| Declaration of Authorship | Ι    |

|---------------------------|------|

| Abstract                  | III  |

| Contents                  | IV   |

| List of Figures           | VI   |

| List of Tables            | VIII |

| Abbreviations             | IX   |

|                           |      |

| Introduction              | XII  |

#### I A Wideband SAW-Less Transmitter Operating in Closed-Loop with Embedded RF Filtering 1

| 1        | $\mathbf{An}$ | introd   | uction to 5G                                                                                    | <b>2</b> |

|----------|---------------|----------|-------------------------------------------------------------------------------------------------|----------|

|          | 1.1           | Gener    | al considerations                                                                               | 2        |

|          | 1.2           | Towar    | ds 5G $\ldots$ | 3        |

|          | 1.3           | Moder    | rn standard communication platforms                                                             | 5        |

| <b>2</b> | Stat          | te-of-tl | he-art transmitters                                                                             | 8        |

|          |               | 2.0.1    | Power-mixer $[1]$                                                                               | 8        |

|          |               | 2.0.2    | Direct-digital [2]                                                                              | 8        |

|          |               | 2.0.3    | Voltage-mode passive mixers [3–5]                                                               |          |

|          |               | 2.0.4    | Current-mode passive mixers [6]                                                                 | 11       |

| 3        | Circ          | cuit de  | escription                                                                                      | 12       |

|          | 3.1           | Propo    | sed TX architecture                                                                             | 12       |

|          |               | 3.1.1    | N-path filters                                                                                  | 12       |

|          |               | 3.1.2    | Closed-loop TX                                                                                  | 16       |

|          | 3.2           |          | gain analysis                                                                                   |          |

|          |               | 3.2.1    | Linearity and stability considerations                                                          | 17       |

|          |               | 3.2.2    | Effect of parasitic capacitance on N-path filter                                                | 19       |

|          |               |          |                                                                                                 |          |

|   | 3.3 | 3.2.3 Rebalancing auxiliary mixer |    |

|---|-----|-----------------------------------|----|

| 4 | Pro | totype and measurements           | 26 |

|   | 4.1 | Systems considerations            | 26 |

|   |     | 4.1.1 Out-of-band noise           | 26 |

|   |     | 4.1.2 Linearity                   | 27 |

|   |     | 4.1.2.1 ACLR                      | 27 |

|   |     | 4.1.2.2 CIM3                      | 29 |

|   | 4.2 | Measurement results               | 29 |

| 5 | Con | nclusion                          | 34 |

## II A TVWS LNTA with Balanced Output Employing a Low-Noise Current Multiplier

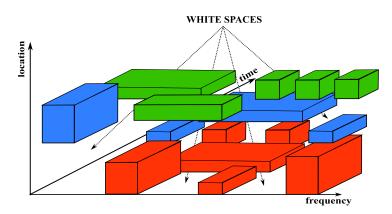

| 6 | Sys  | tem considerations                             | 36 |

|---|------|------------------------------------------------|----|

|   | 6.1  | TV-White Space environment                     | 36 |

|   | 6.2  | Architecture analysis                          | 37 |

| 7 | Cire | cuit description                               | 41 |

|   | 7.1  | Review of noise-canceling Low-Noise Amplifiers | 41 |

|   | 7.2  | Proposed noise-canceling LNTA                  | 42 |

|   | 7.3  | LNTA IIP2 analysis and optimization            | 45 |

|   | 7.4  | Baseband noise analysis                        | 48 |

| 8 | Sim  | ulation results                                | 51 |

| 9 | Cor  | nclusion                                       | 55 |

|   |      |                                                |    |

|   |      |                                                |    |

| A | TX output spectrum measurements | 56 |

|---|---------------------------------|----|

|   |                                 |    |

|   |                                 |    |

| Bibliography |

|--------------|

|--------------|

35

## List of Figures

| 1.1  | DataFly Wheel effect                                                                                | 3  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 1.2  | 5G targets                                                                                          | 4  |

| 1.3  | Skyworks vision of the 5G ecosystem                                                                 | 5  |

| 1.4  | Typical SAW-less scenario                                                                           | 6  |

| 2.1  | Class A/B power mixer TX                                                                            | 9  |

| 2.2  | All digital RF transmitter                                                                          | 9  |

| 2.3  | QDAC based transmitter                                                                              | 10 |

| 2.4  | RQDAC based transmitter                                                                             | 10 |

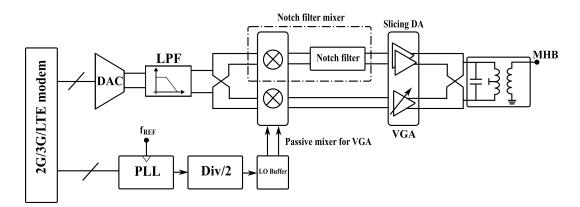

| 2.5  | Transmitter with notch filter mixer                                                                 | 10 |

| 2.6  | N-path SC gain loop TX                                                                              | 11 |

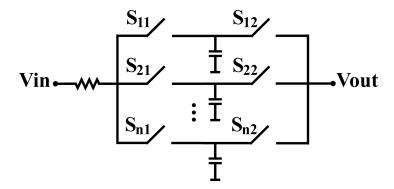

| 3.1  | N-path filter: basic idea                                                                           | 12 |

| 3.2  | N-path filter: RC low pass                                                                          | 13 |

| 3.3  | N-path filter: only capacitors                                                                      | 13 |

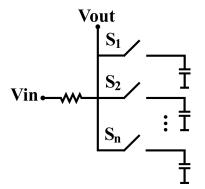

| 3.4  | N-path filter: one switches set                                                                     | 13 |

| 3.5  | N-path filter: time domain analysis                                                                 | 14 |

| 3.6  | DC value charging one capacitor                                                                     | 14 |

| 3.7  | DC values stored on the capacitors                                                                  | 14 |

| 3.8  | N-path filter: staircase approximation of the input signal                                          | 15 |

| 3.9  | Architecture of the proposed transmitter                                                            | 16 |

| 3.10 | Driver amplifier IM3 suppression due to closed-loop operation                                       | 16 |

| 3.11 | Loop gain w/o and with the rebalancing auxiliary mixer optimization $\ldots$                        | 18 |

| 3.12 | Loop phase w/o and with the rebalancing auxiliary mixer optimization                                | 18 |

| 3.13 | The effect of parasitic capacitance on the N-path filter                                            | 20 |

| 3.14 | N-path filter with rebalacing auxiliary mixer                                                       | 22 |

| 3.15 | RF OpAmp first and second stage                                                                     | 23 |

| 3.16 | Bias circuit of the RF OpAmp first stage                                                            | 24 |

| 3.17 | RF OpAmp third stage                                                                                | 24 |

| 4.1  | Out-of-band noise measurement setup                                                                 | 27 |

| 4.2  | Adjacent channel emission spectrum $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 28 |

| 4.3  | CIM3 generation                                                                                     | 28 |

| 4.4  | Chip prototype                                                                                      | 30 |

| 4.5  | Up-conversion gain                                                                                  | 30 |

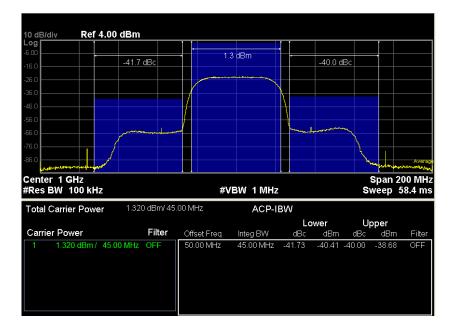

| 4.6  | ACLR with modulated output spectrum                                                                 | 31 |

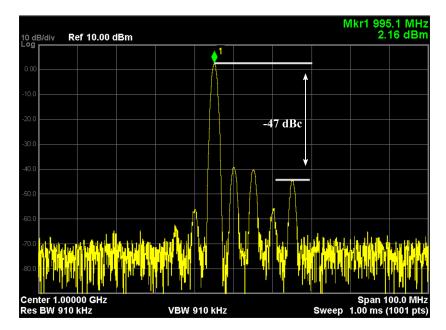

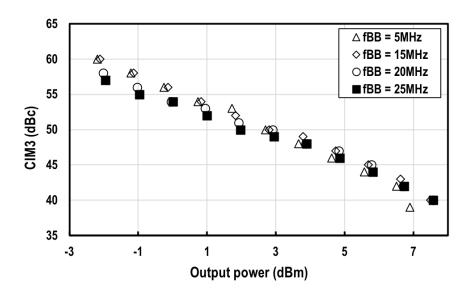

| 4.7  | CIM3 at 3.9 dBm output power spectrum                                                               | 32 |

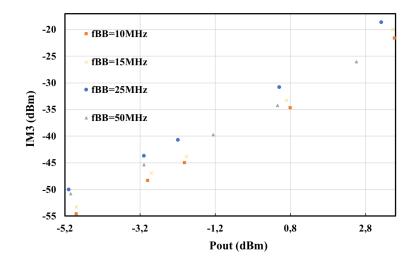

| 4.8  | CIM3 for different single tone output power and BB frequency $\ . \ . \ .$ .                        | 32 |

| 6.1 | Spectrum holes                                                                                               |

|-----|--------------------------------------------------------------------------------------------------------------|

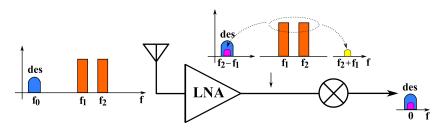

| 6.2 | Second order distortion in wideband receiver                                                                 |

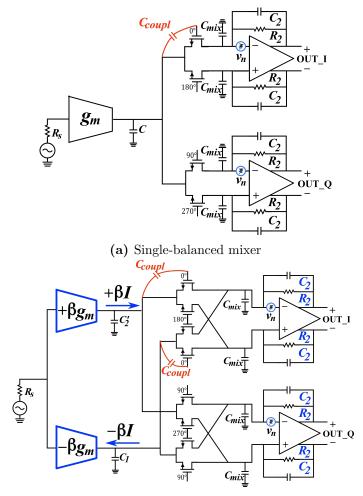

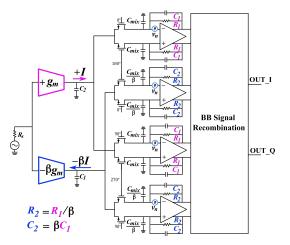

| 6.3 | Receiver architectures                                                                                       |

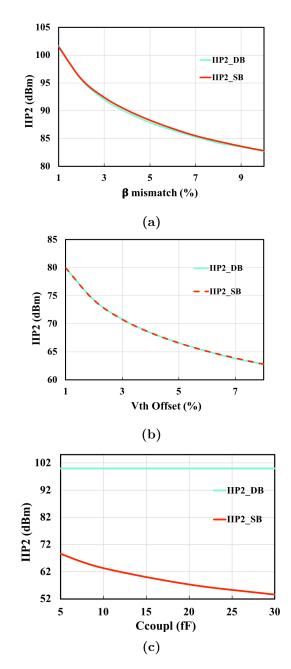

| 6.4 | Simulated RX IIP2 with SB and DB mixers: a) $\beta$ mismatch; b) $V_{\text{th}}$ mismatch; c) RF-LO coupling |

| 7.1 | Proposed CG-CS noise-cancelling LNTA                                                                         |

| 7.2 | Noise models                                                                                                 |

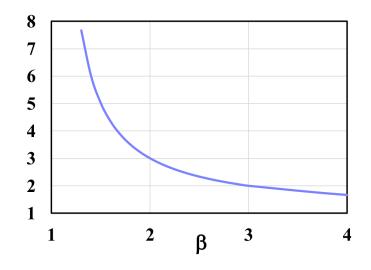

| 7.3 | MBCM noise reduction factor                                                                                  |

| 7.4 | LNTA IM2 generation and propagation                                                                          |

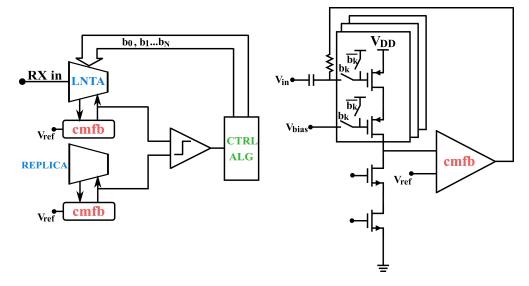

| 7.5 | LNTA IIP2 automatic control loop                                                                             |

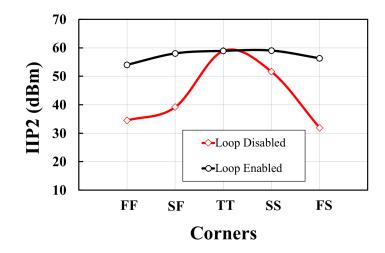

| 7.6 | LNTA IIP2 with and without optimization                                                                      |

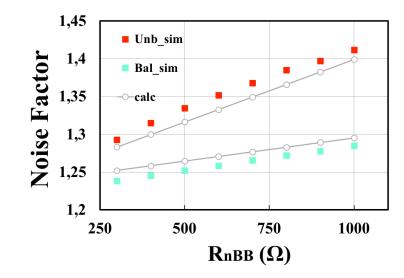

| 7.7 | Receiver base-band Noise Factor                                                                              |

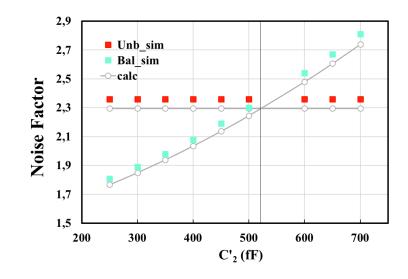

| 7.8 | BB Noise Factor vs $C'_2$                                                                                    |

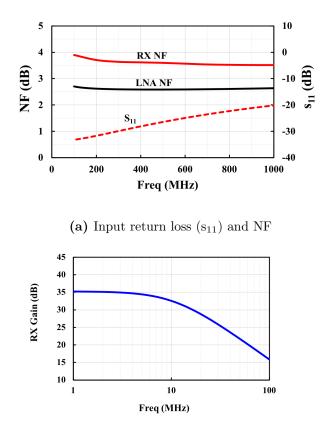

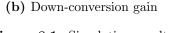

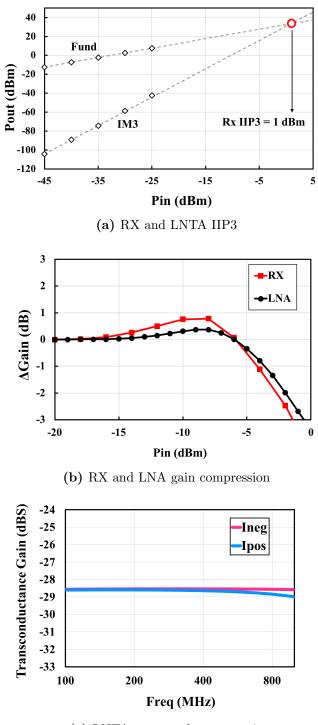

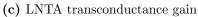

| 8.1 | Simulation results                                                                                           |

| 8.2 | Simulation results                                                                                           |

| A.1 | Two-tones test: output IM3 values                                                                            |

| A.2 | ACLR measured with a 16 QAM signal                                                                           |

| A.3 | ACLR measured with a 64 QAM signal                                                                           |

## List of Tables

| 4.1 | Table of comparison | <br>33 |

|-----|---------------------|--------|

| 8.1 | Table of comparison | <br>51 |

## Abbreviations

| AC                     | Alternating Current                                                                                                                                                                                                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACLR                   | ${f A}$ djacent Channel Leakage Ratio                                                                                                                                                                                                          |

| BB                     | Base Band                                                                                                                                                                                                                                      |

| BOM                    | Bill Of Material                                                                                                                                                                                                                               |

| BP                     | Band Pass                                                                                                                                                                                                                                      |

| $\mathbf{BS}$          | Band Stop                                                                                                                                                                                                                                      |

| $\mathbf{C}\mathbf{A}$ | Carrier Aggregation                                                                                                                                                                                                                            |

| $\mathbf{CG}$          | Common Gate                                                                                                                                                                                                                                    |

| CIM3                   | Counter Intermodulation Product $3$                                                                                                                                                                                                            |

| $\mathbf{C}\mathbf{M}$ | Common Mode                                                                                                                                                                                                                                    |

| CMFB                   | ${\bf C}{\rm ommon}\ {\bf M}{\rm ode}\ {\bf F}{\rm eed}\ {\bf B}{\rm ack}$                                                                                                                                                                     |

| $\mathbf{CS}$          | Common Source                                                                                                                                                                                                                                  |

| DB                     | Double Balanced                                                                                                                                                                                                                                |

| DC                     | Direct Current                                                                                                                                                                                                                                 |

| $\mathbf{eMBB}$        | $\mathbf{e}\mathbf{n}\mathbf{h}\mathbf{a}\mathbf{n}\mathbf{c}\mathbf{e}\mathbf{d}\ \mathbf{M}\mathbf{o}\mathbf{b}\mathbf{i}\mathbf{l}\mathbf{e}\ \mathbf{B}\mathbf{r}\mathbf{o}\mathbf{a}\mathbf{d}\ \mathbf{B}\mathbf{a}\mathbf{n}\mathbf{d}$ |

| $\mathbf{FDD}$         | Frequency <b>D</b> ivision <b>D</b> uplexing                                                                                                                                                                                                   |

| HP                     | $\mathbf{H} \mathrm{igh} \; \mathbf{P} \mathrm{ass}$                                                                                                                                                                                           |

| IM2                    | Inter Modulation 2                                                                                                                                                                                                                             |

| IM3                    | Inter Modulation 3                                                                                                                                                                                                                             |

| IIP2                   | Input Intercept Point 2                                                                                                                                                                                                                        |

| IIP3                   | Input Intercept Point 3                                                                                                                                                                                                                        |

| ΙΟ                     | Input Output                                                                                                                                                                                                                                   |

| IoT                    | Internet of Things                                                                                                                                                                                                                             |

| LNA                    | $\mathbf{Low} \ \mathbf{N} oise \ \mathbf{A} mplifier$                                                                                                                                                                                         |

| LNTA                   | $\mathbf{Low} \ \mathbf{Noise} \ \mathbf{Transconductance} \ \mathbf{Amplifier}$                                                                                                                                                               |

| LO                     | Local Oscillator                                                                                                                                                                                                                               |

| $\mathbf{LP}$                       | Low Pass                                                                                                                        |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| LTE                                 | Long Therm Evolution                                                                                                            |  |  |

| LTI                                 | Linear Time Invariant                                                                                                           |  |  |

| MBCM                                | $\mathbf{M}$ irror $\mathbf{B}$ ased $\mathbf{C}$ urrent $\mathbf{M}$ ultiplier                                                 |  |  |

| MIMO                                | $\mathbf{M}$ ulti Input $\mathbf{M}$ ulti Output                                                                                |  |  |

| mMTC                                | $\mathbf{M} \text{assive } \mathbf{M} \text{achine } \mathbf{T} \text{ype } \mathbf{C} \text{ommunications}$                    |  |  |

| MOS                                 | $\mathbf{M} \mathrm{etal} \ \mathbf{O} \mathrm{xide} \ \mathbf{S} \mathrm{emiconductor}$                                        |  |  |

| $\mathbf{NR}$                       | $\mathbf{N}$ ew $\mathbf{R}$ adio                                                                                               |  |  |

| OOB                                 | Out Of Band                                                                                                                     |  |  |

| PAD                                 | $\mathbf{P} ower \ \mathbf{A} mplifier \ \mathbf{D} river$                                                                      |  |  |

|                                     |                                                                                                                                 |  |  |

| PPA                                 | $\mathbf{P}\mathrm{re}\ \mathbf{P}\mathrm{ower}\ \mathbf{A}\mathrm{mplifier}$                                                   |  |  |

| PPA<br>RF                           | Pre Power Amplifier<br>Radio Frequency                                                                                          |  |  |

|                                     | *                                                                                                                               |  |  |

| $\mathbf{RF}$                       | Radio Frequency                                                                                                                 |  |  |

| RF<br>RX                            | Radio Frequency     Receiver                                                                                                    |  |  |

| RF<br>RX<br>SAW                     | Radio Frequency         Receiver         Surface Acoustic Wave                                                                  |  |  |

| RF<br>RX<br>SAW<br>SB               | Radio Frequency         Receiver         Surface Acoustic Wave         Single Balanced                                          |  |  |

| RF<br>RX<br>SAW<br>SB<br>TDD        | Radio Frequency<br>Receiver<br>Surface Acoustic Wave<br>Single Balanced<br>Time Division Duplexing                              |  |  |

| RF<br>RX<br>SAW<br>SB<br>TDD<br>TIA | Radio Frequency<br>Receiver<br>Surface Acoustic Wave<br>Single Balanced<br>Time Division Duplexing<br>Trans Impedance Amplifier |  |  |

To my sister Clarissa

## Introduction

In recent years, the diffusion of wireless devices, in developed and emerging economies, has enabled everyone to communicate. It follows that modern communication standards have to coexist with the previous generations, while satisfying the new requirements. The continuous demand for higher data rates has led to the opening of several new bands in the sub-6GHz range to mobile communications with channel bandwidth up to 100MHz. At the same time, low power and low cost architectures represent the best solution to meet the requirements of the increasingly popular massive-MIMO techniques.

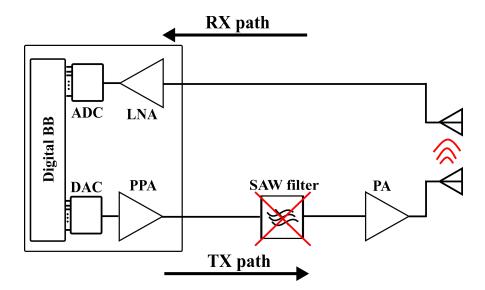

In order to enable multi-band operation and to improve connection quality through diversity and multiple-input multiple-output (MIMO) techniques, several transceiver chains are integrated on the same chip and connected to multiple antennas, each covering a sub-set of the desired bands. The addition of external filtering, i.e. SAW filter or duplexers avoids signal degradation caused by mutual interference, self-interference and out-of-band transmitter emissions but substantially complicate the board and the Input/Output PADs. In this way, not only the cost of the system will be limited by the external components, but also such a complicated routing limits system integration scaling down, main feature of modern technologies. Therefore, minimizing the external component counts represents a key goal in transceiver research, but it faces very stringent requirements in terms of receiver and transmitter noise and linearity.

These system considerations are even more true, in the broadband scenario that characterizes the new standards. Considering the design of a TX/RX chain: the transmitter needs to keep the emission (out-of-band noise and non-linearity) in the receiving band as low as possible, in order to avoid compromising the receiver performance. On the other hand, RX design needs to be prompt to handle high interferers. Plus, in both cases, power consumption is another important parameter (MIMO systems). This thesis is divided in two main parts, where a transmitter and a LNTA implementations are proposed.

The used simulation environment is Cadence Virtuoso® System Design Platform.

Part I describes the design of a current-mode transmitter, based on a passive upconversion mixer that combines the I and Q signals into a virtual ground provided by a closed-loop RF amplifier. In Chapter 1 a brief description of the new generation standards is provided, together with the design motivation. An analysis of the stateof-the-art is carried out in Chapter 2, while Chapter 3 describes in greater detail the proposed transmitter. Measurements results are summarized in Chapter 4, while Chapter 5 concludes this part.

Part II reports the analysis and design of a broadband noise-canceling LNTA, aiming at TVWS applications. Chapter 6 describes the TVWS scenario and explains the project motivation. In Chapter 7 the review of similar implementations are analysed and the LNTA topology is described. The simulation results are gathered in Chapter 8 and Chapter 9 draws the conclusions of the second part.

## Part I

# A Wideband SAW-Less Transmitter Operating in Closed-Loop with Embedded RF Filtering

### Chapter 1

## An introduction to 5G

Modern communication standards demand wireless transmitter to cover a wide carrier frequencies range and attaining increasingly channel bandwidths. In the first part of this dissertation, the design of a wideband SAW-less TX with embedded RF filtering, enclosed within a resistive loop is presented. This chapter presents the 5G sub-6GHz environment, starting from the analysis and considerations presented in [7] and lists the challenges related to SAW-less architectures, in addition to general system considerations.

#### **1.1** General considerations

The arrival of LTE (Long Term Evolution) has made an important change into people everyday life, although it can be questionable that it had a larger impact than any other technology to developed and emerging economies, giving benefits to any kind of user.

The mobile industry represents the world's leader engine of innovation, because of the exponentially increasing smartphone adoption and the high quality service provided by the LTE. In most countries, in fact mobile is the main platform to Internet access.

However, this growing environment will keep rising, by extending the network coverage even to rural areas, making the mobile services more and more affordable, providing relevant content and increasing digital skills.

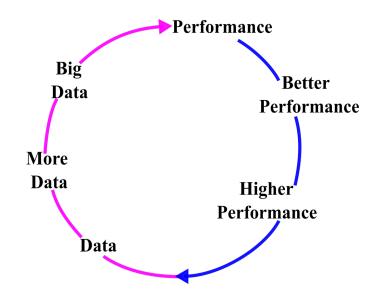

Starting with the availability of LTE data, an exponential growth of data consumption is keeping approaching. It follows the *Data flywheel effect*, which combines mobility, good network performance and desirable content into a virtuous cycle [7] (Fig.1.1).

At this point, as the user experience improves, the consumed data increases, following the trend of 'data demand' that has always been one of the main target of mobile industry, since the arrival of LTE.

Actually, to provide the required higher throughput, new techniques have been developed, making the *wheel* running faster.

Figure 1.1: DataFly Wheel effect

Mobile communications are now moving into the 5G world that can be considered an evolution of the previous LTE but also a revolution, thinking about the 5G New Radio (NR).

According to [7] the definition of 5G can be satisfied by driving the average data throughput in tens of gigabits per second ranges.

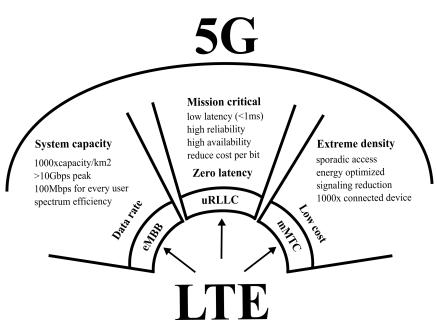

The current 3GPP standards, moving towards the 5G requests, is able to provide 2 to 3 times greater data rates, exploiting new standardized methods (Fig.1.2):

- eMBB (Enhanced mobile broadband) based on growing the system capacity, aiming at 1000x capacity. This aspect will characterize the sub-6GHz 4G and 5G

- uRLLC (Ultra reliable low latency communications) that is very important for critical implementation, requiring high reliability and availability, in addition to very low latency

- mMTC (Massive machine-type communications) strictly correlated to the IoT (Internet of Things) applications, thus requiring low cost and low data rate

#### 1.2 Towards 5G

As reported in Eq.(1.2) (Shannon-Hartley theorem) the capacity of a link depends on the number of data streams, bandwidth and channel noise.

$$C\left(\frac{B}{S}\right) = MB\log[2]\left(1 + \frac{S}{N}\right) \tag{1.1}$$

Figure 1.2: 5G targets

where C is the channel capacity in bits/second, M is the number of channels (related to massive MIMO applications), B is the bandwidth and  $\frac{S}{N}$  it the signal to noise ratio.

At this point, the main goal in modern standard is to increase the data rates, as already stated. To achieve this goal it is possible to:

- increase the bandwidth

- increase the number of paths M

- increase the Transmit Power (S)

- reducing the noise (N)

Different techniques have been proposed to attain the required performance. Wider bandwidth can been achieved through carrier aggregation (CA), the modulation order has been improved and also MIMO is under deeply investigation.

Carrier Aggregation is a new technique in which different channels are used to cover a wider bandwidth, with the help of a supplementary carrier.

Increasing the complexity of the modulation allows to increase the number of bits per symbol or data rate. However, in order to obtain the expected results, the SNR must be improved.

From the transmitter point of view, the RF amplifier must minimize the emission and noise level. At the same time the TX should also be able to manage a wider dynamic range, to maximize efficiency which is extremely important in these applications.

The number of paths is another key point, as deeply related to MIMO approach, used to increase the mobile systems bandwidth, involving to send and receive more than one data stream onto a single radio, exploiting at the same time the use of multiple antennas.

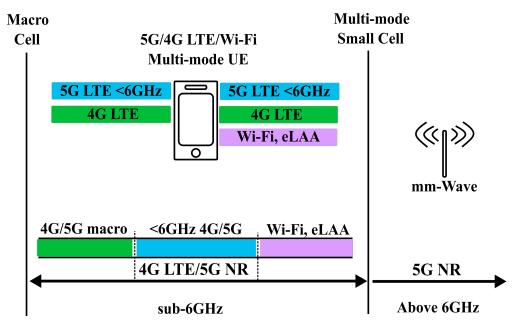

Figure 1.3: Skyworks vision of the 5G ecosystem

Taking into account all the previous considerations, the RF front-end circuitry complexity is increasing, in order to guarantee the claimed performance.

Fig.1.3 shows the 5G environment. There are two main frequency range of activities: sub-6GHz and at mmWave. The first one represent the range of application of the architecture proposed in this work.

In this frequency range, both traditional 4G LTE systems and modern 5G NR should coexist. It follows that the design challenges (reported in the next section) are quite similar to the typical LTE architectures. However, wider bandwidth for higher throughput is an additional request.

Eventually, 5G represents the next step of the 4G architectures, where all the old features need to be achieved and improved.

#### 1.3 Modern standard communication platforms

5G communications below 6GHz are characterized by highly demanding New Radio (NR) interface. Wireless transmitter should be able to cover a wide carrier frequencies range, with channels up to 100MHz.

Compatibility with the previous standards is also a critical point, in fact the number of frequencies and the coexistence of multiple standards represent a limit for the platform costs and performance.

This aspect is even more critical considering the ever-growing approach of massive-MIMO techniques, to meet the demanded high data-rate. This implies the need of interactions among many antennas that further increase the complexity of the communication chains and platforms.

Figure 1.4: Typical SAW-less scenario

5G communication operates both in TDD and FDD. In the former case, the isolation between TX and RX is provided by the switching operation, the latter instead requires the help of external SAW filters/duplexers in order to avoid an unwanted leakage from the transmitter to the receiver. Both TDD and FDD have multiple bands of operation, each one asking for a specific filter.

The several numbers of Input-Output (IO) PADs require to externally connect the receiver to the transmitter and viceversa, strongly limiting the scalability of the CMOS process. The chip dimension, indeed, can be dominated by the IO PADs number and space occupation, making the possibility of exploitation of the technology scaling-down harder.

Although each antenna is able to work in a wideband frequency range, the burden of the external passive components will become unacceptable. Cost and performance will be strongly affected, since SAW filters (and also duplexers) are bulky and costly. For this reason, they become the dominant cost contributors and together with the complexity of the board, they will impact the Bill of Material (BOM) in a significant way.

Hence, modern architectures need to eliminate these bulky, costly and above all not tunable filters, which are not suitable for the state-of-the-art requirements (Fig.1.4).

However, removing the external filtering comes not for free. It actually makes the transceiver design even more challenging. The most sensitive part of the transceiver (the analog front-end) can be compromised, unless a different design approach is proposed.

There are two main issues, related to the leakage from TX to RX and they become even more crucial in a wideband scenario, as the one of modern communication standards:

• linearity: the transmitted signal represents the biggest blocker for the small receiver signal, together with many other interferers. Along the RX chain intermodulation or other non-linear effects may happen, causing undesired signals into the

receiver bandwidth or compression of the chain. However, this is a main concern of the RX design.

• out-of-band emission: out-of-band noise and non-linearity of the transmitter can degrade the front-end performance, when falling in the RX channel, which is actually quite close to the TX, in a wideband scenario. It is therefore important to keep the emission low, as it will be deeply described later in this work.

The architecture described in this thesis is quite innovative, as concern the design approach and it is able to achieve a wide signal bandwidth, still maintaining the out-ofband emissions low.

### Chapter 2

## State-of-the-art transmitters

State-of-the-art transmitters are presented in this chapter, which compares the possible solutions, highlighting advantages and drawbacks of the different implementations. This represents the starting point in the proposed transmitter design.

Although current-mode passive mixers, followed by a base-band transimpedance amplifier is recognized as the most effective receiver architecture, because of its outstanding linearity and noise, in transmitters several solutions are still researched with both active and passive mixers. In fact, classic analog topologies, based on a RF pre-power amplifier (PPA), are strongly limited by the efficiency-linearity trade-off, becoming even more important under technology and temperature variations.

This section presents different approaches, coming from the state-of-the-art, to the problem of TX design.

#### 2.0.1 Power-mixer [1]

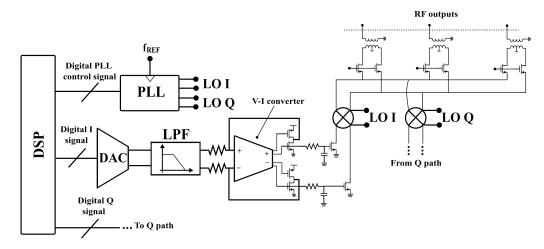

This work describes a fully reconfigurable multi-standard TX, reported in Fig.2.1. The operation are in voltage-mode for the base-band that consists into a DAC and two Biquad cells and it adopts an up-conversion power mixer. A variable gain V-I converter works as interface between the two domains (BB and RF), driving the mixer in class A/B.

This architecture, as a representative of power-mixer transmitter, eliminates the PPA and achieves good linearity, without using pre-distortion, however it is not very efficient.

#### 2.0.2 Direct-digital [2]

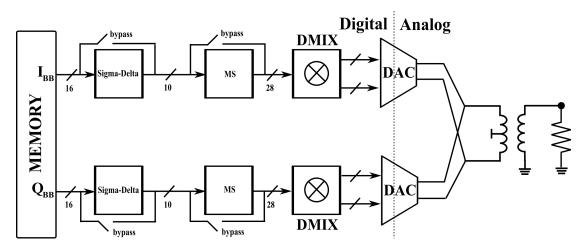

The "all-digital radio transceiver" represents a recent trend, where the RF functions are digitally implemented, but it suffers of large out-of-band noise due to quantization and efficiency is quite poor. Moreover, in order to achieve the optimum linearity performance

Figure 2.1: Class A/B power mixer TX

Figure 2.2: All digital RF transmitter

it needs pre-distortion that is not compatible with the massive MIMO approach, where many antennas interact with each other.

In this work, quantization noise in the RX band is reduced using a FIR notch that however costs extra power (Fig.2.2).

#### 2.0.3 Voltage-mode passive mixers [3–5]

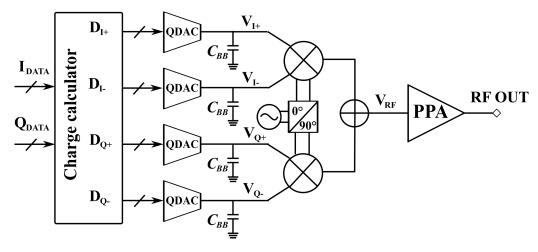

In literature, different and advanced transmitter architectures are based on voltage-mode passive mixers. In order to achieve high mixer linearity and avoid early compression, the voltage swing at the output must be constrained. It follows that either a low output power is delivered or a PPA is still necessary, as noticeable in the reported works.

Plus, even if a higher output power can be achieved, the performance are shown in back-off conditions.

Fig.2.3, Fig.2.4 and Fig.2.5 report three different voltage-mode passive mixers architectures, showing all the previously described drawbacks.

Figure 2.3: QDAC based transmitter

Figure 2.4: RQDAC based transmitter

Figure 2.5: Transmitter with notch filter mixer

Figure 2.6: N-path SC gain loop TX

#### 2.0.4 Current-mode passive mixers [6]

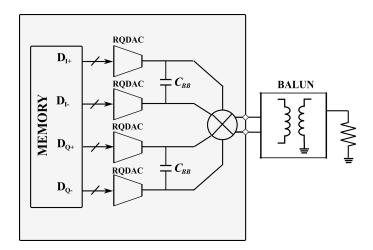

Current-mode passive mixers are hindered by the issue of creating a good virtual ground after up-conversion. For this reason, the idea of a transmitter architecture "symmetrical" to the state-of-the-art receiver is just a recent trend.

This work (Fig.2.6) describes a current-mode passive mixer, where a single-stage RF amplifier closed in feedback through a N-path filter implements the virtual ground. The transfer function is narrow-band (although the new standards are moving to wideband solutions) and it is exploited to reduce the OOB noise.

The single-stage amplifier attains a limited gain, therefore a single-ended PPA has been introduced, but it is not included inside the loop. For this reason, the linearity and driving capability issues are simply shifted to the PPA level.

## Chapter 3

## **Circuit description**

The proposed current-mode passive mixers transmitter is explained in this chapter, with a detailed description of the three-stage RF amplifier. A general introduction to N-path filters helps understanding the loop gain behaviour of the implemented TX that is qualitatively analysed, showing a band-pass filtering function, helping to solve the stability issue of the closed-loop solution.

#### **3.1** Proposed TX architecture

#### 3.1.1 N-path filters

As well explained in [8], the idea behind the concept of "N-path filters" goes back in the history. In fact, in [9] a narrow band-pass (BP) filter was proposed, based on a down-converter, a low-pass (LP) filter and an up-converter. Later, this basic concept has been applied in the "commutated networks" of [10], which implement a centerfrequency tunable switched-RC band pass filter and a band stop (BS) filter. However, because of the lack of transistors, mechanical switches have been used.

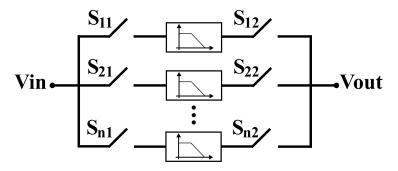

In 1960 [11] N-path filters have been proposed as a sliced version of the circuit of [9], which realizes a multiple (N) paths topology, where each path is active at a specific time as reported in Fig.3.1.

Figure 3.1: N-path filter: basic idea

Figure 3.2: N-path filter: RC low pass

Figure 3.3: N-path filter: only capacitors

Figure 3.4: N-path filter: one switches set

Designing LP (HP) filters is much easier than BP (BS) filters. On the basis of this consideration, exploiting down and up-conversion, it is possible to realize BP (BS) filters, based on LP (HP). Indeed, this is the general idea of N-path filtering, where instead of performing an RF filtering, at first the signal is down-converted to base-band by the first set of switches, then this down-converted version is lowpass (highpass) filtered and finally, the signal is up-converted again (Fig.3.1).

Starting from Fig.3.1, the circuit can be simplified as follows:

- the LP filter can be implemented as a simple RC filter (Fig.3.2);

- the resistor R is connected in each phase, therefore it can be moved before the first set of switches (Fig.3.3);

Figure 3.5: N-path filter: time domain analysis

Figure 3.6: DC value charging one capacitor

| Ţ | Ţ | Ţ | Ţ | Ţ | Ţ | Ţ | Ţ |

|---|---|---|---|---|---|---|---|

| Ī | Ī | Ī | Ī | Ī | Ī | Ī | Ī |

Figure 3.7: DC values stored on the capacitors

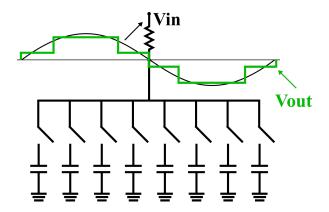

• the second set of switches can be removed, since when the switches are closed the output signal can be taken after the input R (Fig.3.4);

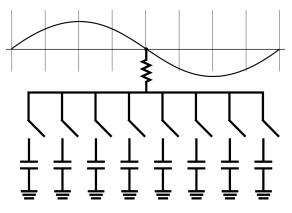

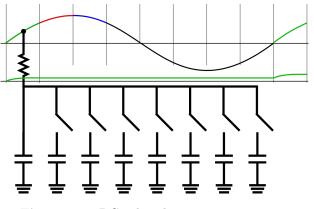

A frequency domain analysis is reported in [11], while in [11–15] it is discussed the time domain functionality.

Considering Fig.3.5, a simple time domain explanation can be provided, supposing at first that the clock frequency is equal to the input frequency. In each cycle, the capacitor is charged through the resistor at the input sinusoid value, with an RC time constant that is very large, in particular much greater than the time the switch is closed.

Figure 3.8: N-path filter: staircase approximation of the input signal

For this reason, the capacitance can charge just a little, each time the corresponding switch is on, since it sees always the same portion of the input sinusoid (Fig.3.6). Hence, after many cycles the dc voltage on the capacitance will be equal to the average value of the sinusoid in that interval (Fig.3.7).

Eventually, the output signal will look as a staircase approximation of the input signal, which becomes closer to the real sinusoid as the number of phases and capacitors increases.

On the other hand, if the input signal frequency is different from the clock frequency, each time the capacitors will see a different portion of the input signal, with the results of a final average DC voltage of the input signal equal to zero. It follows that for input frequency equal to the clock frequency the output is equal to the input, while for different frequencies the output is zero, resulting into a BP filter behaviour.

One of the main advantage of N-path filters is related to the way they can be implemented. In fact, they are basically realized with switches and capacitors, making CMOS technology the most suitable candidate for this kind of circuits. For this reason, the technology scaling and improvements have led to a renewed interest in this field. However, there are further positive characteristics. Indeed, the filter Q is extremely high (depending on the ratio of RC bandwidth and clock frequency) and simply changing the clock frequency, allows quick filter tuning.

As regards noise performance, the N-path filter shows good results, due to the zero DC current through the capacitance that allows low in-band noise. At the same time, the linearity is good as well since, in-band, the voltage swing across the switches is quite small, while out-of-band the signals are attenuated. Furthermore, the power consumption required to drive the switches scales with technology.

Unfortunately, this kind of circuits suffers of frequency folding and also harmonics represent a big issue in their behaviour.

An interesting and deeper discussion about N-path filters and their applications is also provided in [16] and [17], where LTI models of these time-varying architectures are

Figure 3.9: Architecture of the proposed transmitter

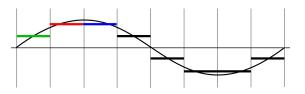

Figure 3.10: Driver amplifier IM3 suppression due to closed-loop operation

described and can be very useful, for a better understanding on how these circuits work.

#### 3.1.2 Closed-loop TX

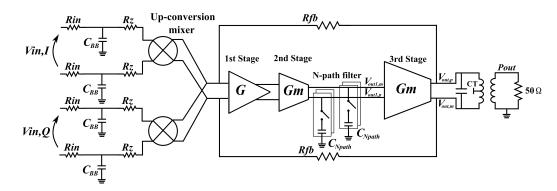

The architecture of the proposed transmitter is shown in Fig.3.9. The topology is wideband and, as the one described in [6], it is based on a current-mode passive mixer.

The base-band resistors  $R_{in}$  (300  $\Omega$ ) perform the voltage-current conversion and together with the capacitors  $C_{BB}$  (5 pF) attain a first order low-pass filtering, setting the input signal bandwidth to 100 MHz.

$R_z$ , equal to 80  $\Omega$ , represents the last base-band component. Its role is crucial both for stability and noise performance, but it will be discussed in the following sections. The direct (I) and quadrature (Q) base-band signals are up-converted by the current-mode passive mixer and added up into the RF virtual ground, which is the bottle-neck of the entire design. In fact, providing a good virtual ground at clock frequency (around GHz) represents one of the main challenge in this topology.

In order to overcome this issue, the transmitter RF side has been realized as a threestage amplifier with a broadband resistive feedback ( $R_f = 170 \ \Omega$ ). This loop, not only is able to provide the virtual ground but also performs the current to voltage conversion, directly driving the primary of the output balun. The proposed topology is entirely closed-loop (no external RF PAD), which represents a new feature compared to the other state-of-the-art solutions. It follows that some significant advantage of closed-loop systems, most of them distortion related, are embedded into this architecture. In fact, the distortion of the push-pull output stage of the amplifier is significantly suppressed by the loop.

Simulation results reported in Fig.3.10 compare the distortion generated by the output stage when operating in open-loop with the distortion produced by the driver, when it is enclosed in the proposed solution. At reasonable power level, an improvement of 12 dB can be observed.

However, closed-loop operation implies stability issues that, in this particular structure have been solved in a non-conventional way. In fact, a N-path filter, switched at the clock frequency, has been inserted as load of the second RF amplifying stage, as noticeable in Fig.3.9. As explained in the previous section, its behaviour is band-pass, ensuring high loop gain around the transmitter carrier frequency, while limiting the out-of-band gain. In this way, differential loop stability can be achieved even with process and temperature variations.

Eventually, all the advantages related to N-path filters, that is low power consumption, good noise and linearity performance and easy tuning are inherent in this solution. Above all, the circuit simplicity (only switches and capacitors are needed) allows compatibility with scaled technology, which is one of the main advantage of the whole TX chain.

The following section will describe the loop gain behaviour, showing simulation results that will help understanding in a qualitative way how this time-varying loop works.

#### 3.2 Loop gain analysis

#### 3.2.1 Linearity and stability considerations

The proposed architecture (Fig.3.9), being closed-loop, implies stability concerns. The closed-loop RF amplifier consists of a three-stage topology that allows to achieve sufficiently high gain. Unfortunately, the phase margin can be quite low, unless a solution for compensation is introduced.

At this point, it is important to remember that the transmitter needs high gain just in the bandwidth of interest, while out-of-band, not only for stability but also to improve noise performance a filtering behaviour is preferable.

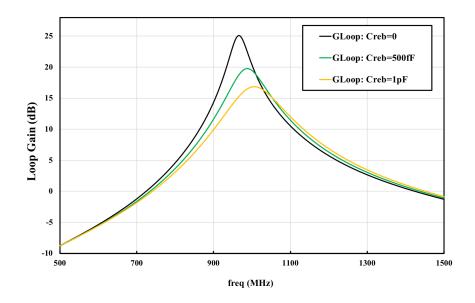

This supports the choice of a N-path filter as load of the second amplifier stage. Basically, it corresponds to the introduction of controlled pole, realized with switches and capacitors, which gives to the loop gain a band-pass shape, as noticeable in the black curve of Fig.3.11. Fig.3.12 reports the phase of the loop.

Figure 3.11: Loop gain w/o and with the rebalancing auxiliary mixer optimization

Figure 3.12: Loop phase w/o and with the rebalancing auxiliary mixer optimization

The N-path filter is clocked at the transmitter carrier frequency ( $f_{LO}$  equal to 1GHz), ensuring in this way a good virtual ground in the desired channel bandwidth. It follows that the loop works properly just in the frequencies of interest, while its gain starts decreasing far away from the carrier, as required by the application.

Despite the simplicity of the network, the N-path filter design is quite crucial. The switches needs to be big enough to manage the RF signals without introducing distortion and the capacitors size must be chosen considering a trade-off between stability and linearity performance, without neglecting the area consumption. Considering linearity at first, the value of the N-path capacitor is equivalent to 15 pF single-ended, resulting in a loop gain -3 dB bandwidth of about 23 MHz, above and below the carrier frequency with a peak gain of 25 dB. Hence, until the loop is working, it will manage to keep the distortion of the output stage low, as already explained and demonstrated in the previous section.

In order to increase the Q of the loop gain, to achieve higher values, the N-path capacitance must be increased. However, this will narrow the gain bandwidth, therefore intermodulation products that fall far away from the carrier will degrade the distortion performance, since not compressed by the loop. It follows that at very low frequency offsets linearity performance will be better, but in a wideband applications fashion a broadband loop gain represents a smarter choice.

As concerns stability, a qualitative and intuitive analysis is provided, which together with simulation results served as a basis for the circuit design.

At first, once the N-path is inserted in the loop, three resonating structures are present: the up-conversion mixer that with  $C_{BB}$  basically consists in another N-path filter, the second-stage load N-path filter and the output balun. Considering that the Q of the output balun is extremely low, the issue may concern the up-conversion mixer and the N-path filter.

The BB capacitance, as already described sets together with the input resistance the input low-pass filter cut-off frequency, and its value is quite low (5 pF). At the same time, the N-path capacitance is set for a wide loop gain bandwidth to 15 pF. It means that the poles of the two filters can be dangerously closed to each other.

Thus, to improve the phase margin (and also noise performance as it will be later explained) another base-band resistance  $R_z$  is put in series to the mixer, moving the zero that is usually set by the on-resistance of the switches to lower frequencies, to tackle the N-path pole.

Finally, the operational amplifier poles should be accurately set to higher frequencies, so that their contribution could be considered negligible.

#### 3.2.2 Effect of parasitic capacitance on N-path filter

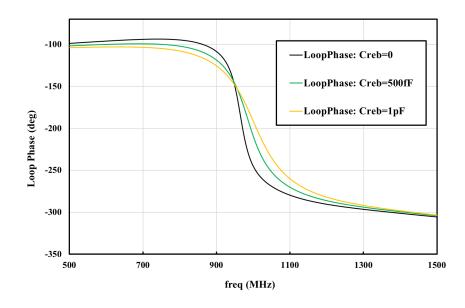

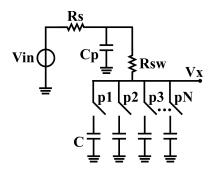

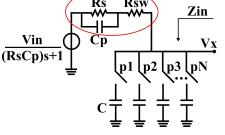

In order to understand the effect of parasitics capacitance on the designed TX, a general description of N-path filter affected by parasitics is required, since the mechanisms are actually the same occurring in the proposed architecture.

Parasitic capacitances represent one of the biggest issue to deal with, when designing a N-path filter. As reported in [17], the N-path filter can be modelled with a RLC tank. For this reason, the intuitive expectation is that the addition of parasitic capacitance at the input node will lower the center frequency of the filter, without introducing loss. However, voltage losses are actually introduced. In fact, modelling the input

(b) Effect of parasitic capacitance

(c) Equivalent source impedance

(d) RLC equivalent model

Figure 3.13: The effect of parasitic capacitance on the N-path filter

impedance of the filter with a RLC tank, if the inductance L and capacitance C values are independent from the parasitic capacitance, the value of the resistance R decreases, increasing  $C_{par}$  value.

The transfer function of the filter reported in Fig.3.13a around the LO frequency  $(f_{LO})$  is [18, 19]:

$$T(\omega_{LO} + \Delta\omega) = \frac{Y_s(j(\omega_{LO} + \Delta\omega))}{\frac{NCj\Delta\omega}{sinc^2(\frac{\pi}{N})} + \sum_{m=-\infty}^{+\infty} \frac{Y_s(j(Nm+1)\omega_{LO})}{(1+mN)^2}}$$

(3.1)

Following the rationale of [18], the series at the denominator of Eq.(3.1) can be called  $Y_{eff}$ , thus  $Y_{in}$  of Fig.3.13a will become:

$$Y_{in} = Re\{Y_{eff}\} - Re\{Y_s\} + j\left(\frac{NC\Delta\omega}{sinc^2(\frac{\pi}{N})} + Im\{Y_{eff}\} - Im\{Y_s\}\right)$$

(3.2)

The effect of parasitic capacitance can now be studied, starting from Eq.(3.1) and Eq.(3.2), with reference to Fig.3.13b. The circuit of Fig.3.13b is converted to the topology in Fig.3.13c, to obtain an equivalent solution of Fig.3.13a.

At this point,  $Y_s(s)$  is equal to  $\frac{1}{R_s + R_{sw}} \frac{R_s C_p s + 1}{R_s / R_{sw} C_p s + 1}$ .

The transfer function of the circuit in Fig.3.13c from  $V_{in}$  to  $V_x$  can be calculated as:

$$T(\omega_{LO} + \Delta\omega) = \frac{1}{jR_s//R_{sw}C_p\omega_{LO} + 1} \frac{1}{R_s + R_{sw}} \frac{1}{j\left(\frac{NC\Delta\omega}{sinc^2(\frac{\pi}{N})} + Im\right) + Re}$$

(3.3)

where:

$$Re = \frac{1}{R_s + R_{sw}} \sum_{n=-\infty}^{+\infty} \frac{1 + (1 + nN)^2 (R_s / / R_{sw}) R_s C_p^2 \omega_{LO}^2}{(1 + nN)^2 \left[ 1 + (1 + nN)^2 (R_s / / R_{sw})^2 C_p^2 \omega_{LO}^2 \right]}$$

(3.4)

$$Im = \frac{1}{R_s + R_{sw}} \sum_{n = -\infty}^{+\infty} \frac{(R_s - R_s / / R_{sw}) C_p \omega_{LO}}{(1 + nN) \left[ 1 + (1 + nN)^2 (R_s / / R_{sw})^2 C_p^2 \omega_{LO}^2 \right]}$$

(3.5)

Therefore, from Eq.(3.3) the new center frequency of the N-path filter can be computed and it can be noticed (Eq.(3.6)) that it is shifted to lower frequency:

$$\omega_c = \omega_{LO} - \frac{Imsinc^2(\frac{\pi}{N})}{NC} \tag{3.6}$$

Modelling the input impedance of the filter with a RLC tank (Fig.3.13d) is useful to understand the origin of the losses of the filter due to the capacitance. The values of the components are described in the following equations:

$$\frac{1}{R_m} = Re - \frac{1}{R_s + R_{sw}} \frac{1 + (R_s / / R_{sw}) R_s C_p^2 \omega_{LO}^2}{1 + (R_s / / R_{sw})^2 C_p^2 \omega_{LO}^2}$$

(3.7)

$$C_m = \frac{NC}{2sinc^2(\frac{\pi}{N})} \tag{3.8}$$

$$L_m = \frac{1}{C_m \omega_{LO}^2} \tag{3.9}$$

It results that only the resistive part of the tank is affected by the parasitic capacitance, indeed  $R_m$  decreases as  $C_p$  increases, causing filter losses.

In summary, the effect of parasitic capacitance of a N-path filter causes:

- lowering of the effective impedance, reducing the peaking of the bandpass filter

- shifting of the center frequency with respect to the desired value

The higher the switching frequency, the worse is the filter behaviour. Reducing the harmonic contents of the filter, which corresponds to an increase in the number of phases, can mitigate this effect. In fact, shortening the switching time will also minimize the charge sharing between C and  $C_p$ . However, if most of the parasitic capacitance is due to the switches, then increasing the number of phase is not a suitable solution.

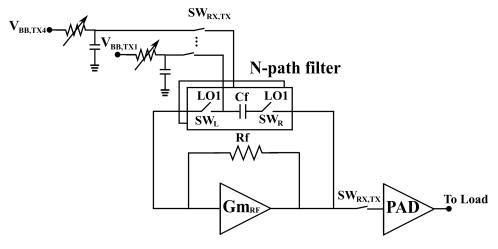

Figure 3.14: N-path filter with rebalacing auxiliary mixer

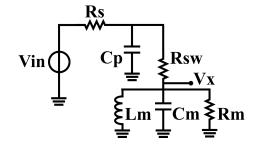

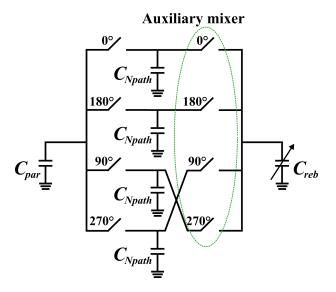

#### 3.2.3 Rebalancing auxiliary mixer

Considering the proposed transmitter, the N-path filter, introduced as load of the second stage, really suffers the issue of parasitic capacitance, especially as concern the alignment of the center frequency with the carrier frequency.

This happens because the RF nodes of this filter, corresponding to the output of the second stage and the input of the third one, see a big parasitic capacitance, despite it has been minimized as much as possible during the layout drawing.

For this reason, as shown in Fig.3.11, the center frequency of the loop gain is shifted at a lower frequency. In literature, different solution to correct this alignment can be found [18], based for instance on  $G_m$  cells. The same option can be adopted also for the closed-loop TX, but it will cost extra power consumption, directly proportional to the amount of phase shifting.

It is instead possible, introducing an auxiliary mixer, to perform the rebalancing operation without increasing considerably the power consumption and the complexity of the system. As reported in Fig.3.14, an auxiliary mixer is added at the base-band side of the filter.

It samples the voltage stored on the N-path capacitors, due to the RF parasitic capacitance  $C_{par}$  and it up-converts it on a variable capacitance  $C_{reb}$ , whose purpose is to emulate the RF parasitic. However, the order of the sampling phases in the auxiliary mixer is opposite with respect to the N-path one. For this reason, when the voltage produced on  $C_{reb}$  is down-converted on the N-path capacitors, it appears as the image signal of the one produced by  $C_{par}$ , thus the two signals cancel out, reducing the shifting effect.

Fig.3.11 reports the simulated loop gain when the auxiliary mixer is not active and for different values of  $C_{reb}$ . It pops up that the peak has been moved back to the original

Figure 3.15: RF OpAmp first and second stage

center frequency, which corresponds to a symmetrical loop behaviour with respect to the carrier frequency.

Unfortunately, the peak gain is reduced, because of switched-capacitors contributions caused both by the N-path and the auxiliary mixer. However, as also presented in literature, the peak can be re-aligned but the losses cannot be recovered.

It results that a good trade-off between alignment and peaking needs to be found, when dealing with this kind of applications, which is the reason of having a degree of freedom in activating and de-activating the auxiliary mixer (through external programmability) as in the proposed architecture.

#### 3.3 Three-stage RF operational amplifier

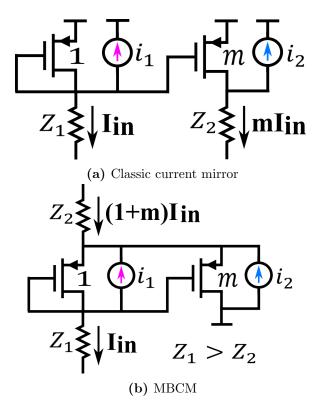

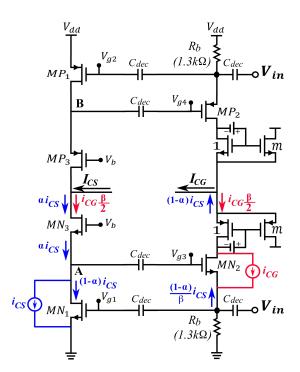

This section gives a detailed description of the RF amplifier topology. The first stage provides 12 dB of broadband differential gain. The second stage consists of a push-pull transconductor loaded by a differential N-path filter, clocked at the carrier frequency  $(f_{LO}$  equivalent to 1GHz). Eventually, the output signal is provided by the third stage, a push-pull cascoded transconductor.

The N-path filter, introduced to keep the circuit differential stability under control, is seen by common-mode (CM) signals as a large capacitive load. In addition, the upconversion mixer pole is also present. It follows that common-mode stability could be undermine.

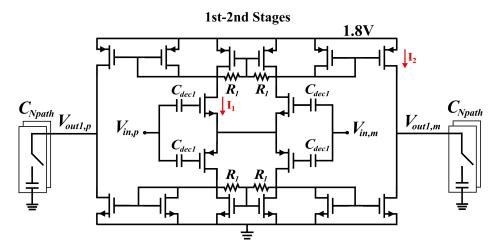

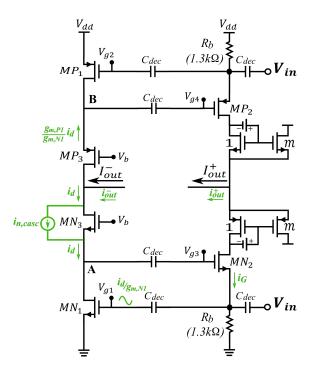

Fig.3.15 shows the schematic of the first and second stages of the RF amplifier.

The first stage design has been carried on, in order to drastically reject CM signals up to frequencies well above the carrier, still providing at the same time enough gain to achieve the required linearity and noise performance.

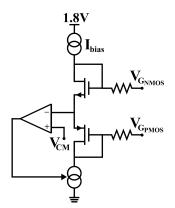

The NMOS-PMOS input stage presents AC coupled inputs, allowing to bias the NMOS and PMOS with different DC voltages provided by the circuit in Fig.3.16. Basically,

Figure 3.16: Bias circuit of the RF OpAmp first stage

Figure 3.17: RF OpAmp third stage

a current source injects the desired bias current (or a scaled replica) in two diodeconnected devices (NMOS and PMOS respectively) stacked onto a tail current source, whose current is closed-loop controlled.

In fact, the proposed circuit Fig.3.16 is not only able to properly bias the gate of the NMOS and PMOS devices, but it also sets the CM node (the sources of the two devices) to a desired voltage. In fact, when the CM voltage departs from the target value, the closed loop control, implemented with a simple operational amplifier (classic differential pair with active load), changes the tail current value, in order to return to the supposed operating condition. For this reason, the amplifier bias can be easily scaled down with the supply voltage, as well as for the current.

Considering the small signal behaviour, the topology of Fig.3.15 basically consists of two back-to-back CMOS differential pairs, which exploits current-reuse mechanism that helps achieving a differential transconductance equal to twice the transconductance  $(g_m)$  of each transistor. It follows lower current consumption and noise.

The differential pairs presents an active load of current mirrors that easily bias the second stage, where the signal currents are also recombined.

On the other hand, the common-mode transconductance corresponds to the parasitic conductance to ground at the common-source node. At the same time, the CM load impedance is twice smaller than the differential one, further increasing the required common-mode rejection.

The bias currents are  $I_1 = 608 \mu A$  and  $I_2 = 2.4 m A$ . The input decoupling capacitance is  $C_{dec1} = 2pF$ , while the load resistance is  $R_1 = 2k\Omega$ .

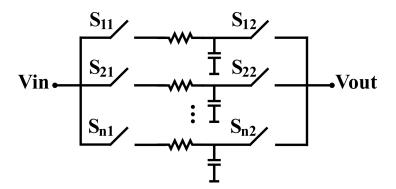

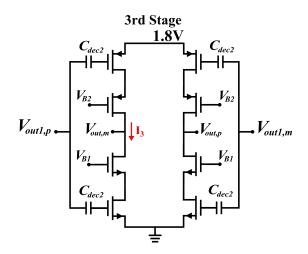

The third (output) stage, reported in Fig.3.17, implements a cascoded class-A/B pushpull topology that directly drives the differential load. This in quite innovative, with respect to the state-of-the-art transmitters. In this way, the output voltage swing is constrained between the supply rails, making the architecture compatible with deeply scaled transistors even for 1.8V supply.

Despite the voltage swing (i.e. the voltage efficiency) is about halved, the current efficiency is doubled, keeping the overall efficiency almost constant. Moreover, different from all the previous transmitter, the output stage that is the output driver is included in the feedback loop, allowing the output signal to closely approach the rails, without degrading the linearity performance. In fact, as already demonstrated in the previous section, the distortion of this stage is killed by the loop, as in a usual closed-loop operational amplifier.

The bias current is  $I_3 = 4mA$ . The input decoupling capacitance is  $C_{dec2} = 8pF$ . The cascode bias voltages are internally set by a resistive voltage divider to the nominal condition of  $V_{B1} = 1.2V$  and  $V_{B2} = 0.6V$ , in order to leave enough voltage headroom to the transconductor devices, when large signal occurs.

The output stage is actually implemented with sliced version of the circuit reported in Fig.3.17, introducing a programmability degree of freedom. This helps reducing the static current in case of low power delivering, in order to maintain good efficiency even in this condition.

The differential output is eventually converted to single-ended, by an on-chip balun with a turns ratio close to 1.

### Chapter 4

### **Prototype and measurements**

In this chapter the prototype measurement results are reported and compared with the state-of-the-art solutions.

#### 4.1 Systems considerations

The emission generated by the transmitter in the adjacent receiver bandwidths constitutes one of the main challenge in TX design. This becomes even more important in the state-of-the-art SAW-less applications. In fact, SAW filters do not represent an option in wideband systems, since they are bulky, costly and lossy. Above all, these are narrow band filters, characterized by en extremely low tuning capability.

For this reason, reducing TX signal emission has become a key point to meet modern standard requirements of:

- out-of-band noise

- linearity

#### 4.1.1 Out-of-band noise

If on the receiver side of the chain the in-band noise is crucial, for transmitter the biggest issue is represented by the noise out-of-band. The traditional approach was to put a SAW filter before the power amplifier to eliminate this undesired leakage, however, as already mentioned, in recent years SAW-less applications are in order.

Therefore, a low-noise transmitter must be designed, optimizing the structure to provide some filtering along the chain.

Considering the proposed architecture (Fig.3.9), the main noise contributors (according to theory and simulations) near the carrier frequency are represented by the feedback resistors, followed by the base-band resistors. Then, the third contribution is given by the amplifier input stage, whose noise transfer function would increase as the mixer up-converted impedance drops.

Figure 4.1: Out-of-band noise measurement setup

The resistors  $R_z$  added in series to the mixer, not only improve the stability margin (as explained in the previous section) but they also avoid the up-converted impedance dropping, keeping the noise of the first stage at an acceptable level, until the filtering effect of N-path occurs at large frequency offsets.

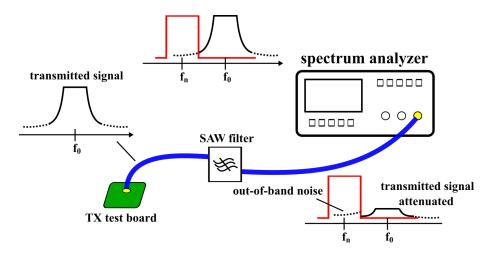

The procedure to measure output noise emission of an integrated transmitter is usually the following: the RF output is connected to the spectrum analyzer through a SAW/duplexer filter chosen accordingly to the signal carrier. In this way, the stop-band of the external filter will attenuate the transmitted signal, while the noise will pass unchanged, with the exception of the insertion loss.

Thus, the noise can be measured avoiding the instrument saturation as shown in Fig.4.1.

Actually, when the LO signals are provided with an external signal generator to the on-chip dividers, a further SAW filter is used to attenuate the phase noise of the aforementioned instrument.

Finally, it must be said that, it is quite hard to discriminate between noise and nonlinearities, during this kind of measurements, especially when the transmitted power reaches the peak values.

For the proposed prototype the LO frequency has been set to 965 MHz, with a signal frequency of 970MHz, delivering a power of 3 dBm after de-embedding the losses. In this condition, the measured output noise at 80 MHz offset from the carrier is -153.5 dBc/Hz.

#### 4.1.2 Linearity

#### 4.1.2.1 ACLR

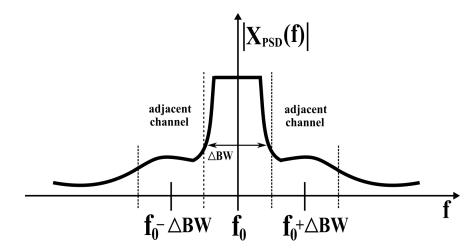

The Adjacent Channel Leakage Ratio(ACLR) or Adjacent Channel Power Ratio(ACPR) measurement gives information about the linearity of the transmitter [20, 21]. This kind

Figure 4.2: Adjacent channel emission spectrum

Figure 4.3: CIM3 generation

of unwanted emissions should be firmly restricted such that interference with the other radio systems is kept low.

The adjacent channel emission level is one of the most important parameter in TX architecture. It is generally defined as the ratio between the adjacent channel power, integrated on a specific bandwidth, and the total delivered power in the transmission channel as reported in Eq.(4.1):

$$ACLR = \frac{\int_{f_0 - \Delta BW/2}^{f_0 + \Delta BW/2} PSD(f) \, df}{\int_{f_0 - \Delta BW/2}^{f_0 - \Delta BW/2} PSD(f) \, df}$$

(4.1)

where PSD(f) is the Power Spectrum Density of the transmitted signal. This concept is clarified in Fig.4.2.

Basically, the adjacent channel powers come from spectral regrowth and non-linearity of the amplification stages, which in the proposed architecture are reduced by the closedloop operations.

#### 4.1.2.2 CIM3

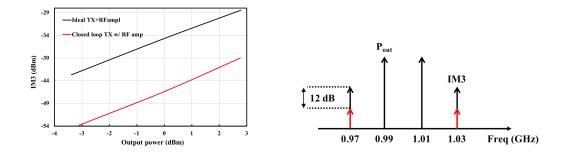

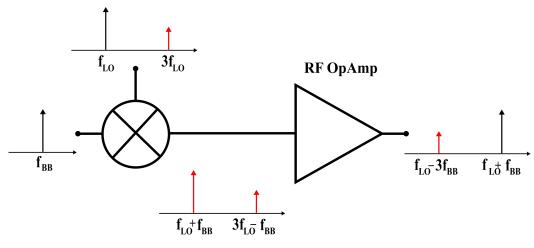

The Counter third order intermodulation products (CIM3) is more and more recognized as another important linearity parameter in transmitter characterization. As reported in [22], the CIM3 results from the  $3^{rd}$ -order intermodulation (IM3) product of signals around  $f_{LO}$  and  $3f_{LO}$  when using 25% or 50% duty-cycle LO signals for mixer driving.

In fact, if the frequency of the input signal is equal to  $f_{BB}$ , after the up-conversion mixer and the RF amplifier, the desired transmitted signal at  $f_{LO} + f_{BB}$  will be produced, together with an undesired CIM3 component at  $f_{LO} - 3f_{BB}$ .

In particular, for 25% duty-cycle LO, after the up-conversion of the base-band signal  $(f_{BB})$ , assuming a lower sideband I-Q rejection, the mixer output will show a component at  $f_{LO}+f_{BB}$  and  $3f_{LO}-f_{BB}$ . These two tones are intermodulated by the non-linearity of the amplifier, resulting in an intermodulation product at  $f_{LO}-3f_{BB}$  at the transmitter output (Fig.4.3).

From this rationale, it becomes clear that in order to reduce CIM3 contribution, the odd harmonics of the LO signals should be suppressed. Different solutions have been proposed in literature, such as harmonic rejection, but most of them requires calibration or off-chip filtering components.

On the other hand, another possibility is to modify the LO signals duty-cycle or number of phases, in order to suppress the LO harmonics. However, this solution, which is actually the most suitable for the proposed transmitter, will put extra design effort on the LO signals generators (dividers), implying above all an increase in power consumption that will reduce the overall architecture efficiency.

#### 4.2 Measurement results

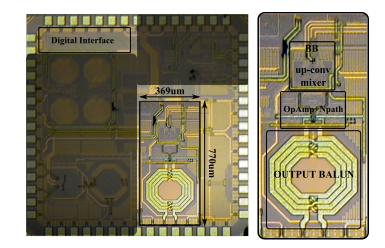

The chip prototype, highlighted in Fig.4.4 belongs to a multi-project chip, implemented in TSMC 28nm CMOS technology and its active area is equivalent to  $0.28mm^2$ . In order to perform the testing, the chip has been bonded on a dedicated printed circuit board (PCB) designed with the software Autodesk EAGLE.

An on-chip digital interface allows to turn on and off the desired circuit in the multiproject chip. The programmability bits are provided off-chip by the SPI (serial peripheral interface) NI USB-8451 (National Instruments), controlled by the dedicated software. Once the chip is correctly programmed, it is biased through National Instruments current (NI-9265) and voltage (NI-9263) modules, mounted on the National Instrument chassis cDAQ-9171 (Chassis compactDAQ).

The chip was tested with an operating frequency equal to 1GHz, with the exception of out-of-band noise measurements, where the LO frequency has been moved to 965MHz.

Figure 4.4: Chip prototype

Figure 4.5: Up-conversion gain

The LO signals are provided by the Agilent N5183A MXG signal generator and the 25% duty-cycle is obtained with an on-chip divider.

The BB signals in case of a single-tone or two tones test are given by the Agilent E8257D PSG signal generator, while in case of modulated signal test the input is provided by Agilent E4438C ESG Vector Signal Generator.

The output signal has been observed on the PXA Signal Analyzer N9030A.

The transmitter is able to achieve a maximum measured output power, delivered to the load of 8 dBm, after de-embedding the cable and PCB (printed circuit board) losses (around 1.7 dB).

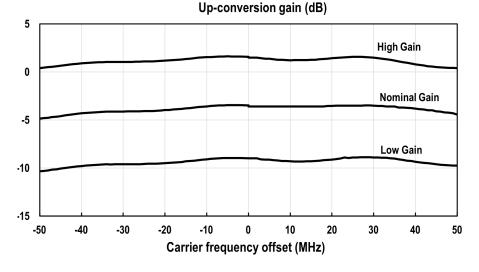

The up-conversion gain is reported in Fig.4.5. The base-band resistors, as well as the feedback one can be programmed through a digital interface. In fact, it is possible to reduce their value in order to increase or decrease the up-conversion gain by 5 dB. It

Figure 4.6: ACLR with modulated output spectrum

is noticeable that, in all the three gain configurations, a signal bandwidth exceeding 100MHz has been measured, aligned with the state of the art required bandwidth.

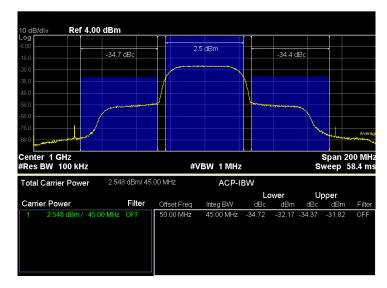

The measured output spectrum for a QPSK 50MHz-RF bandwidth modulated signal is reported in Fig.4.6. The ACLR, in this condition, is equal to -40 dBc, for a corresponding output power of 3 dBm.

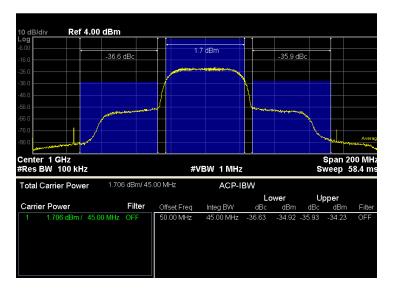

Fig.4.7 shows the output spectrum for a single-tone input signal corresponding to 3.9 dBm output power, where the CIM3 is -47 dBc. The CIM3 has also been measured for different BB frequency, with respect to the output power and the results are reported in Fig.4.8. The CIM3 behaviour is quite interesting, in fact, for an output power of 3 dBm its value is better than -49 dBc for single-tone frequency offsets up to 25MHz.

As already mentioned, the out-of-band noise, considering an output power of 3dBm at a frequency offset of 80MHz away from the carrier, corresponds to -153.5 dBc/Hz. The measurement setup is reported in the previous section (Fig.4.1).

Table 4.1 summarizes the prototype measurements, in comparison with the state-ofthe art solutions that implement different kind of architectures, the one analysed in Chapter 2. The active area of the proposed transmitter is lower than all the other topologies that also have an on-chip balun, at the same time it is not much bigger with respect to the solutions with an external balun.

The most noticeable result is represented by the RF bandwidth, which is equal to 50MHz. This value is more than twice with respect to the other implementations.

Although a wider bandwidth has been achieved, the other performance are aligned with the state-of-the art. In fact, considering 3 dBm of average output power, the

Figure 4.7: CIM3 at 3.9 dBm output power spectrum

Figure 4.8: CIM3 for different single tone output power and BB frequency

ACLR is -40 dBc and CIM3 is -49. These values are close to the one of [6], which also exploits a current-mode passive mixer, but reaching a 4 dB lower delivered power.

Other implementations, such as [2, 4], achieve better results but exploiting digital pre-distortion. [5] shows very good CIM3, attained trapping the third harmonic of the LO signal, unfortunately this is not beneficial for the ACLR, which is almost equal to the one achieved in the proposed TX, but with a narrow band.

The out-of-band noise has been measured with a carrier frequency of 965MHz and a signal frequency of 970MHz. The delivered power is equal to 3 dBm, after de-embedding

|                                 |                                       |                |              |                  |                         | 1-1                                                                 |                                                 |

|---------------------------------|---------------------------------------|----------------|--------------|------------------|-------------------------|---------------------------------------------------------------------|-------------------------------------------------|

|                                 | This                                  | [1]            | [3]          | [4]              | [2]                     | [5]                                                                 | [6]                                             |

|                                 | work                                  | ISSCC'13       | ISSCC'15     | ISSCC'16         | ISSCC'17                | ISSCC'18                                                            | ISSCC'16                                        |

| Technology                      | 28nm                                  | 55nm           | 28nm         | 28nm             | 28nm                    | 14nm FinFET                                                         | 65nm                                            |

| Architecture                    | Closed loop<br>passive power<br>mixer | Power<br>mixer | QDAC         | RQDAC            | $\Delta\Sigma + MS$ DAC | Notch filter<br>mixer                                               | SC GLoop+<br>Gain boost<br>Npath filter+<br>PAD |

| Integrated<br>balun             | YES                                   | YES            | NO           | NO               | YES                     | YES                                                                 | NO                                              |

| Chip area<br>[mm <sup>2</sup> ] | 0.28                                  | 1.3            | 0.25         | 0.22             | 0.82                    | 1.04                                                                | 0.038                                           |

| Supply<br>Voltage[V]            | 1.8/1.2                               | 1.8            | 0.9/1.8      | 0.9/1.1          | 0.9/1.5                 | NA                                                                  | 1.1/2.5                                         |