# Università degli Studi di Pavia

Dipartimento di Ingegneria Industriale e dell'Informazione,

Ph.D. School in Microelectronics

# Frequency Multipliers in SiGe BiCMOS for Local Oscillator Generation in D-band Wireless Transceivers

Author: **Mahmoud M. Pirbazari**

Supervisor: **Andrea Mazzanti**

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

February 2021

## **Abstract**

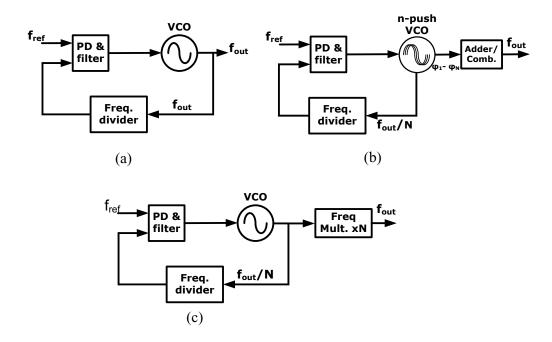

Communications at millimeter wave (mm-Wave) have drawn a lot of attention in recent years due to the wide available bandwidth which translates directly to higher data transmission capacity. Generation of the transceivers local oscillation (LO) is critical because many contrasting requirements, i.e. tuning range (TR), phase noise (PN), output power, and level of spurious tones, affect the system performance. Differently from what is commonly pursued at Radio Frequency, LO generation with a PLL embedding a VCO at the desired output frequency is not viable at mm-wave. A more promising approach consists of a PLL in the 10-20GHz range, where silicon VCOs feature the best figure of merit, followed by a frequency multiplier.

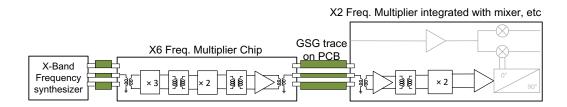

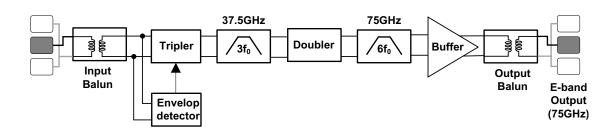

In this thesis a frequency multiplication chain is investigated to up-convert an LO signal from X-band to D-band by a multiplication factor of 12. The multiplication is done in steps of 3, 2, and 2. A sextupler chip comprises the tripler and the first doubler and the last doubler stage which upconverts the LO signal from E- to D-band is realized in a separate chip, all in a 55nm SiGe BiCMOS technology. The frequency tripler circuit is based on a novel circuit topology which yields a remarkable improvement on the suppression of the driving signal frequency at the output, compared to conventional designs exploiting transistors in class-C. The active core of the circuit approximates the transfer characteristic of a third-order polynomial that ideally produces only a third-harmonic of the input signal. Implemented in a separate break-out chip and consuming 23mW of DC power, the tripler demonstrates ~40dB suppression of the input signal and its 5th harmonic over 16% fractional bandwidth and robustness to power variation of the driving signal over a 15dB range. Including the E-band doubler, the sextupler chip achieves a peak output power of 1.7dBm at 74.4GHz and remains within 2dB variation from 70GHz to 82GHz, corresponding to 16% fractional BW. In this frequency range, the leakages of all harmonics are suppressed by more than 40dBc.

The design of the D-band doubler was aimed at delivering high output power with high efficiency and high conversion gain. Toward this end, the efficiency of a push-push pair was improved by a stacked Colpitts oscillator to boost the power conversion gain by 10dB. Moreover, the common-collector configuration keeps separate the oscillator tank from the load, allowing independent optimization of the harmonic conversion efficiency and the load impedance for maximum power delivery. The measured performance of the test chip demonstrated P<sub>out</sub> up to 8dBm at 130GHz with 13dB conversion gain and 6.3% Power Added Efficiency.

## **Acknowledgments**

I wish to thank my family before anything else because if it was not for them, I would be standing nowhere close to where I am now. I feel proud of Shiva, my wife, who stood beside me as a close friend despite all the ups and downs during our past years and I feel deeply indebted to my parents whose support for my education through all these long years was neverending.

I can't find the proper words to thank my supervisor professor Andrea Mazzanti for not only his deep knowledge and experience on the subject were always there to tap, but the level of his engagement in the research as a professor and his close collaboration with his students were not imaginable to me before joining the AIC Lab. Moreover, I am grateful to my colleagues for all their help, and above all, the warm and friendly atmosphere in our laboratory.

My Ph.D. research was defined within the framework of the European H2020 DREAM project. DREAM gave me an opportunity to be involved in a challenging project with a lot of room for innovations, as well as learning from the other designers of the team. The schedule of the project with the milestones planned ahead was a great help to me to keep my work organized. I am deeply grateful to the DREAM consortium for the opportunity and to the partners for the many fruitful discussions.

Infine, dopo aver trascorso più di tre anni in Italia, desidero esprimere la mia gratitudine per tutta l'ospitalità e lo spirito positivo che ho ricevuto qui. Il corso del mio dottorato nella bella Italia, rimarrà tra i miei migliori ricordi.

# **Table of contents**

| Chapter | r 1   | Introduction                                            |

|---------|-------|---------------------------------------------------------|

| 1.1     | Mot   | ivation8                                                |

| 1.2     | The   | DREAM project                                           |

| 1.3     | LO    | generation at mm-Wave frequencies12                     |

| 1.4     | Proj  | posed LO generation architecture                        |

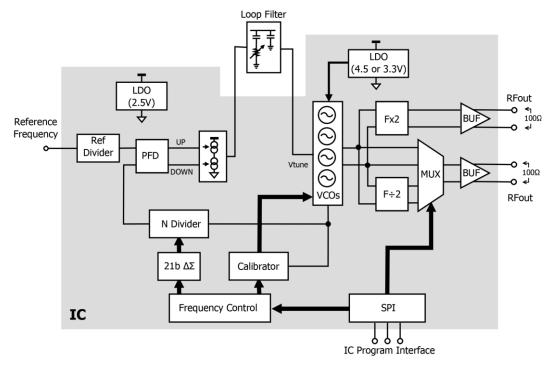

| 1.4     | 4.1   | X-band phase locked loop                                |

| Chapter | r 2   | E-band Frequency multiplier by 6                        |

| 2.1     | Circ  | cuit techniques for frequency multiplication            |

| 2.2     | Ord   | er of frequency multiplication stages24                 |

| 2.3     | Proj  | posed frequency tripler with 37.5GHz output frequency27 |

| 2.3     | 3.1   | Principle of operation                                  |

| 2.3     | 3.2   | Circuit design                                          |

| 2.3     | 3.3   | Measurement results of the tripler breakout             |

| 2.4     | Proj  | bosed frequency doubler with 75GHz output frequency34   |

| 2.5     | Mea   | surement results of the sextupler chip                  |

| Chapter | r 3   | D-band frequency doubler                                |

| 3.1     | Circ  | euit description40                                      |

| 3.2     | Mea   | surement results46                                      |

| Chapter | r 4   | Summary and future work                                 |

| 4.1     | Sun   | nmary54                                                 |

| 4.2     | Futi  | re work55                                               |

| Append  | lices | 57                                                      |

| Appe    | endix | I57                                                     |

| Appe    | endix | II60                                                    |

| Referen | ices  | 63                                                      |

# List of abbreviations

|         | Local Oscillation             |

|---------|-------------------------------|

| TR      | Tunning Range                 |

| LR      | Locking Range                 |

| PN      | Phase Noise                   |

| VCO     | Voltage Controlled Oscillator |

| PLL     | Phase Locked Loop             |

| BW      | Bandwidth                     |

| FBW     | Fractional Bandwidth          |

| HRR     | Harmonic Rejection Ratio      |

| FoM     | Figure of Merit               |

| PPF     | Poly Phase Filter             |

| mm-Wave | Millimeter Wave               |

| CS      | Common Source                 |

| CD      | Common Drain                  |

| IF      | Intermediate Frequency        |

# List of figures

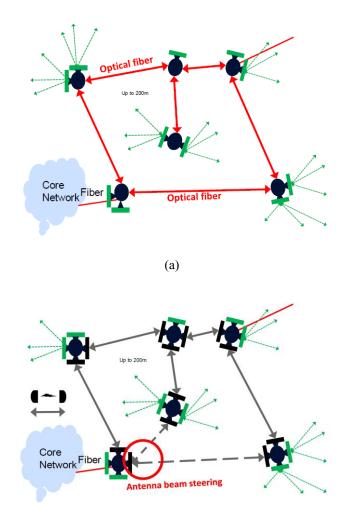

| Figure 1.1. Small cell backhaul connections by (a) fibre optic, (b) seamless fibre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | performance    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| wireless links [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9              |

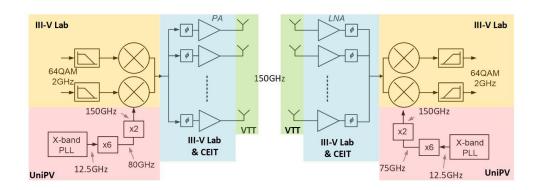

| Figure 1.2. System-level architecture of the DREAM's transceiver with the role of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f each partner |

| marked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11             |

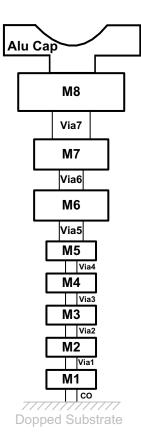

| Figure 1.3. Cross section of the metal stack of the 55nm BiCMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11             |

| Figure 1.4. LO generation at mm-wave frequency using (a) direct synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | s, (b) n-push  |

| technique, (c) frequency multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13             |

| Figure 1.5. The proposed LO chain to upconvert an X-band source to D-band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16             |

| Figure 1.6. simplified block diagram of StuW81300 frequency synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18             |

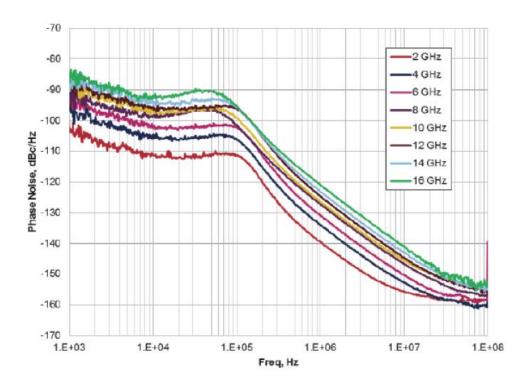

| Figure 1.7. Phase noise performance of StuW81300 frequency synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19             |

| Figure 2.1. Block diagram of the frequency multiplier by 6 chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21             |

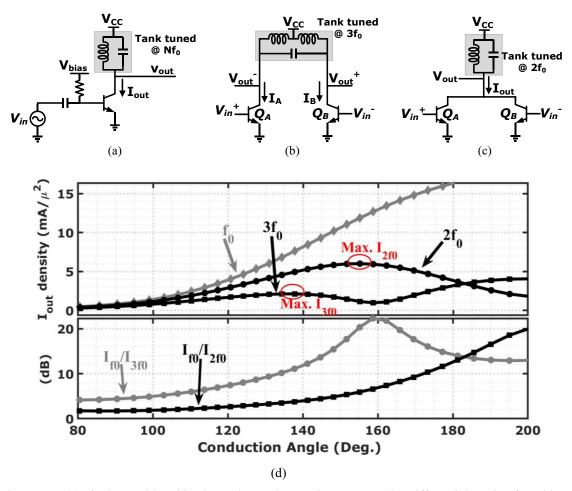

| Figure 2.2. (a) Single BJT biased in class-B/C as a harmonic generator, (b) Difference of the control of the co | ential version |

| for odd-order multipliers, (c) Differential version for even-order multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (push-push),   |

| (d) Harmonics of I <sub>out</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22             |

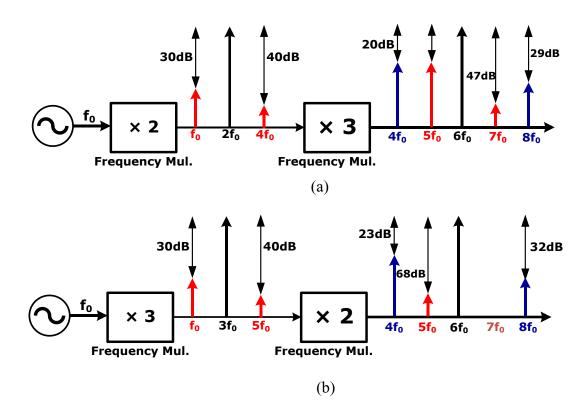

| Figure 2.3. Conceptual diagram to show effect of multipliers' order on outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | out spurs. (a) |

| Doubler first, (b) Tripler first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26             |

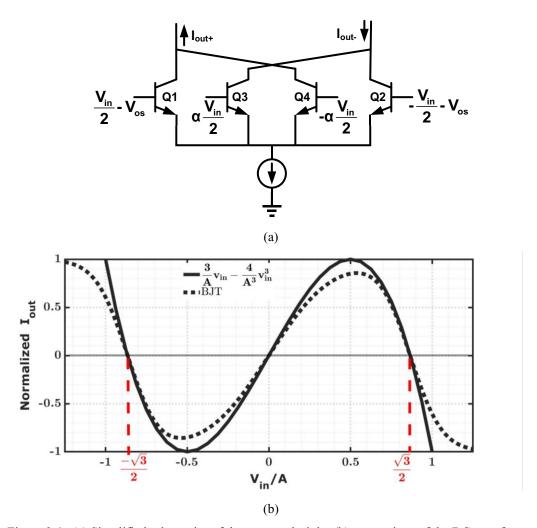

| Figure 2.4. (a) Simplified schematics of the proposed tripler (b) comparison of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e DC transfer  |

| characteristic with Eq. (2.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28             |

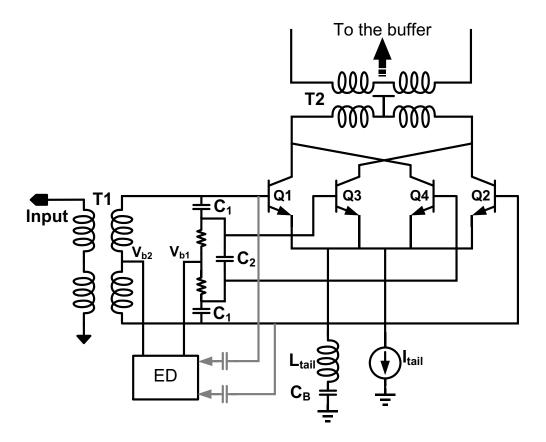

| Figure 2.5. Detailed schematics of the proposed Tripler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29             |

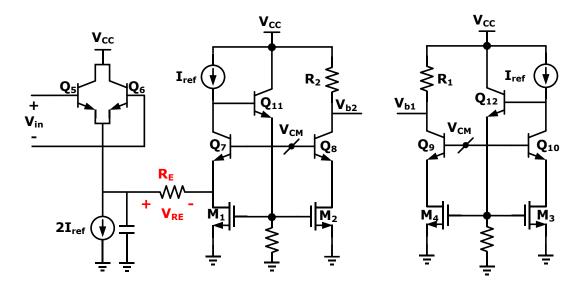

| Figure 2.6. The Envelope detector Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29             |

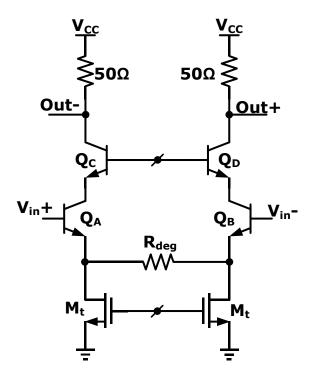

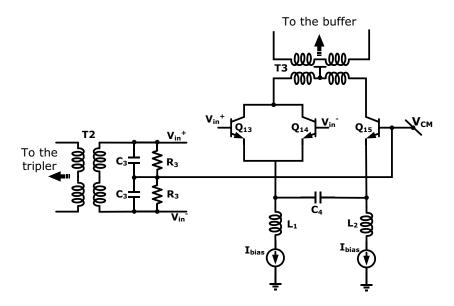

| Figure 2.7. Test buffer following the tripler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30             |

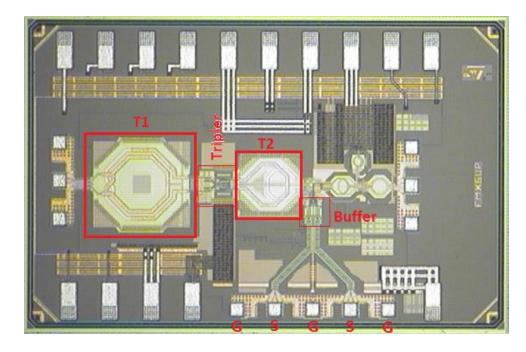

| Figure 2.8. Chip photograph of the tripler breakout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31             |

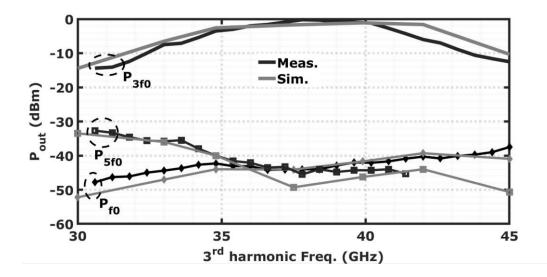

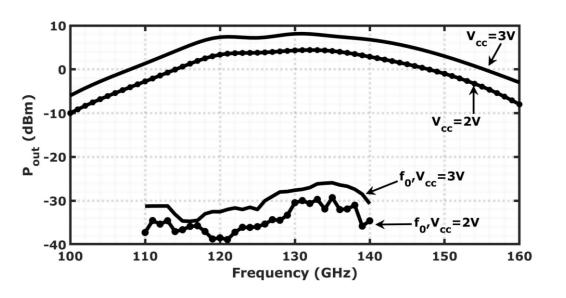

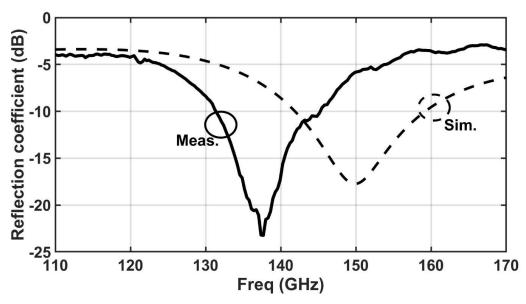

| Figure 2.9. Measured and simulated output power of the tripler breakout chip sho                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | owing the 3rd  |

| harmonic, f0, and f5 leakage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32             |

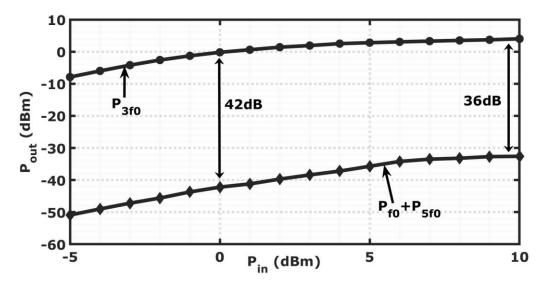

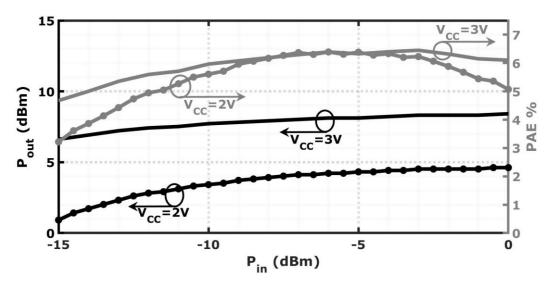

| Figure 2.10. Measured output power of the tripler breakout chip showing 3rd h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | narmonic and   |

| HRR versus input power at f <sub>0</sub> =12.5GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32             |

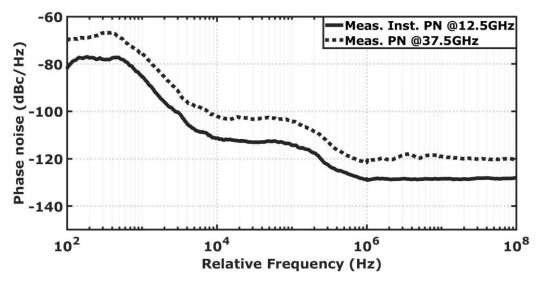

| Figure 2.11. Phase noise performance of the tripler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33             |

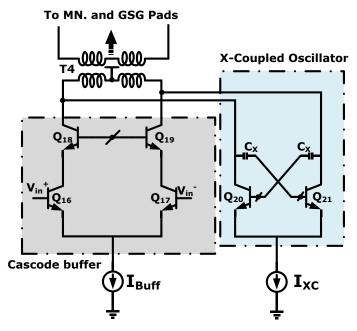

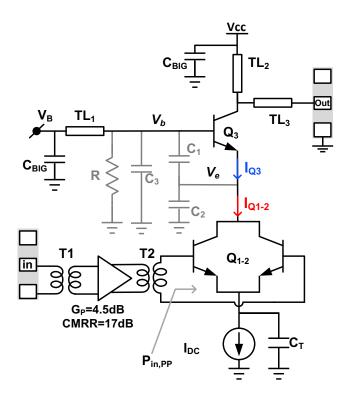

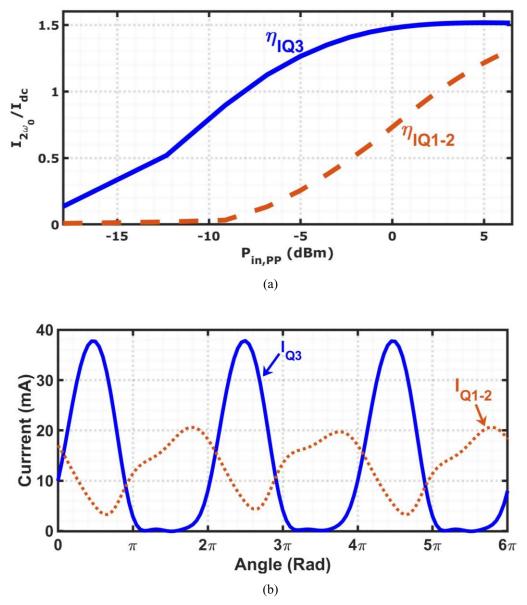

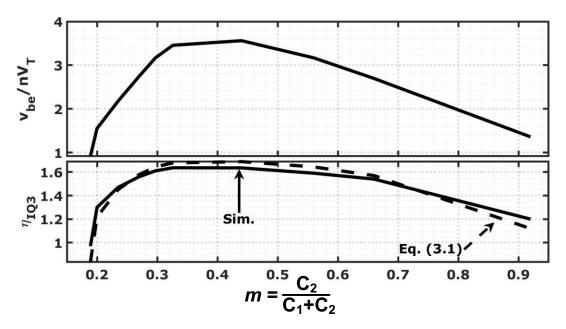

| Figure 2.12. Proposed E-band frequency doubler with differential operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34             |

| Figure 2.13. Output injection buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35             |

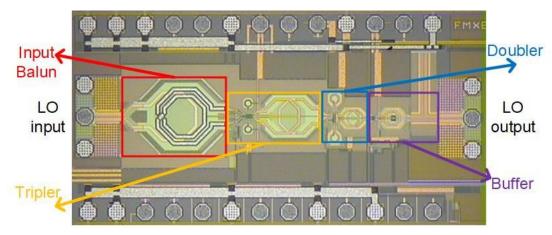

| Figure 2.14. Microphotograph of the sextupler chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36             |

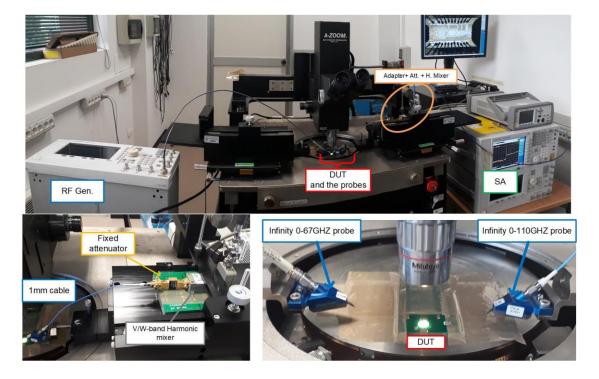

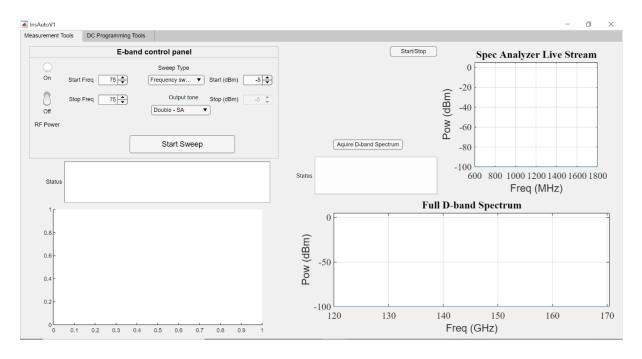

| Figure 2.15 Measurement setup for the sextupler test chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36             |

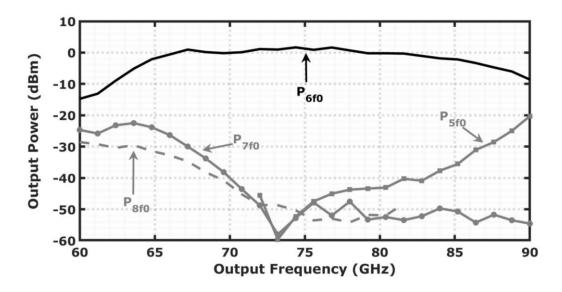

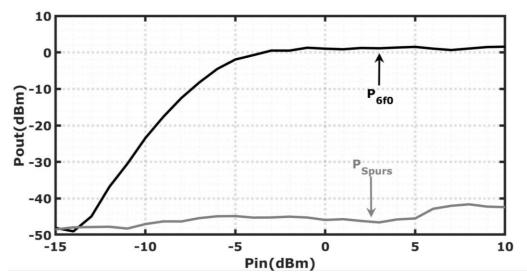

| Figure 2.16. Measured output power of the 6th harmonic and the largest spurious tones vers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

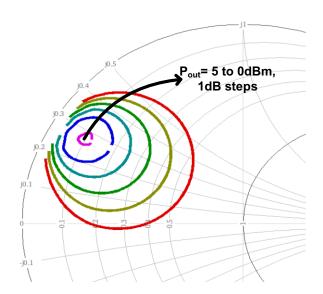

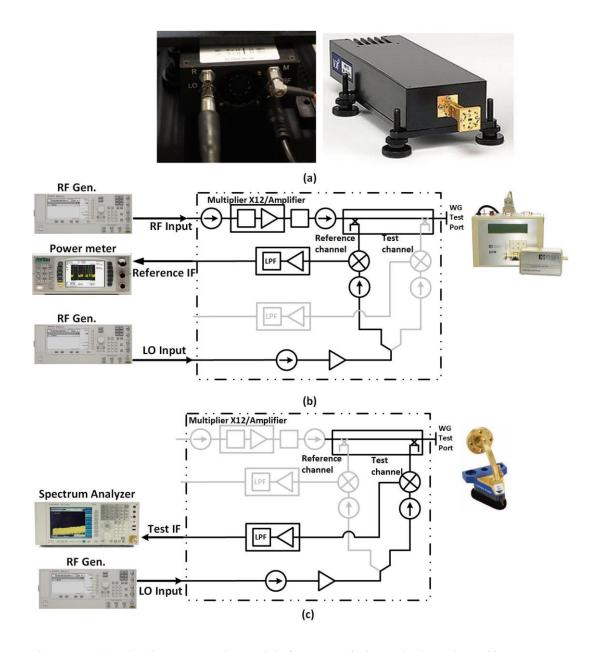

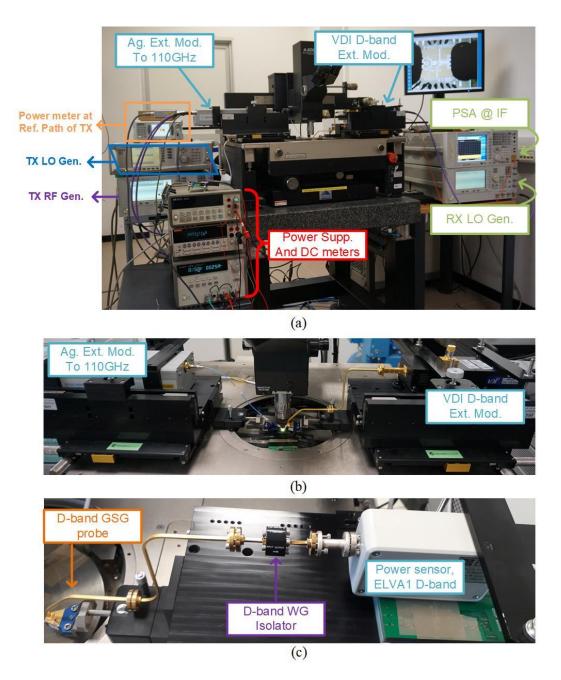

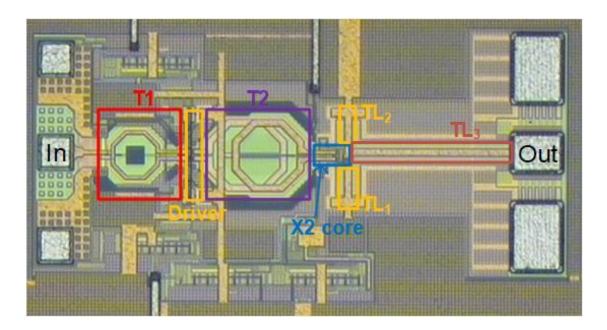

| frequency for 0dBm input signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |